Декодер сверточного кода

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

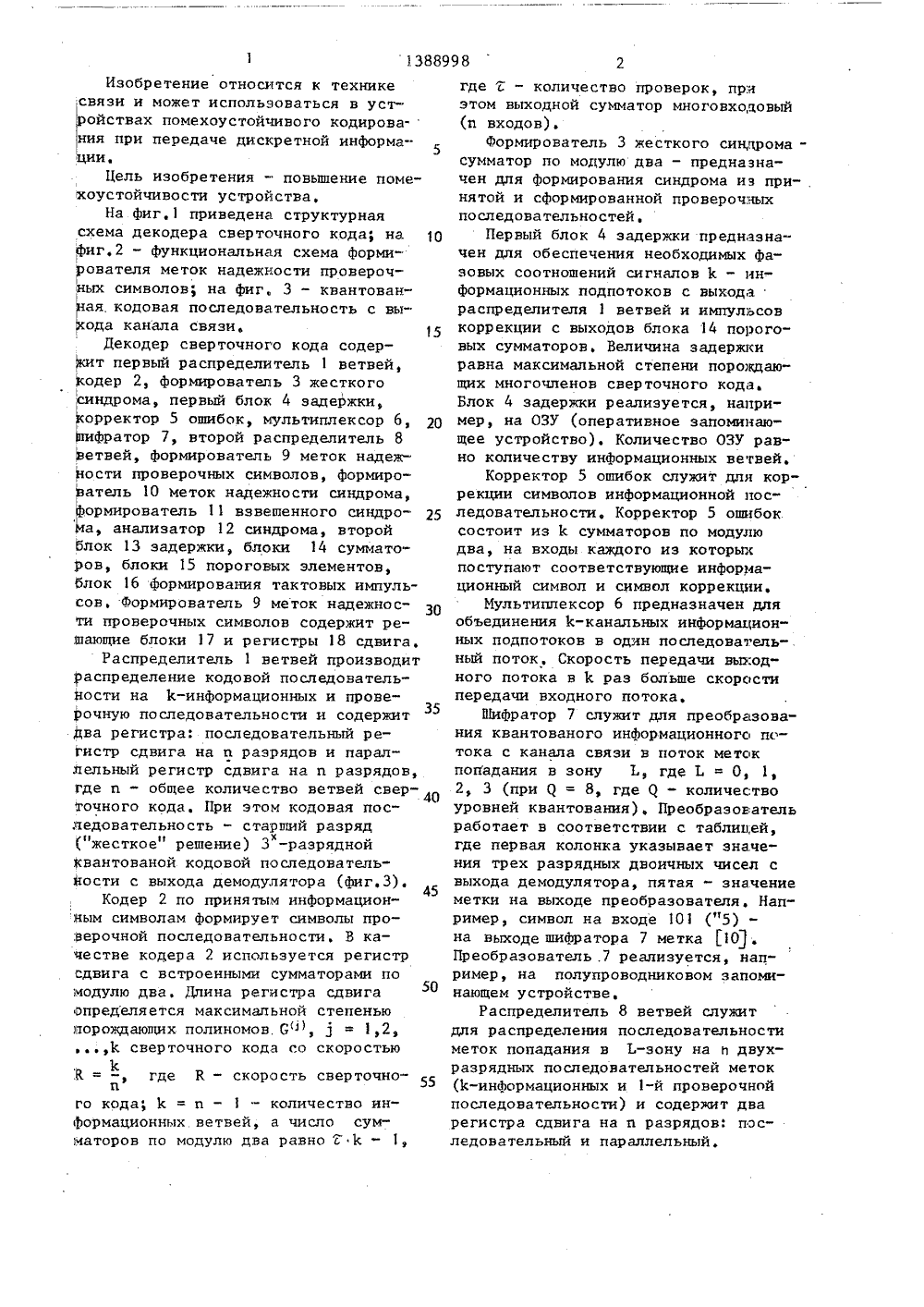

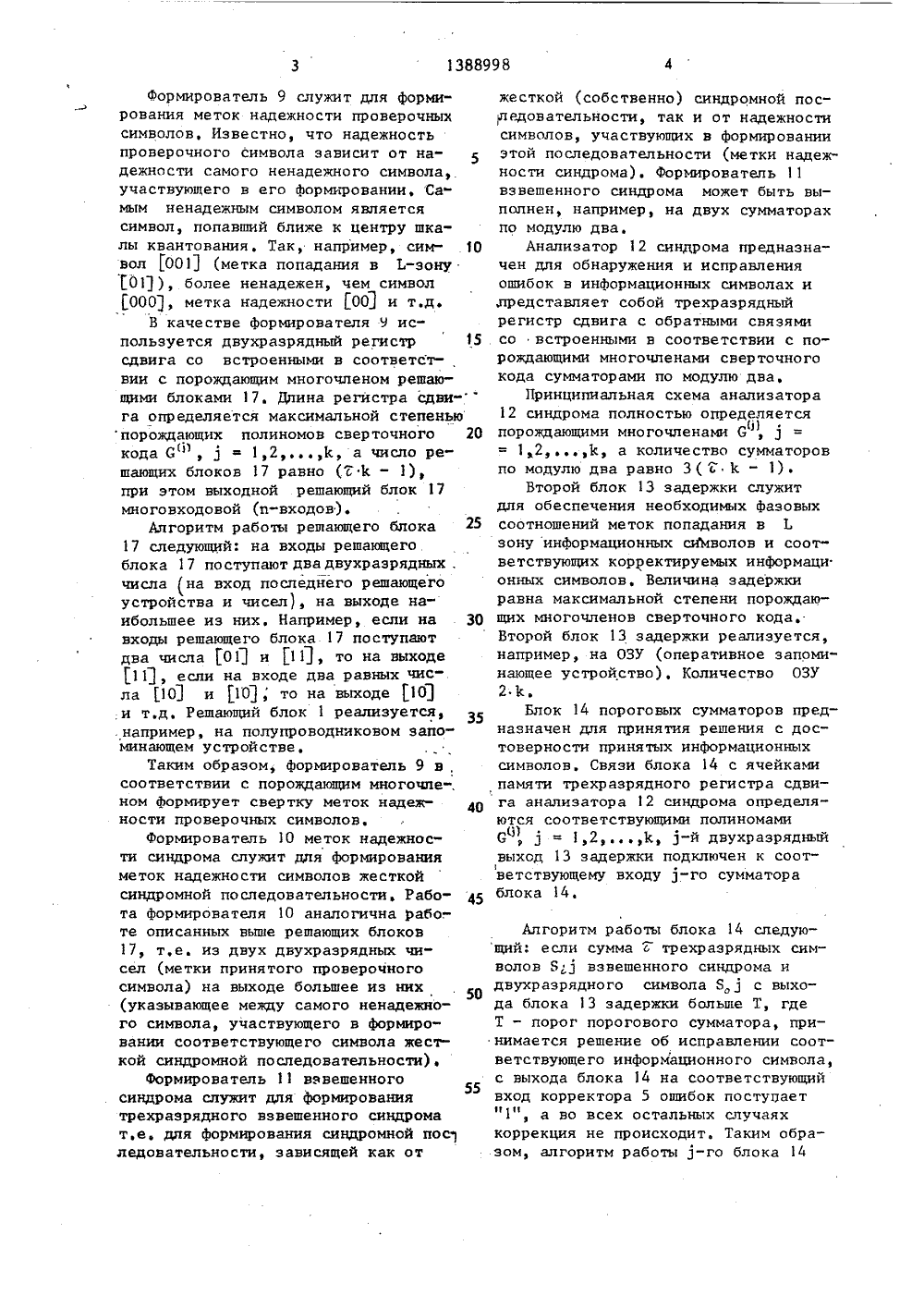

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНРЕСПУБЛИН 9) 01) М 130 51) ЕНИЯ ЕЛЬСТ ОСУДАРСТВЕННЫЙ НОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ К АВТОРСНОМУ СВ(71) Одесский электротехнический институт связи им, А.С.Попова (72) В.Л.Банкет и А.З.Геер (53) 621.394,14 (088,8)(56) Авторское свидетельство СССР У 108654, кл. Н 03 М 13/12, 1985,Авторское свидетельство СССР Вф 1320904, кл. Н 03 М 13/12, 1985. (54) ДЕКОДЕР СВЕРТОЧНОГО КОДА (57) Изобретение относится к технике связи и может использоваться для обеспечения помехоустойчивого кодирования при передаче дискретной информации. Цель изобретения - повышение помехоустойчивости устройства Декодер сверточного кода содержит первый 1 и второй 8 распределителиветвей, кодер 2, формирователь 3жесткого синдрома, первый 4 и второй13 блоки задержки, корректор 5 оши"бок, мультиплексор 6, шифратор 7,формирователь 9 меток надежностипроверочных символов, формирователь10 меток надежности синдрома, формирователь 11 взвешенного синдрома,анализатор 12 синдрома, блоки 14сумматоров, блоки 15 пороговых элементов. Использование декодерасверточного кода с мягким алгоритмом решения позволяет повысить помехоустойчивость при фиксированномобъеме оборудования и особенно эффективно для декодирования длинных(с большой длиной кодового ограничения) высокоскоростных кодов. 3 ил.Изобретение относится к технике связи и может использоваться в устройствах помехоустойчивого кодирова.ния при передаче дискретной информа 5Цель изобретения - повьппение помехоустойчивости устройства.На фиг,1 приведена структурная схема декодера сверточного кода; на. Фиг.2 - функциональная схема формирователя меток надежности проверочных символов; на фиг, 3 - квантоваяая кодовая последовательность с выода канала связи. 15Декодер сверточного кода содер 1 кит первый распределитель 1 ветвей, содер 2, формирователь 3 жесткого синдрома, первый блок 4 задеРжки, корректор 5 ошибок, мультиплексор 6, 20 1 пифратор 7, второй распределитель 8 ветвей, формирователь 9 меток надежности проверочных символов, формиропатель 10 меток надежности синдрома, формирователь 11 взвешенного синдро 1 юа, анализатор 12 синдрома, второй блок 13 задержки, блоки 14 сумматоров, блоки 15 пороговых элементов, блок 16 формирования тактовых импульсов, Формирователь 9 меток надежности проверочных символов содержит решающие блоки 17 и регистры 18 сдвига,Распределитель 1 ветвей производит распределение кодовой последовательности на Е-информационных и проверочную последовательности и содержит два регистра: последовательный реГистр сдвига на и разрядов и параллельный регистр сдвига на и разрядов, Где и - общее количество ветвей свер 40 точного кода. При этом кодовая последовательность - старший разряд(" жесткое" решение) 3 -разрядной Квантованой кодовой последовательности с выхода демодупятора (Фиг,3).45Кодер 2 по принятым информационНым символам формирует символы проверочной последовательности. В качестве кодера 2 используется регистр сдвига с встроенными сумматорами по модулю два, Длина регистра сдвига ьпределяется максимальной степенью порождающих полиномов. С 11, 3 = 1,2,сверточного кода со скоростью1 с К = - где К - скорость сверточнои 55 Го кода; 1 с = и - 1 - количество информационных. ветвей, а число сумматоров по модулю два равно Г1 - 1,где- количество проверок, приэтом выходной сумматор многовходовый(и входов).Формирователь 3 жесткого синдромасумматор по модулю два - предназначен для Формирования синдрома из принятой и сформированной проверочныхпоследовательностей,Первый блок 4 задержки предназначен для обеспечения необходимых фазовых соотношений сигналов Е - информационных подпотоков с выхода .распределителя 1 ветвей и импульсовкоррекции с выходов блока 14 пороговых сумматоров, Величина задержкиравна максимальной степени порождающих многочленов сверточного кода.Блок 4 задержки реализуется, например, на ОЗУ (оперативное запоминающее устройство), Количество ОЗУ равно количеству информационных ветвей.Корректор 5 ошибок служит для коррекции символов информационной последовательности. Корректор 5 ошибоксостоит из Е сумматоров по модулюдва, на входы каждого из которыхпоступают соответствующие информационный символ и символ коррекции.Мультиплексор 6 предназначен дляобъединения Ы-канальных информационных подпотоков в один последовательный поток, Скорость передачи выходного потока в 1 раз больше скоростипередачи входного потока.Шифратор 7 служит для преобразования квантованого информационного потока с канала связи в поток метокпопадания в зону Ь, где Ь = О, 1,2, 3 (при Я = 8, где Я - количествоуровней квантования), Преобразовательработает в соответствии с таблицей,где первая колонка указывает значения трех разрядных двоичных чисел свыхода демодулятора, пятая - значениеметки на выходе преобразователя, Нап"ример, символ на входе 101 ("5) -на выходе шифратора 7 метка 1101.Преобразователь .7 реализуется, например, на полупроводниковом запоминающем устройстве,Распределитель 8 ветвей служитдля распределения последовательностиметок попадания в Ь-зону на и двухразрядных последовательностей метокВ-информационных и 1-й проверочнойпоследовательности) и содержит дварегистра сдвига на и разрядов: последовательный и параллельный,Формирователь 9 служит для формирования меток надежности проверочныхсимволов, Известно, что надежностьпроверочного символа зависит от надежности самого ненадежного символа,.участвующего в его формировании, Самым ненадежным символом являетсясимвол, попавший ближе к центру шкалы квантования. Так, например, символ 0013 (метка попадания в 1-зонуОЦ ), более ненадежен, чем символ000, метка надежности 1001 и т.д.В качестве формирователя 9 используется двухразрядный регистр 15сдвига со встроенными в соответствии с порождающим многочленом решающими блоками 17, Длина регистра сдви-"га определяется максимальной степеньюпорождающих полиномов сверточного 20кода С", 1 = 1,21 с, а число решающих блоков 17 равно (7 К - 1),при этом выходной решающий блок 17многовходовой (п-входов).Алгоритм работы решающего блока 2517 следующий: на входы решающего.блока 17 поступают двадвухразрядных,числа (на вход последнего решающегоустройства и чисел), на выходе наибольшее из них, Например, если на 30входы решающего блока 17 поступаютдва числа 1011 и 11, то на выходе11, если на входе два равных чис-.ла 103 и 101; то на выходе 10).например на полупроводниковом запоминающем устройстве,Таким образом, формирователь 9 в,соответствии с порождающим многочпе-.ном формирует свертку меток надежности проверочных символов.Формирователь 1 О меток надежности синдрома служит для формированияметок надежности символов жесткойсиндромной последовательности. Рабата формирователя 10 аналогична рабо-.те описанных выше решающих блоков17, т,е. из двух двухразрядных чисел (метки принятого проверочногосимвола) на выходе большее из них(указывающее между самого ненадежного символа, участвующего в формировании соответствующего символа жесткой синдромной последовательности).Формирователь 11 взвешенногосиндрома служит для формированиятрехразрядиого взвешенного синдромат,е, для формирования синдромной пос 1ледовательности, зависящей как от жесткой (собственно) синдромной последовательности, так и от надежностисимволов, участвующих в формированииэтой последовательности (метки надежности синдрома). Формирователь 11взвешенного синдрома может быть выполнен, например, на двух сумматорахпо модулю два,Анализатор 12 синдрома предназначен для обнаружения и исправленияошибок в информационных символах и,представляет собой трехразрядныйрегистр сдвига с обратными связямисо встроенными в соответствии с порождающими многочленами сверточногокода сумматорами по модулю два,Принципиальная схема анализатора12 синдрома полностью определяетсяпорождающими многочленами С,О)1,2 М, а количество сумматоровпо модулю два равно 3 ( сК - 1) еВторой блок 13 задержки служитдля обеспечения необходимых фазовыхсоотношений меток попадания взону информационных сММволов и соответствующих корректируемых информаци.онных символов, Величина задержкиравна максимальной степени порождающих многочленов сверточного кода,Второй блок 13 задержки реализуется,например, на ОЗУ (оперативное запоминающее устройство), Количество ОЗУ2 1 с.Блок 14 пороговых сумматоров предназначен для принятия решения с достоверности принятых информационныхсимволов. Связи блока 14 с ячейкамипамяти трехразрядного регистра сдвига анализатора 12 синдрома определяются соответствующими полиномамиС , 1 = 1,21 с, 1-й двухразрядныйОвыход 13 задержки подключен к соответствующему входу 1-го сумматораблока 14,Алгоритм работы блока 14 следующий: если сумма Г трехразрядных символов 8,1 взвешенного синдрома и двухразрядного символа Я, 1 с выхода блока 13 задержки больше Т, где Т - порог порогового сумматора, принимается решение об исправлении соответствующего информационного символа, с выхода блока 14 на соответствующий вход корректора 5 ошибок поступает "1", а во всех остальных случаях коррекция не происходит. Таким образом, алгоритм работы 1-го блока 14следующий: Х Б; 1Т - на выходе блока 14 "1", и ноль в противном случае,Рассмотрим принцип работы декодера сверточного кода на примере сверточного кода с К = - = 7/8, с = 4,1 сш = 47, где ш - максимальная степеньпорождающих многочленов, С011,21 с,Принятая квантованная на О = 8уровней информационная последователь-,ность поступает на шифратор 7, приэтом старший разряд (жесткое решение)поступает на распределитель 1, с выхода которого символы 1 с = 7 информационных подпотоков одновременно поступают на входы соответствующих линий задержки первого блока 4 задержки и на входы кодера 2. С выхода первого блока 4 задержки задержанныеинформационные символы поступают напервые входы корректора 5.25В кодере 2 иэ принятых информационных символов формируются символыпроверочной последовательности, которые поступают на первый вход Формирователя 3 жесткого синдрома, навторой вход которого поступают символы приянтой проверочной последо,вательности, Формируется жесткийсиндром, структура которого зависитот типа ошибок как в информационныхтак и в проверочных символах.35При использовании гибкого решенияалгоритм порогового декодированияможно представить ввиде(1-2 А;) И, + Я с О , (1)1:где 1 А; - система из , ортогональных проверок;Ч; - весовой коэффициент проверки А;1Ю - весовой коэффициент иноФормационного символа,для которого осуществляется проверка.При этом надежность каждой проверки(коэффициент М,) информационногосимвола (весовой коэффициент И )определяется надежностью наименеенадежного символа, участвующего вформировании данной проверки, 55Надежность символа зависит от зоны квантования, в которую попал данный символ, Для ( = 8 таблица коэффициентов надежности показана на фиг,3 (первая и вторая колонки).Например, если символ 0101(зона квантователя "2"), то М; = 0111("3") и т,д,Удобно преобразовать (1), Для это" го умножим левую и правую часть (1) на -1 и прибавим число (7 +1) И, где 11- максимальный весовой коэффициент;;Г Я;ТоИз таблицы следует: старший разряд взвешенного синдрома Б; совпадает с жестким синдромом А , остальные раз-. ряды совпадают с меткой надежности синдрома (колонка 5), если А;=О, и совпадают с инверсией меток надежнос ти синдрома, если А; = 1.Одновременно с Формированием жесткого синдрома производится формирование коэффициентов надежности синдрома следующим образом: принятая трехразрядная последовательность символов с канала связи поступает на вход шифратора 7, с выхода которого двухразрядный поток меток,указывающих зону, в которую попали длинные символы, поступает на распределитель 8 ветвей, с выхода которого 1 с потоков меток поступает на формирователь 9 меток надежности провероч- ных символов, который производи 1 свертку меток в соответствии с порождающими многочленами сверточного кода, Сформированная последовательность меток надежности проверочных символов поступает на первый вход формирователя 10 меток надежностисиндрома, на второй вход которогопоступает последовательность метокпопадания в зону канальных проверочных символов, Сформированная в соответствии с таблицей двухразряднаяпоследовательность меток надежностисиндрома поступает на второй входформироватейя 11 взвешенного синдрома, на первый вход которого поступа Оет жесткий синдром, формируетсявзвешенная синдромная последовательность Я;, структура которой зависиткак от типа ошибок в информационныхи проверочных символах, так и от надежности этих символов. При этом,метки попадания в зону Ь информационных символов поступают на второйблок 13 задержки, с выхода которогозадержанные на ш бит метки поступают в блок 14.Необходимо отметить, что меткипопадания в Ь зону на выходе блоказадержки совпадают с Яо 1, так какв формировании Яо участвует лишь 25одна метка, указывающая в какуюиз симметричных зон надежности попалконтролируемый 1-м пороговым сумматором информационный бит,Сформированный взвешенный синдром поступает на вход анализатора 12синдрома, На каждом такте производится анализ пороговыми сумматорамиструктуры взвешенной синдромной последовательности Я, и принятие решения о достоверности первого блокаиз 1 информационных символов, Решение о достоверности информационногобита: еслиЕ+ 1 4+1 40Я 1- -- 11 = - -7=152 Йх 2 то принимается решение, что информационный символ принят с ошибкой, с выхода блока 14 на соответствующий 45 вход корректора 5 ошибок, на первый вход которого поступает соответствующий информационный символ, и соответствующие сумматоры по модулю два анализатора 12 синдрома поступает импульс коррекции, соответствуюшие Я; инвертируются. Например, Я; - 101; Я; = 010. Если , Я с Т, то1=0коррекция не происходит. С выхода корректора 5 откорректированные информационные символы поступают на мультиплексор 6, где объединяются в один информационный поток,Формула изобретенияДекодер сверточного кода, содержащий кодер, выход которого подключен к первому входу формирователя жесткого синдрома, блок формирования тактовых импульсов, первые выходы которого подключены к первым входам мультиплексора, анализатор синдрома, первый блок задержки, корректор ошибок, блок пороговых элементов, о т л и ч а ю щ и й с я тем, что, с целью повышения помехоустойчивости декодера, в него введены второй блок задержки, блок сумматоров, формирователь взвешенного синдрома, формирователь меток надежности синдрома, формирователь меток надежности проверочных символов, первый и второй распределители и шифратор, вход которого объединен с первым входом первого распределителя и является входом декодера, выход шифратора соединен с первым входом второго распределителя, второй и третий входы которого объединены с одноименными входами первого распределителя и подключены к одноименным выходам блока формирования тактовых импульсов, первые выходы первого распределителя подключены к соответствующим входам кодера и первого блока задержки, выходы которого подключены к первым входам корректора ошибок, второй выход первого распределителя соединен с вторым входом Формирователя жесткого синдрома, выход которого подключен к первому входу формирователя взвешенного синдрома, первые выходы второго распределителя подключены к соответствующим входам Формирователя меток надежности проверочных символов и второго блока задержки, выходы которого подключены к первым входам соответствующих блоков сумматоров, второй выход второго распределителя подключен к первому входу Формирователя меток надежности синдрома, второй вход которого подключен к выходу Формирователя меток надежности проверочных символов, а выход соединен с вторым входом формирователя взвешенного синдрома, выход которого подключен к первому входу анализатора синдрома, выходы которого подключены к вторым входам соответствующих блоков сумматоров, выходы которых через соответствующие блоки пороговых эле"10 1388998 Метканадежности Зоны 0,7 7 0 000 00 00 1,б 0 01 2,5 0 10 3,4 3,4 00 0,7 ментов подключены к вторым входаманализатора синдрома и корректораошибок, выходы которого подключены к вторым входам мультиплексора, выход которого является выходом декодера,001 01 010 10 О 11 11 100 11 101 10 Ь 10 01

СмотретьЗаявка

4094299, 18.04.1986

ОДЕССКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. А. С. ПОПОВА

БАНКЕТ ВИКТОР ЛЕОНИДОВИЧ, ГЕЕР АЛЕКСАНДР ЭВАЛЬДОВИЧ

МПК / Метки

МПК: H03M 13/51

Метки: декодер, кода, сверточного

Опубликовано: 15.04.1988

Код ссылки

<a href="https://patents.su/6-1388998-dekoder-svertochnogo-koda.html" target="_blank" rel="follow" title="База патентов СССР">Декодер сверточного кода</a>

Предыдущий патент: Преобразователь кода системы остаточных классов в позиционный код

Следующий патент: Генератор тестовых последовательностей

Случайный патент: Устройство для сортировки изделий