Система передачи и приема цифровых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1314463

Авторы: Медведев, Сафаров, Сидельников, Сухинин

Текст

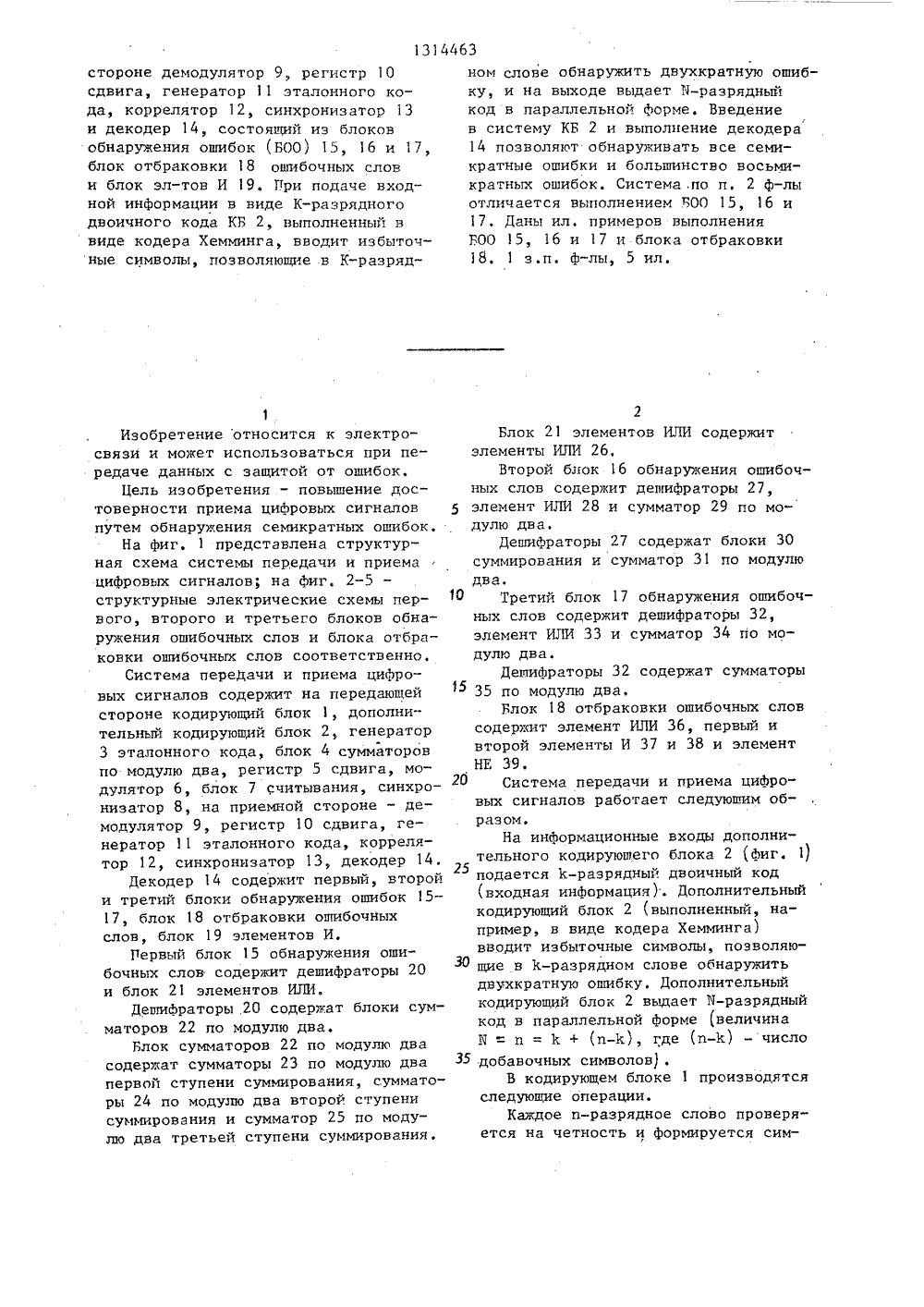

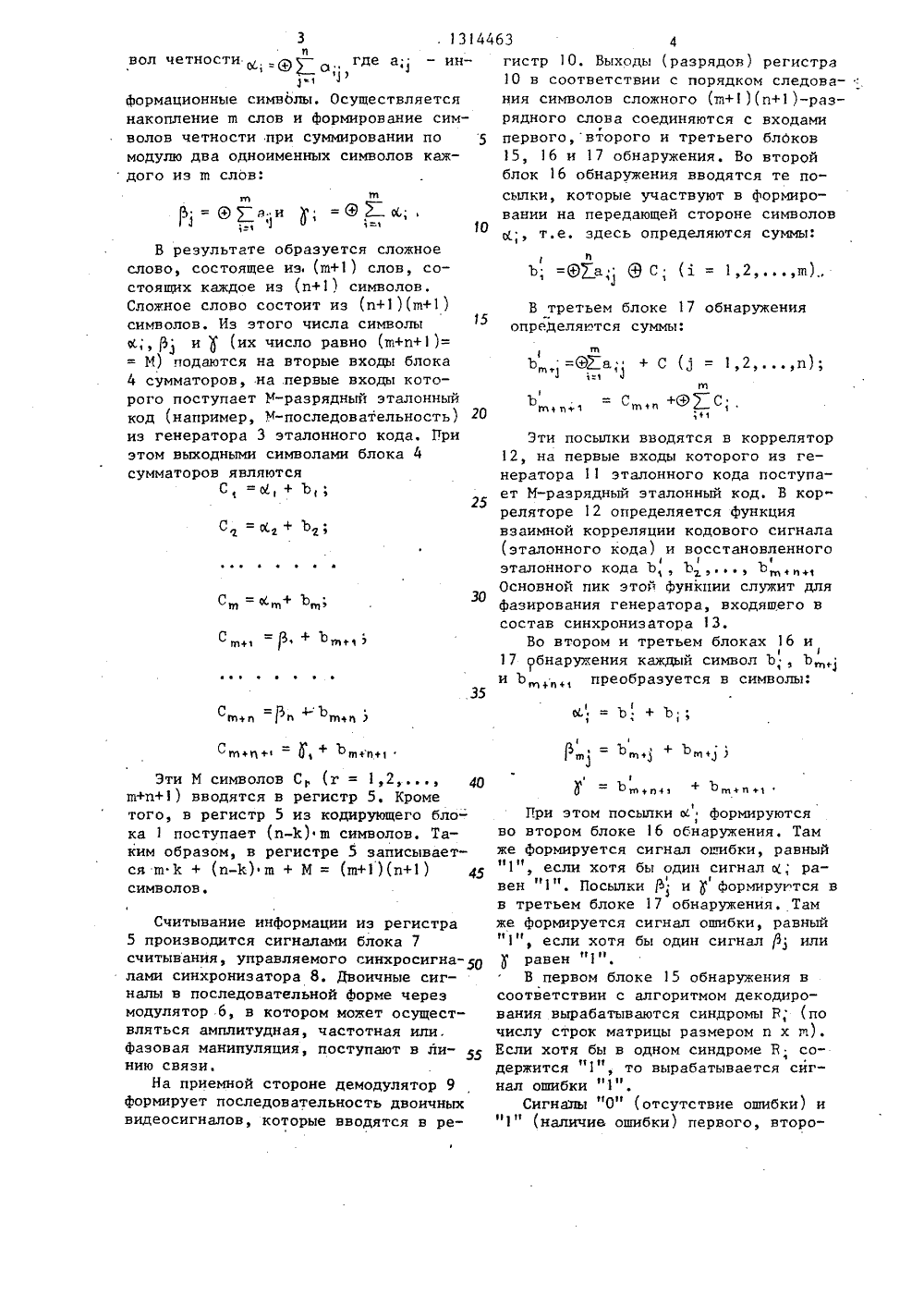

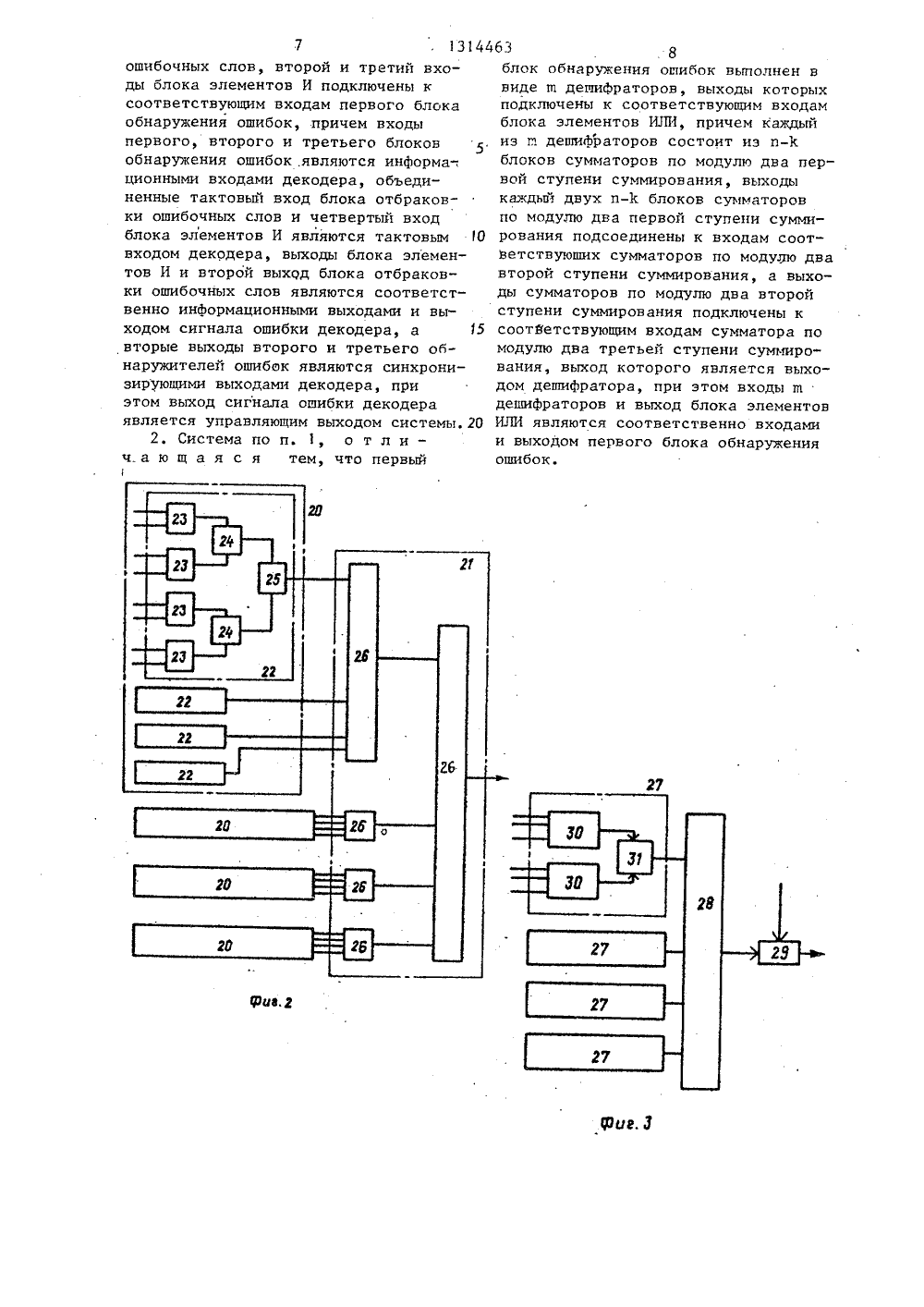

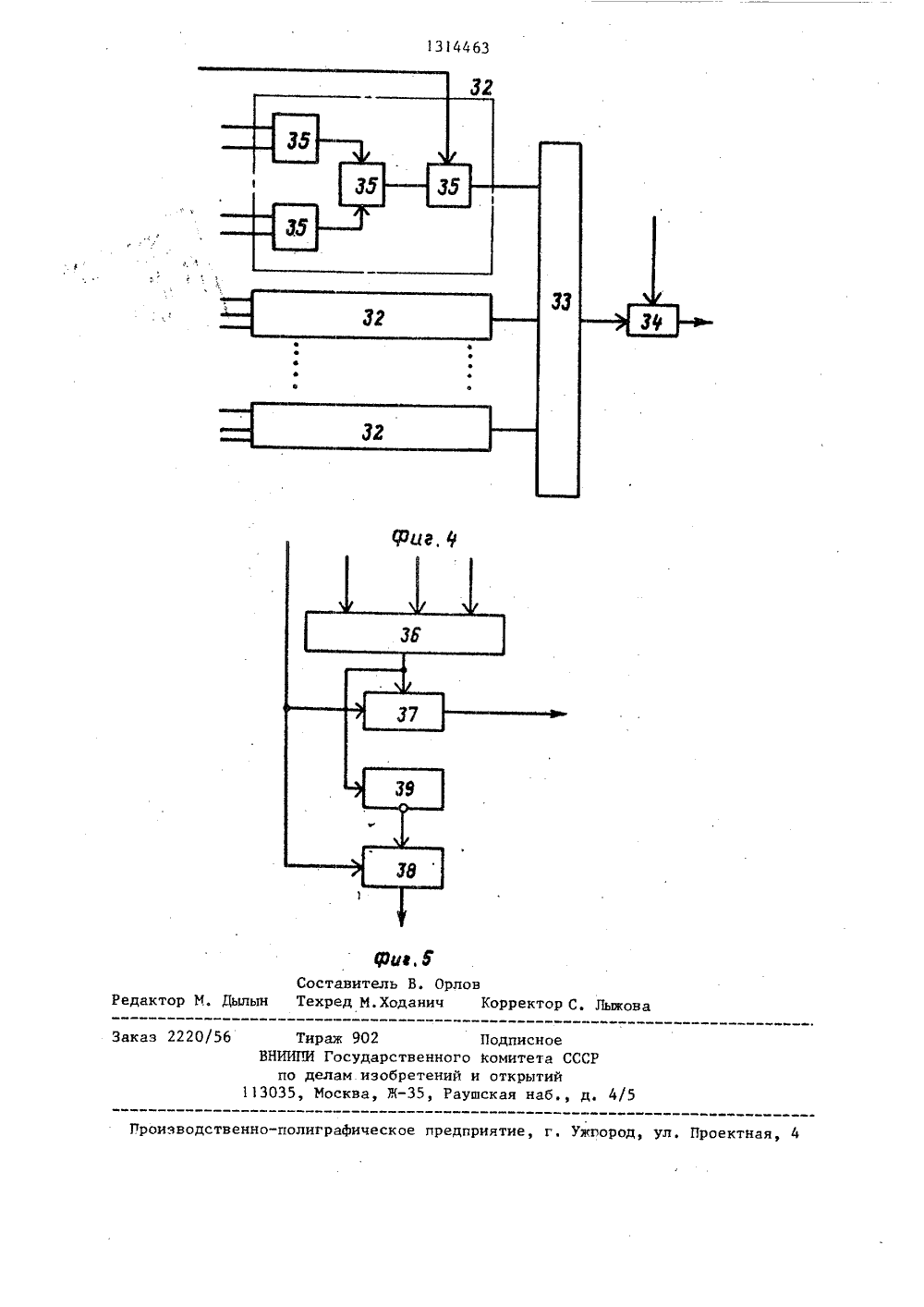

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНРЕСПУБЛИК А 1 19) Я 1314 1)4 Н 03 М 13/О ОСУДАРСТ 8 ЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ АНИЕ ИЗОБРЕТ(57) Изобретение освязи и может испоредаче данных с зЦель изобретенияверности приема цтем обнаружения сСистема содержитне кодирующие блоратор 3 эталонногторов 4 по модулю РО 2(72 ель н Осн- М. 6.8 ство С 1/10, ы техниСвязь6 9 СР 98 сдвига, модуля7 и синхрониза ков, (53) (56) ки п 1973А В О ВТОРСНОМЪГ СВИДЕТЕЛЬСТ 3860164/24-0922,02.8530.05.87. Бюл,Ленинградский элтут связи им. М Р, Т, Сафаров, Г Е. В. Медведев и 621.394.14(088.8 Рляпоберский В. редачи сообщений с. 354, 355, ри торское свидетел 1359, кл. Н 04 1 тносится к электрользоваться при пеащитои от ошибок. - повышение достоифровых сигналов пу емикратных ошибок. на передающей сторо ки (КБ) 1 и 2, гене о кода, блок суммадва, регистр 5 6, блок считывания 8, а на приемной131 стороне демодулятор 9 регистр 10 сдвига, генератор 11 эталонного кода, коррелятор 12, синхронизатор 13 и декодер 14, состоящий из блоков обнаружения ошибок (БОО) 15, 16 и 17, блок отбраковки 18 ошибочных слов и блок эл-тов И 19. При подаче входной информации в виде К-разрядного двоичного кода КБ 2, выполненный в виде кодера Хемминга, вводит избыточные символы, позволяющие в К-разряд 4463ном слове обнаружить двухкратную ошибку, и на выходе выдает И-разрядный код в параллельной форме. Введение в систему КБ 2 и выполнение декодера 14 позволяют обнаруживать все семикратные ошибки и большинство восьмикратных ошибок. Система,по и, 2 ф-лы отличается выполнением БОО 15, 16 и 17, Даны ил, примеров выполнения БОО 15, 16 и 17 и блока отбраковки 18, 1 з.п, Ф-лы, 5 ил, Изобретение относится к электросвязи и может использоваться при передаче данных с защитой от ошибок.Цель изобретения - повышение достоверности приема цифровых сигналов 5путем обнаружения семикратных ошибок.На фиг. 1 представлена структурная схема системы передачи и приемацифровых сигналов; на Фиг, 2-5структурные электрические схемы первого, второго и третьего блоков обнаружения ошибочных слов и блока отбраковки ошибочных слов соответственно,Система переДачи и приема цифровых сигналов содержит на передающейстороне кодирующий блок 1, дополнительный кодируюший блок 2, генераторЖ3 эталонного кода, блок 4 сумматоровпо модулю два, регистр 5 сдвига, модулятор 6, блок 7 считывания, синхронизатор 8, на приемной стороне - демодулятор 9, регистр 10 сдвига, генератор 11 эталонного кода, коррелятор 12, синхронизатор 13, декодер 14.Декодер 14 содержит первый, второйи третий блоки обнаружения ошибок 1517, блок 18 отбраковки ошибочныхслов, блок 19 элементов И,первый блок 15 обнаружения ошибочных слов содержит дешифраторы 20и блок 21 элементов ИЛИ,Дешифраторы 20 содержат блоки сумматоров 22 по модулю два.Блок сумматоров 22 по модулю двасодержат сумматоры 23 по модулю двапервой ступени суммирования, сумматоры 24 по модулю два второй ступенисуммирования и сумматор 25 по модулю два третьей ступени суммирования. 2Блок 21 элементов ИЛИ содержитэлементы ИЛИ 26,Второй блок 16 обнаружения ошибочных слов содержит дешифраторы 27,элемент ИЛИ 28 и сумматор 29 по модулю два,Дешифраторы 27 содержат блоки 30суммирования и сумматор 31 по модулюдва.Третий блок 17 обнаружения ошибочных слов содержит дешифраторы 32,элемент ИЛИ 33 и сумматор 34 по модулю два.Дешифраторы 32 содержат сумматоры35 по модулю два,Блок 18 отбраковки ошибочных словсодержит элемент ИЛИ 36, первый ивторой элементы И 37 и 38 и элементНЕ 39,Система передачи и приема цифровых сигналов работает следуюшим образом.На информационные входы дополнительного кодируюшего блока 2 (Фиг. 1)подается Е-разрядный двоичный код(входная информация). Дополнительныйкодирующий блок 2 (выполненный, например, в виде кодера Хемминга)вводит избыточные символы, позволяющие в К-разрядном слове обнаружитьдвухкратную ошибку. Дополнительныйкодирующий блок 2 выдает Б-разрядныйкод в параллельной форме (величинаБ = и = Х + (п-К), где (и-Е) - числодобавочных символов,В кодирующем блоке 1 производятсяследующие операции.Каждое и-разрядное слово проверяется на четность и формируется сим3 . 134463 вол четности , О с в где а - ин- г 1 1 ) 1 формационные символы. Осуществляется н накопление ш слов и Формирование сим- р волов четности при суммировании по 5 п модулю два одноименных символов каж дого из ш слов: б 3 Тс в 1=1 О4истр 10. Выходы (разрядов) регистра О в соответствии с порядком следоваия символов сложного (ш+1)(п+1)-разядного слова соединяются с входами ервого,второго и третьего блоков 5, 16 и 17 обнаружения. Во второй лок 16 обнаружения вводятся те поылки, которые участвуют в формироании на передающей стороне символов Ы , т.е. здесь определяются суммы: В третьем блоке 17 обнаруженияопределяются суммы: Эти посылки вводятся в коррелятор12, на первые входы которого из генератора 11 эталонного кода поступает И-разрядный эталонный код. В корреляторе 12 определяется Функциявзаимной корреляции кодового сигнала(эталонного кода) и восстановленного1эталонного кода Ь Ь, Ь)1,+,Основной пик этой функции служит дляфазирования генератора, входяшего всостав синхронизатора 13.Во втором и третьем блоках 16 и117 с)бнаружения каждый символ Ъ;, Ьи Ъпреобразуется в символы: 35 Сг =Ог+ Ьг Сп= + Ъ С, =(3,+Ь; В результате образуется сложное слово, состоящее из (ш+1) слов, состоящих каждое из (п+1) символов, Сложное слово состоит из (и+1)(ш+1) символов. Из этого числа символы к;,и ) (их число равно (ш+и+1)= = М) подаются на вторые входы блока 4 сумматоров, на первые входы которого поступает Р-разрядный эталонный код (например, ).-последовательность) 20 из генератора 3 эталонного кода. При этом выходными символами блока 4 сумматоров являютсяС, =о,+Ь,;Ь; =О+ а 3 С; (3. = 1,2ш) Ь, =О+а; + С ( = 1,2и);1:1Эти И символов С (г = 1,2 1 40 ш+и+1) вводятся в регистр 5. Кроме того, в регистр 5 из кодирующего бло-" ка 1 поступает (п-Х)1 ш символов. Таким образом, в регистре 5 записывается шс + (и-к)1 ш + м = (ш+1) (и+1 ) 15 символовСчитывание информации из регистра 5 производится сигналами блока 7 считывания, управляемого синхросигналами синхронизатора 8. Двоичные сигналы в последовательной Форме через модулятор 6, в котором может осуществляться амплитудная, частотная или.фазовая манипуляция, поступают в ли нию связи.На приемной стороне демодулятор 9 формирует последовательность двоичных видеосигналов, которые вводятся в ре 1Р.=Ь +Ь1 11 1=Ь+Ь1При этом посылки о формируютсяво втором блоке 16 обнаружения, Тамже Формируется сигнал ошибки, равный"1") если хотя бы один сигнал О; равен "1". Посылки Р иформиругтся вв третьем блоке 17 обнаружения. Тамже Формируется сигнал ошибки, равный"1", если хотя бы один сигналилиравен "1",В первом блоке 15 обнаружения всоответствии с алгоритмом декодирования вырабатываются синдромы Р; (почислу строк матрицы размером и х ш).Если хотя бы в одном синдроме В содержится "1", то вырабатывается сигнал ошибки "1",Сигналы "О" (отсутствие ошибки) и"1" (наличие ошибки) первого, второ 5 31446 го и третьего блоков 15-17 обнаружения вводятся в блок 18 отбраковки (фиг. 5), который осуществляет отбраковку ошибочных слов размером (т+1) (и+1). Управляющий сигнал с второго выхода блока 18 отбраковки поступает в блок 19 элементов И. На входы каждого элемента И блока 19 элементов И, число которых равно Кш, подаются из регистра 10 информационные посылки, 10 из синхронизатора 13 - синхроимпульсы а из блока 18 отбраковки - сигналы наличия или отсутствия ошибок, При отсутствии ошибки при совпадении управляющего сигнала блока 18 отбраковки и синхроимпульса производится считывание К ш-разрядного кода на выход системы передачи и приема цифровых сигналов, после чего регистр 10 переводится в состояние "0.Первый блок обнаружения (фиг. 2) состоит (применительно к коду Хемминга (15, 11) и ш = 4) из четырех дешифраторов 20, каждый из которых сначала вычисляет синдром В 1, затем25 производится проверка наличия символов "1" в синдромах. Эту функцию выполняет блок 21 элементов ИЛИ. Каждый дешифратор 20 содержит по четыре блока сумматоров 22, в которых определяются символы, образующие синдром,Второй блок 1 б обнаружения (фиг. 3) для ш = 4 содержит четыре дешифратора 27, в которых определяются коэффициенты ж , а затем произво дится проверка этих коэффициентов и формирование сигнала ошибки.Третий блок 17 обнаружения (фиг. 4) для и = 15 содержит 16 дешифраторов 32, каждый иэ которых со- ф стоит из четырех сумматоров 35, элемента ИЛИ 33 и сумматора 34, на выхо" де которого появляется сигнал "1", если произошла ошибка по столбцам матрицы.Предлагаемая система передачи и приема цифровых сигналов позволяет обнаруживать все 7-кратные и большинство 8-кратных ошибок за исключением ошибок 8-й кратности при искажении в двух словах (в строках матрицы), в которых искажены по четыре одноименных символа.Формула изобретенияСистема передачи и приема цифровых сигналов, содержащая на переда 3 6ющей стороне последовательно соединенные генератор эталонного кода, блок сумматоров по модулю два, регистрсдвига и модулятор, последовательносоединенные синхронизатор и блок считывания, а также кодирующий блок, тактовый вход которого объединен с входом генератора эталонного кода и подключен к выходу синхронизатора, а выход блока считывания подсоединен .к тактовому входу модулятора, на приемной стороне последовательно соединенные коррелятор, синхронизатор и генератор эталонного кода, последовательно соединенные демодулятор и регистр сдвига, а также декодер, информационные входы которого подключены к соответствующим выходам регистра сдвига, объединенные тактовые входы регистра сдви га, демодулятора и декодера подключены к,выходу синхронизатора, первые ивторые входы коррелятора подключенысоответственно к выходам генератораэталонного кода и синхронизирующимвыходам декодера, причем информационные выходы декодера являются информационными выходами системы, а выход модулятора и вход демодулятора являются соответственно канальньйя выходом и входом системы, о т л и ч а -ю щ а я с я тем, что, с целью повышения достоверности приема цифровых сигналов путем обнаружения семикратных ошибок, на передающей стороне введен дополнительный кодирующий блок, при этом тактовый вход дополнительного кодирующего блока подключен к выходу синхронизатора, выходы дополнительного кодирующего блока подсоединены к соответствующим вторым входам регистра сдвига и входам кодирующего блока, выходы которого подсоединены к соответствующим вто" рым входам блока сумматоров по модулю два, причем информационные входы дополнительного кодирующего блока объединены с соответствующими третьими входами регистра сдвига и являются входами системы, на приемной стороне декодер содержит последовательно соединенные первый блок обнаружения ошибок, блок отбраковки ошибочных слов и блок элементов И, атакже второй и третий блоки обнаружения ошибок, первые выходы которых подсоединены соответственно к второму и третьему входам блока отбраковки13144 ошибочных слов, второй и третий входы блока элементов И подключены к соответствующим входам первого блока обнаружения ошибок, причем входы первого, второго и третьего блоков обнаружения ошибок, являются информационными входами декодера, объединенные тактовый вход блока отбраковки ошибочных слов и четвертый вход блока элементов И являются тактовым 10 входом декодера, выходы блока элементов И и второй выход блока отбраковки ошибочных слов являются соответственно информационными выходами и выходом сигнала ошибки декодера, а 5 вторые выходы второго и третьего обнаружителей ошибок являются синхронизирующими выходами декодера, при этом выход сигнала ошибки декодера является управляющим выходом системы. 202. Система по п. 1, о т л и - ч.а ю щ а я с я тем, что первый 63 8блок обнаружения ошибок выполнен ввиде ш денифраторов, выходы которыхподключены к соответствующим входамблока элементов ИЛИ, причем каждыйиз ш дешифраторов состоит иэ и-Хблоков сумматоров по модулю два первой ступени суммирования, выходыкаждый двух и-К блоков сумматоровпо модулю два первой ступени суммирования подсоединены к входам соотВетствуюших сумматоров по модуЛю двавторой ступени суммирования, а выходы сумматоров по модулю два второйступени суммирования подключены ксоответствующим входам сумматора помодулю два третьей ступени суммирования, выход которого является выходом дешифратора, при этом входы шдешифраторов и выход блока элементовИЛИ являются соответственно входамии выходом первого блока обнаруженияошибок.1314463 Соста Техре Лыжо оррек тор М. Дыл аказ 2220/5 Тираж 902 Подписное ИИТЯ Государственного комитетам изобретений и открытий ква, Ж, Раушская наб. В по дела 3035, Мос

СмотретьЗаявка

3860164, 22.02.1985

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

САФАРОВ РИЗА ТАДЖИЕВИЧ, СИДЕЛЬНИКОВ ГЕННАДИЙ МИХАЙЛОВИЧ, МЕДВЕДЕВ ЕВГЕНИЙ ВСЕВОЛОДОВИЧ, СУХИНИН АНДРЕЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H03M 13/51

Метки: передачи, приема, сигналов, цифровых

Опубликовано: 30.05.1987

Код ссылки

<a href="https://patents.su/6-1314463-sistema-peredachi-i-priema-cifrovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи и приема цифровых сигналов</a>

Предыдущий патент: Устройство для преобразования кодов

Следующий патент: Устройство для распознавания импульсных сигналов с внутриимпульсной модуляцией

Случайный патент: Способ переработки отходов фосфорного производства