Дельта-кодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

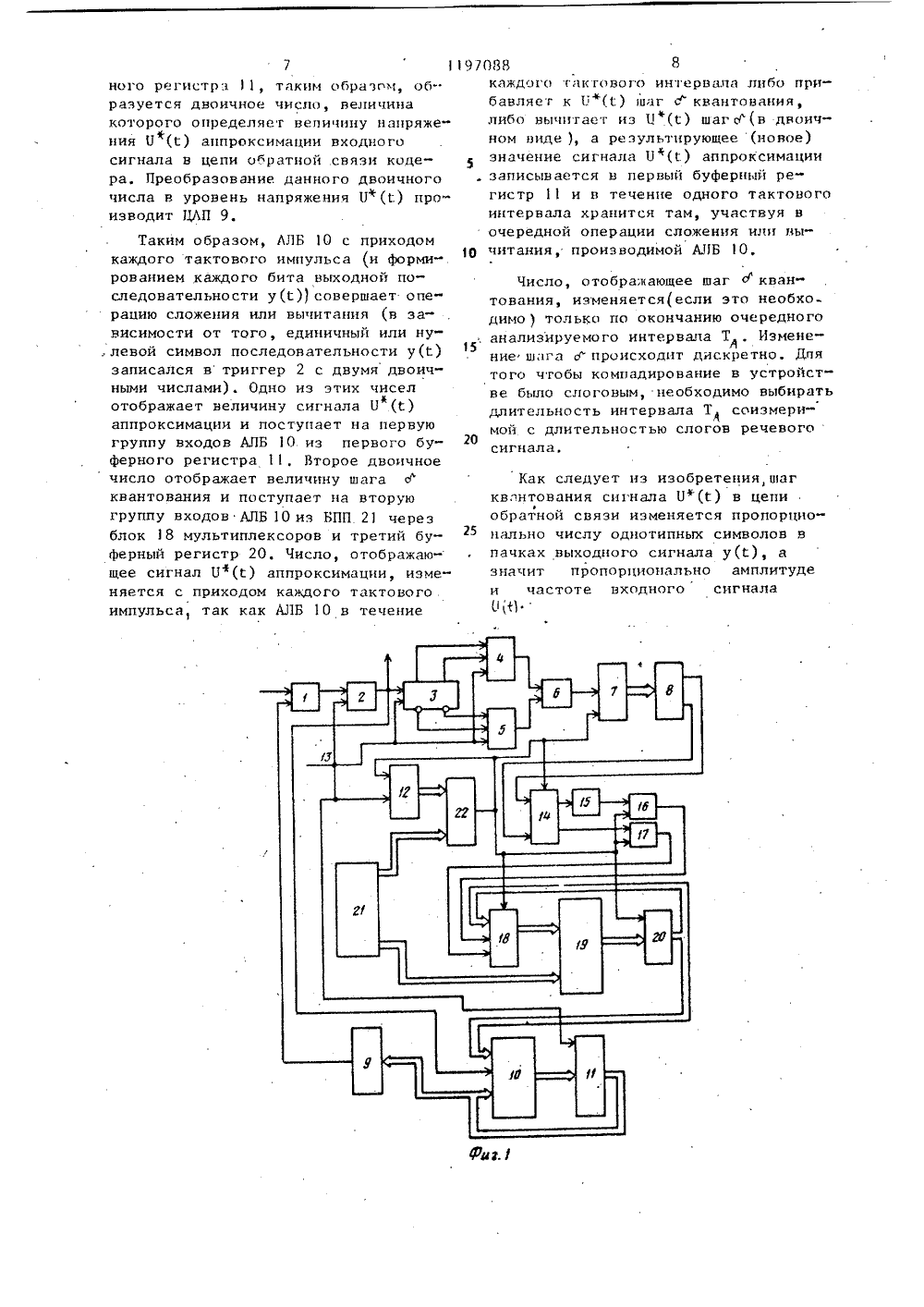

,Я 0119708 г 5114 н 03 ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ого Красий институ тович,ок ены с(71) Рижский ордена Трудонного Знамени политехническ тим. А. Я. Пельше(54)(57) ДЕЛЬТА-КОДЕР,. содержащийсоединенные последовательно компаратор, первый вход которого являетсявходом устройства, триггер и регистрсдвига, четыре элемента И, элементИЛИ, элемент эквивалентности, реверсивный счетчик, первый буферный регистр, арифметико-логический блок ицифроаналоговый преобразователь, выход которого соединен с вторым входомкомпаратора, а входы объединены ссоответствующими первыми входами арифметико-логического блока и подключенык выходам первого буферного регистра,входы которого соединены с выходамиарифметико-логического блока, управляющий вход которого подключен квыходу триггера, являющемуся выходомустройства, входы синхронизациитриггера и регистра сдвига объединены и подключены к шине синхронизации, прямые и инверсные выходы первого ивторого разрядов регистра сдвига соединены с первым и вторым входамисоотнетственно первого и второго элементов И, выходы которых подключенык элементу ИЛИ, выходы третьего ичетвертого элементов И соедин входами соответственно обратного ипрямого счета реверсивного, счетчика, . о т л и ч а ю щ и й с я тем, что, с целью повышения отношения сигнал/ шум и устранения шумов свободного . канала, в него введены первый и второй счетчики, дешифратор, второй и третий буферные регистры, элемент НЕ, блок постоянной памяти и блок мультиплексоров, управляющие. входы которого подключены к выходам реверсивного счетчика, установочные входы которого объединены с соответствующими вторыми входами арифметико-логического блока и подключены к выходам третьего буферс ного регистра, входы которого соеди- гв иены с выходами блока мультиплексоров, информационные входы которого подключены к первым выходам блока постоянной памяти, вторые выходы которого соединены с первыми входами элемента эквивалентности, вторые входы которого подключены к выходам второго счетчика, счетный вход которого объединен с входом обнуления 1 первого буферного регистра и третьи- фс, ми входами первого и второго элементов И и соединен с шиной синхрониза- (ф ции, выход элемента эквивалентности у подключен к первым входам третьего и четнертого элементов И и входам обнуления реверсивного счетчика, второго и третьего буферных регистров , Ь и первого и нторого счетчиков, счетный вход первого счетчика соединен с выходом элемента ИЛИ, а выходы ггодключены к входам дешифратор,первыйи второй выходы которого подключены к соответствующим входам нторого буферного регистра, первый выход которого1197088через элемента НЕ,а второй -непосред- соответственно третьего и четвертогоственно соединены с вторыми входами элементов И,Изобретение относится к вычислительной технике и электросвязи ипредназначено для преобразованияаналоговых сигналов в цифровую форму,Целью изобретения является повышение отношения сигнал/шум и устранение шумов свободного канала.На фиг. 1 представлена структурная схема дельта-кодера; на фиг. 2временные диаграммы, поясняющие работу дельта-кодера; на фиг, 3структурная схема блока мультиплексоров,Дельта-кодер содержит компаратор1, первый вход которого являетсявходом устройства, а выход соединенс информационным входом триггера 2,выход которого подключен к информационному входу регистра 3 сдвига.Прямые и инверсные выходы разрядоврегистра 3 сдвига подключены к первым двум входам соответственно первого и второго элементов И 4 и 5, выходы которых соединены с входамиэлемента ИЛИ 6, выход которого подключен к счетному входу первого счетчика 7 выходы которого соединены свходами дешифратора 8; второй входкомпаратора 1 подключен к выходу циф"роаналогового преобразователя (ЦАП )9, входы которого обьединены с соответствующими первыми входами арифметико-логического блока (АЛБ10 иподключены к выходам первого буферно"го регистра 11, входы которого соединены с выходами АЛБ 10, а вход обнуления совместно с счетным входомвторого счетчика 12, входами синхронизации триггера 2 и регистра 3 сдви"га и третьими входами элементов И 4и 5 подключен к лине 13 синхронизации; первый и второй выходы дешифратора В соединены с соответствующими входами второго буферного регистра 14, первый выход которого черезэлемент НЕ 15, а второй - непосредственно подключены к входам соответственно третьего и четвертого элементов И 16 и 17, выходы которых соедииены с входами соответственно обратного и прямого счета реверсивного счетчика 18, выходы последнего подключены к управляющим входам блока. 19мультиплексоров, выходы которого соединены с входами третьего буферногорегистра 20, выходы которого подключены к установочным входам реверсивного счетчика 18 и вторым входам АЛБ О 1 О, управлявший вход которого соединен с выходом триггера 2, являющимсявыходом устройства. Информационныевходы блока 19 мультиплексоров подключены к первым выходам блока 21 постоянной памяти (ГПП ), вторые выходыкоторого соединены с первыми входами элемента 22 эквивапентности, вторые входы которого подключены к.выходам второго счетчика 12, а выход в . к 2 О другим входам элементов И 16 и 17 ивходам обнуления счетчиков 7, 12 и 18и буферных регистров 14 и 20,На фиг.2 обозначено: а - последовательность синхроимпульсов с час тотой Г; б - выходной сигнал у(г.)на выходе триггера 2; в и г - сигналыа(Т), а (Т) на выходах элементов И4, 5; д - сигнал Ь на выходе элемента 6 ИЛИ; е - сигнал х(1) на выходе элемента 22 эквивалентности; жи з - сигналы С(й ), С(Т) на выходахдешифратора 8; и и к - выходные сигналы К (С), К (1) второго буферногорегистра 14.; л - сигнал Кна вы 1 35ходе элемента НЕ 15 м и и - сигналыМ (С), И(1:) на выходах элементов И16 и 17.Устройство работает следующим образом.Результаты сравнения компаратором1 входного 11(С) и аппроксимирующего+11 (1) напряжений в виде единичныхили нулевых битов записываются втриггер 2 по информационному входув моменты поступления на его входсинхронизации синхроимпульсов ГСсигналом кодера и одновременно записывается в регистр 3 сдвига по приходу очередных синхроимпульсов К наего вход синхронизации. Продвигаясьпо регистру 3 сдвига, импульсная последовательность у(й) анализируетсяэлементами И 4 и 5 и элементом ИЛИ 6,на выходе которого генерируются ко.роткие единичные импульсы Ъ(й)(и более 1 одинаковых единичных илинулевых символа, следующих подряд.Длительность единичных импульсовЪ(С) определяется длительностью синхроимпульсов Гс, что обусловленосоединением шины 13 с третьими входами элементов И 4 и 5. Производимоетаким образом укорочение импульсов. а(й), а(С) и Ь(С) необходимо для 2 Ообеспечения нормальной работы первого счетчика 7.Как известно, двух-, и более элементные пачки появляются в выходномсигнале у(й) дельта-кодера тогда, 25когда сигнал аппроксимации Пф(й) неможет "догнать" быстро изменяющийсявходной сигнал Б(й) на протяжениидвух и: более тактовых интервалов,Иаличие многоэлементных "пачек" всигнале у свидетельствует о том,что дельта-кодер работает в режимеперегрузки, что сигнал П(С) восстанавливается с большими искажениямииз-за слишком малого шага квантова 35ния Ы". Присутствие в выходном сигнале у (й) малоэлементных пачек, напротяжении длительного интервалавремени как правило, свидетельствует1.о том, что шаг квантования Ф"выбранслишком большим и восстанавливаемый сигнал У+(г,) имеет низкое отнс -шение сигнал/шум иэ-за большой мощности шумов квантования,Зная, таким образом, параметрывходного сигнала У(С), с которым дол.жен работать. дельта-кодер, .можноустановить число импульсов в последовательности Ь(С) в. течение некоторого анализируемого интервала времени Т, которое свидетельствует отом, что кодер работает в режимеперегрузки.(велика мощность шумовперегрузки и что шаг с квантованиянеобходимо увеличить. Обозначим данное число импульсов .Бмс,Кроме того, можно установить число импульсов в последовательности ЬЙ) в течение интервала времени Тлт которое свидетельствует о том, что кодер работает со слишком бэльшим шагом К квантования (а следовательно, низким отношением сигнал/шум квантования), и что шаг квантования необходимо уменьшить, Обозначим данное число импульсов ЮминОчевидно, тогда любое число импульсов Ь(г.) за время ТА между Юццн и Нбудет свидетельствовать о том, что кодер работает с оптимальным шагом д квантования, менять который по ка не следует.Функцию счета импульсов Ъ(с) на интервале Т в устройстве выполняет первый счетчик 7, на счетный вход которого поступает последовательность Ъ(г.) с выхода элемента ИЛИ 5, Периодический интервал времени Т, на котором проводится анализ выходной последовательности у(С), определяется числом, хранящимся(в двоичном коде) в БПП 21 и постоянно присутствую-. щим на второй группе выводов БПП 21, а следовательно, и на первой группе входов элемента 22 эквивалентности, Это число должно быть равно количеству тактовых импульсов синхропоследовательности Й , укладывающихся в интервал Т, Таким образом, как только второй счетчик 12, счетный вход ко. торого соединен с шиной 13, досчитает до числа, присутствующего на второй группе выводов БПП 21, так на выходе элемента 22 эквивалентности появится единичный импульс Х (фиг, 2 е), который, сбросив первый 7 и второй 12 счетчики и поступив в качестве управляющего и вспомогательного сигнала на другие узлы устройства, отметит конец предыдущего и начало следующего анализируемого интервала Т выходного сигнапа у(1) (а следовательно, и входного сигнала П(Т,Результаты счета импульсов Ь(С) первым счетчиком 7 постоянно анализируются дешифратором 8, который на первом своем выходе С (й) генерирует короткий единичный импульс в тот момент, когда первый счетчик 7 досчитает до М нн, а на втором выходе С(С) - такой же импульс, когда счетчик досчитает до Нд. Результаты анализа последовательностей у(С) и Ъ(й) (сигналы С, (С) и С 2(й в момент их появления записываются во второй буферный регистр 14 и хра 197088нятся там до окончания текущего анализируемого интервала Т, Буферныйрегистр 14 таким образом может бытьреализован в виде нескольких (в рассматриваемом примере - двух ) параллельных асинхронных КБ-триггеров.Импульс с выхода элемента 22 эквивалентности, приходящий в конце каждого интервала Т 1, стирает информацию,записанную в регистр 14, и подготавливает его таким образом к принятиюинформации в течение следующего интервала Т,Комбинация сигналов с выходов вто-,рого буферного регистра 14 поступаетчерез элементы И 1 б и 17 на счетныевходы реверсивного счетчика 18, при"чем сигнал К 1 с первого выхода, буферного регистра 14 предварительноинвертируется элементом НЕ 15 и поступает через элемент И 16 на входобратного счета реверсивного счетчика18, а сигнал К - на вход прямогосчета реверсивного счетчика 18,Таким образом, если в течение интервала Т число импульсов в послеДдовательности Ь(С) на выходе элемента ИЛИ б было меньше И , на выходе второго буферного регистра 14 сигналы К(С) = О и К (:) = О, Соответ 2ственно на входе обратного счета реверсивного счетчика 18 в момент окончания интервала Т появляется короткий единичный импульс М(1). Есличисло импульсов в последовательностиЬ(с) будет Ии И,ц , то в момент прихода очередного импульсах(Е) на обоих входах реверсивногосчетчика 18 присутствуют нули(и реверсивн й счетчик 18 не изменит своегосостояния). Если число импульсов впоследовательности Ь эа время Т 4достигло Б, или превысило его, тов момент окончания .анализируемогоинтервала Т,1 на входе прямого счетаР еверсивного счетчика 18 появляетсякороткий единичный импульс М(последняя ситуация изображена навременных диаграммах фиг, 2 ),Блок 19 мультиплексоров представляет собой несколько мультиплексоровс объединенными управляющими входамии разделенными на группы информационными входами, Одноименные входыотдельных мультиплексоров образуютгруппы входов, объединенные в магистпаль информационных шин, по которой к информационным входам блока 18 мультиплексоров: подводится набор шагов У .У квантования, с кото рыми может работать устройство и которые хранятся в БПП 21 в виде двоичных чисел. Предполагается, что дво ичное число, соответствующее д" больше, чем двоичное число, соответству О ющее д 1 и Т.Д. (б) б", 64)О б"7 с,)При поступлении короткого единичного импульса на вход прямого счетареверсивного счетчика 18, двоичноечисло на его выходах. увеличивается 15на одну единицу и на выход блока 18мультиплексоров подключается следующий (больший ) шаг б"квантования иэБПП 21, в виде двоичного числа (ком"бинации двоичных символов ), Если 20единичный импульс поступает на входобратного, счета реверсивного счетчика 18, то на выход блока 18 мультиплексоров подключается предыдущий( меньший ) шаг кв ан то в ания.25Подключенный иэ БПП 21 шаг квантования (двоичное число, соответствующее размеру шага) записывается втретий буферный регистр 20 по при хоДУ на его вход обнуления импульсах и хранится на его выходах доконца анализируемого интервала ТУстановочные входы реверсивногосчетчика 18 подключены к выходам буферного регистра 20 и, таким образом,информация о текущем шаге квантования (о его порядковом номере, а следовательно, о его размерах) в концекаждого анализируемогоинтервала .40 (по пРиходу импульса,х(с).) записывается в реверсивный счетчик 18 и слу-жит в качестве начального значенияшага Двоичное число, срответствую- .щее текущему шагу квантования, с выхода третьего буферного регистра 20поступает на вторую группу входовАЛБ 1 О и в зависимости от состоянияего управляющего входа либо суммируется либо вычитается из двоичногочисла, присутствующего на первойгруппе входов АЛБ 1 О, Двоичное число на первой. группе входов АДБ 10является результатом аналогичнойарифметической операции, произведенной в предыдущем тактовом интервале,и хранящимся в первом буферном регистре 11 в течение периода одного синхроимпульса, На выходе первого буфер7 1 ного регистра 11, таким образом, образуется двоичное число, величина которого определяет вепичину напряжения Оаппроксимации входного сигнала в цепи обратной связи кодера. Преобразование данного двоичного числа в уровень напряжения 1(1:.) производит ЦАП 9.Таким образом, АЛБ 1 О с приходом каждого тактового импульса (и форми-. рованием,каждого бита выходной последовательности у( совершает операцию сложения или вычитания (в зависимости от того, единичный или ну.,левой символ последовательности у записался втриггер 2 с двумя двоичными числами). Одно иэ этих чисел отображает величину сигнала У (С) аппроксимации и поступает на первую группу входов АЛБ 10 из первого буферного регистра 11, Второе двоичное число отображает величину шага б квантования и поступает на вторую группу входов АЛБ 10 из БПП 21 через блок 18 мультиплексоров и третий буферный регистр 20 Число, отображающее сигнал У (С) аппроксимации, изменяется с приходом каждого тактового . импульса, так как АЛБ 10 в течение 197088каждого тактового интервала либо прибавляе г к П (1:) шаг Р квантования,либо вычитает из(С) шаг с/(в двоичном виде ), а результирующее (новое)значение сигнала У(.) аппроксимации. записывается н первый буферный регистр 1 и в течение одного тактовогоинтервала хранится там, участвуя вочередной операции сложения или вычитания, производимой АЛБ 1 О,Число, отображающее шаг дквантования, изменяется(если это необхо димо ) только по окончанию очередного , анализируемого интервала Т, Изменение шага о происходит дискретно. Для того чтобы компадирование в устройстве было слоговым, необходимо выбирать длительность интервала Т соизмеримой с длительностью слогов речевого сигнала.Как следует из изобретения,шаг квантования сигнала У+(С) в цепиФобратной связи изменяется пропорционально числу однотипных символов в пачках выходного сигнала у(С), а значит пропорционально амплитуде и частоте входного сигнала О,Ц"Патент", г.Ужгород, ул.Проектная, 4 лиал Иредергидному гчеегчи гу31/59 Тираж 8 на 3 гюрз ферггом рееиотру

СмотретьЗаявка

3722916, 09.04.1984

РИЖСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. А. Я. ПЕЛЬШЕ

КОМАРОВ КОНСТАНТИН СЕРГЕЕВИЧ, КОТОВИЧ ГЛЕБ НИКОЛАЕВИЧ, ПАЛКОВ АНДРЕЙ ИМАНТОВИЧ, МАЛАШОНОК ИГОРЬ МИХАЙЛОВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-кодер

Опубликовано: 07.12.1985

Код ссылки

<a href="https://patents.su/6-1197088-delta-koder.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-кодер</a>

Предыдущий патент: Дельта-кодер

Следующий патент: Преобразователь частоты в код

Случайный патент: Способ получения гранулированного хлорида калия