Демодулятор дискретных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

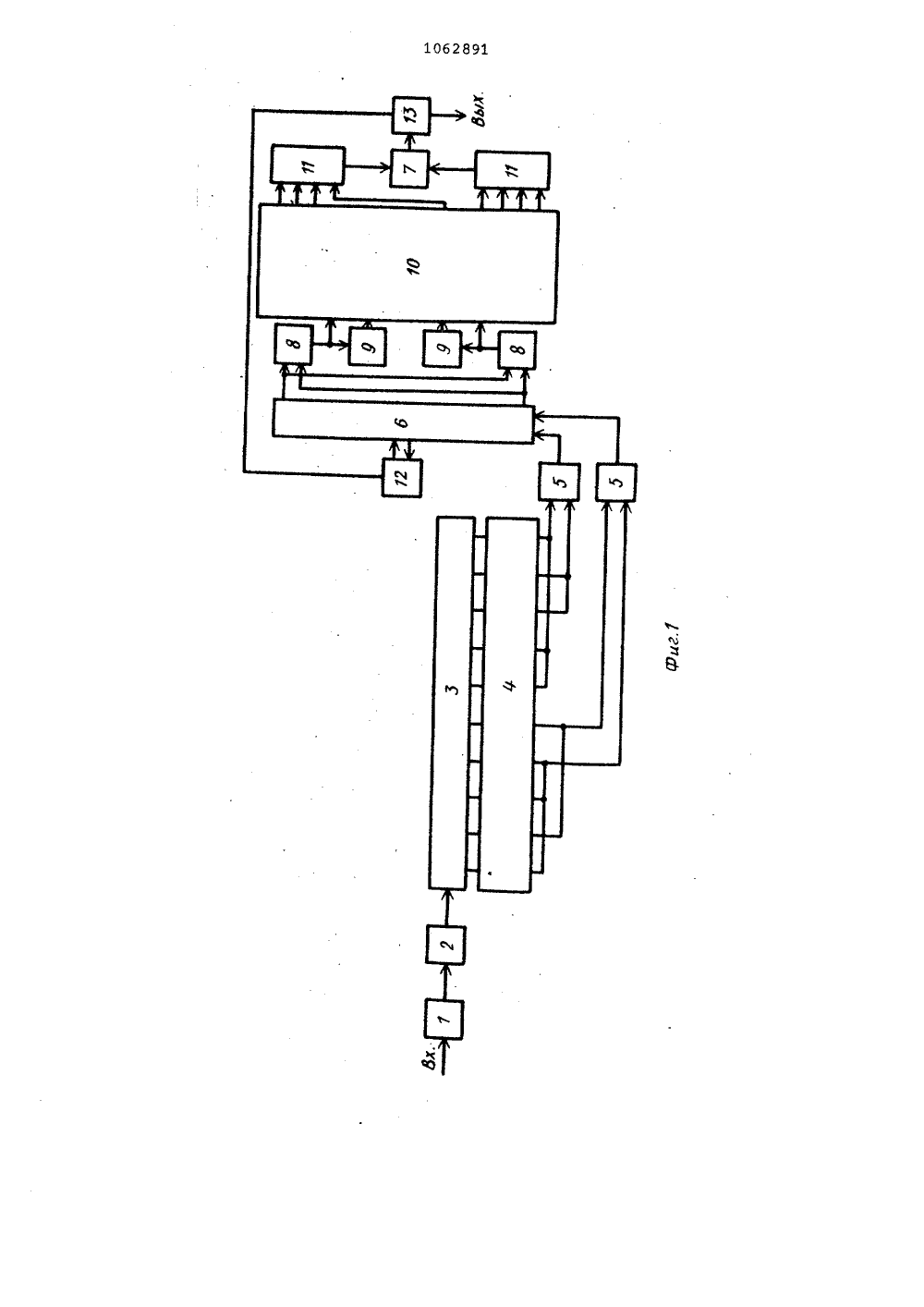

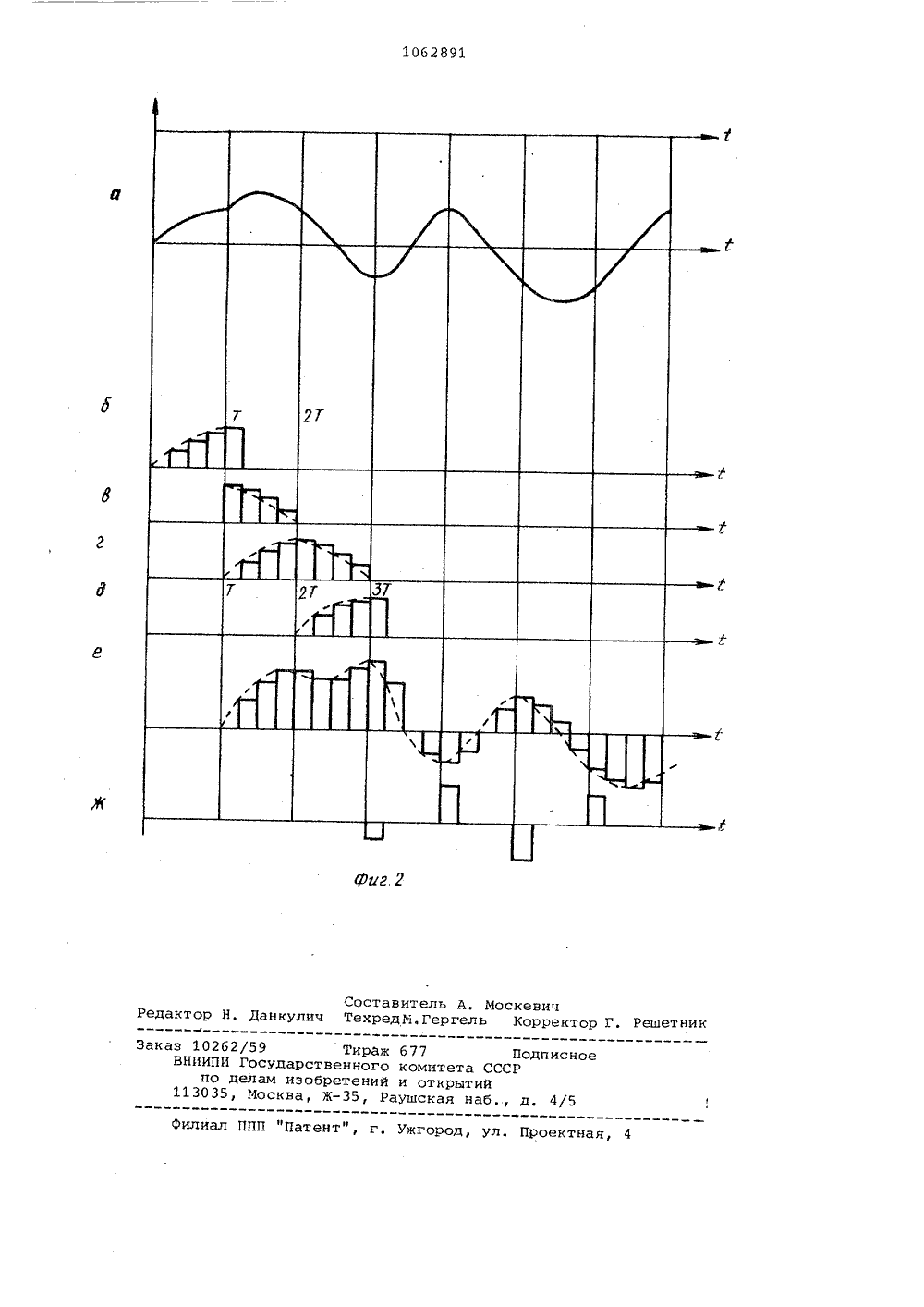

.А. Ци дена Л тво ССС а ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙОПИСАНИЕ ИЗО ТОРСКОМУ СВИДЕТЕЛЬСТ(71 ор енинаполи титут им.М,И.Калинина(56 ) 1. Авторское свидетельс РФ 468380, кл. Н 04 Э 1/02, 1973.2, Авторское свидетельство СССРР 788429, кл. Н 04 (, 27/22, 1979(54)(57) ДЕМОДУЛЯТОР ДИСКРЕТНЫХ СИГНАЛОВ, содержащий последовательносоединенные полосовой Фильтр, дискретизатор и первый элемент задержки,выходы которого подключены к входамблока взвешивания, выходы которогосоединены с входами операционных усилителей, а также первый сумматор,выход которого подключен к первомувходу решающего блока, о т л и чю щ и й с я тем, что, с целью повышения быстродействия при демодуляции сигналов с фазовой манипуляцией, введены второй сумматор, инверторы, рой элемент задержки, блок компен ции., блоки выбора максимального н пряжения и дополнительные суммато выходы которых подключены к входам соответствующих инверторов, выходы которых соединены с одними входами блока компенсации, другие входы которого соединены с выходами дополнительных сумматоров, к входам которых подключены одни выходы второго элемента задержки, входы и другие выходы которого соединены соответственно с выходами операционных усилителей и с входами второго суммато-рС ра, выход которого подключен к второму входу решающего блока, при этом выходы блока компенсации соединены с входами соответствующих бло С ков выбора максимального напряжения, выходы которых подключены к входам первого сумматора.Изобретение относится к технике связи и может использоваться для когерентной высокоскоростной обработки сигналон с фазовой манипуляцией в условиях межсимвольной интерференции.Известен оптимальный демодулятор, содержащий входные полосовые фильтры, входные ключевые элементы, блок синхронизации, линию задержки, взвешивающие блоки, промежуточные ключевые блоки и блоки выделения огибающей, причем выходы входных полосовых Фильтров подключены к входам входных ключевых элементов, которые осуществляют временную дискретизацию сигналов, при этом рабоТОй ключевых элементов управляет блок синхронизации, а сигналы с выходов входных ключевых элементов объединяются и поступают на вход линии задержки к отводам которой подключены вертикальные шины взвешивающих блоков коэффициенты передачи которых пропорциональны выборочным значениям импульсных реакций фильтров, согласованных с обрабатываемыми сигналами, причем горизонтальные шины блоков взвешивания подключены к входам промежуточных ключевых блоков, выходы которых объединены и подключаются к двум входам блоков выделения Огибаюцей 11 .Однако данный демодулятор имеет низкое быстродействие.Наиболее близким техническим рееэениегл к изобретению является демодулятор дискретных сигналов, содержаций последовательно соединенные полосовой фильтр, дискретизатор и первый элемент задержки, выходы которого подключены к входам блока взвешивания, выходы которого соединены с входами операционных усилителей, а такхе первый сумлатор, ныход которого подключен кг первому входу решающего блока 2 .Однако известный демодулятор имеет низкое быстродейстние при демодуляции сигналов с вазовой манипуляцией.Цель изобретения - повышение быстродействия при демодуляции сигналов с фазовой манипуляцией,40 50 55 Поставленная цель достигается тем, что в демодулятор дискретных сигналов, содержаций последовательнс соединенные полосовой Фильтр, дискретизатор и первый элемент задержки, выходы которого подключены к входагл блока взвешивания, выходы которого соединены с входами операционных усилителей, а также первый сумматор, выход которого подключен к первому входу решае 0 щего блока, введЕны второй 5 10 15 20 25 30 35 сумматор, инверторы, нторой элемент задержки, блок компенсации, блоки выбора максимального напряжения и дополнительные сумматоры, выходы которых подключены к входам соответствующих инверторов, выходы которых соединены с одними входагли блока компенсации, другие входы которого соединены с выходами дополнительных сумматоров, к входам которых подключены одни выходы второго элемента задержки, входы и другие выходы которого соединены соответственно с выходами операционных усилителей и с входами второго сумматора, выход которого подключен к второму входу решающего блока, при этом выходы блока компенсации соединены с входами соответствуюцих блоков выбора глаксимального напряжения, выходы которых подключены к входам первого сумматора.На фиг.1 представлена блок-схема прецлагаемого демодулятора на Фиг.2 - эпюры напряжений, поясняющие его работуДемодулятор дискретных сигналов содержит полосовой фильтр 1 цискретиэатор 2, первый элемент 3 задержки, блок 4 взвешивания, операционные усилители 5, второй элемент б задержки, первый сумматор 7, дополнительные сумматоры 8, инверторы 9, блок 10 компенсации, блоки 11 выбора максимального напряжения, второй сугеглатор 12, решаюц 1 ий блок 13.Демодулятор работает следующим образом. Непрерывный сигнал с фазовсй манипуляцией (основание алФавита гге=2 поступает через полосовой фильтр 1 на дискретизатор 2, на выходе которого Формируются последовательности импульсов с амплитудаги, пропорциональными выборочным значениям сигнала н соответствующие моменты нремениЬ=1,2,) . Эти последовательности импульсов поступают на вход первого элемента 3 задержки. Е выходам первого элеглента 3 задержки подключен блок 4 взвешивания коэффициенты передачи кОтОРОГО пропорцееональны Выборочным значениям импульсной реакции фильтра 1, согласованного с одиночным, ограниченным по спектру, сигналом с фазовой манипуляцией.Выходы блока 4 взвешивания подключены к входам операционных усилителей 5. На выходах огерационных усилителей 5 формируются две части импульсного отклика (на интервалах времени 0 с с с Т и г с с с 2 Е)ееа входное воздействие, 10 б 2891Выходы операционных усилителей5 подключаются к входам второго элемента б задержки. Запись информации в ячейки памяти второго элемента б задержки может осуцествляться либо параллельно (двухтактнаялиния), либо последовательно, тос одного входа линии, то с другого. При интервале анализа сигналаТ= 2 Т второго элемента б задержки имеется с ячеек памяти четыреотвода,К выходам средних отводов подключены соответствующий дополнительный сумматор 8 и инвертор 9, на выходе которого формируется импульсный отклик на всем интервале анализа 01 ( 2 Т, состоящий из суммыдвух частей отклика на интервалахО2 Т и Т 12 Т. При этом всевремя задержки второго элементаб задержки, составляет 2 Т (от первого отвода до среднего отвода=Т и от среднего отвода до последнего -1 =Т).К выходам крайних отводов второго элемента б задержки подключеныдругой дополнительный сумматор 8и инвертор 9, при помощи которыхформируются всевозможные комбина-ции импульсных откликов, соответствующих различным комбинациям предыдущих и последующих символов,Таким образом, на выходе второгосумматора 12 формируется отклик наанализируемый символ (с задержкойна время=Т и при интервале анализа Т =2 Т), а на двух крайнихотводах второго элемента б задержкиотклики от опережающего символа иот отстающего символа (на интервалах анализа Та=Т) .Для реализации оптимального алгоритма обработки сигналов с фазовой манипуляцией необходимоучитывать (компенсировать) отличие в энергиях приходящих, интерферируюцих между собой, сигналов.Компенсация этой энергии, в зависимости от различного чередования предыдущих и последующих символов, осуществляется в блоке 10 компенсации путем "взвешивания" илидобавления различных коэффициентов к напряжениям на выходах дополнительных сумматоров 8 и инверторов 9.Таким образом, результаты работы анализируемого сигнала, а также по отдельности - предыдущихи последующих сигналов, поступают,с одной стороны, на решающий блок13 и, с другой стороны, на блоки11 выбора максимального напряжения.При этом на блоках 11 осуществляется выбор максимального сигнала изсовокупности всевозможных чередований лишь предыдущих и последующихсигналон. Каждый из блоков 11 ныбора максимального напряжения выбирает максимальное напряжение с учетом как положительной полярности по 5 лезных сигналов, так и отрицательной полярности полезных сигналов.С выходов блоков 11 в моменты времени КТ (К=1,2,) на входы первого сумматора 7 поступают дна макси 10 мальных напряжения (при этом однопротивоположной полярности) и на выходе формируется напряжение разности. физический смысл этого напряжения состоит в том, что оно представляет собой уровень компенсациивлияния предыдущих и последующих симнолон на анализируемый. При этомучет влияния осуществляется в соответствии с оптимальным алгоритмомвыбора максимально достоверного сигнала (в данном случае применительнок максимально достоверному чередованию предыдуцих и последующих символов) .Напряжение с выхода первого сумматора 7 поступает в качестве порогового напряжения на второй вход решающего блока 13, на котором осуществляется сравнение уровня сигнала,соотнетствуюцего отклику на анализируемый сигнал (на интервале времениТО=2 Т с пороговым значением, сформированным из всевозможных чередований предыдущих и последующих сигналов.З 5 На выходе решающего блока 13 формируется напряжение положительнойили отрицательной полярности (в виде прямоугольных импульсон), применительно к сигналам с фазовой манипу 40 ляцией и с интервалом следования ТРассмотрим работу предлагаемогодемодулятора при следующих .параметрах: вид манипуляции - фазоная (и =2);количество ячеек памяти первого эле 45 мента 3 задержки на интервале времени Т равной И =4; интервал анализа ТС,=2 Т; вид ограниченного поспектру сигнала.интерференция распространяется наодин предыдуций и один последующийсигнал.Непрерывный, ограниченный по по 55 лосе, сигнал (Фиг.2 а) поступаетна вход дискретизатора 2, с помощью которого превращается в последовательность импульсов с амплитудами, равными выборочным значениям60сигнала в моменты времени 1:(К=1,2. ) . Выборочные значения сигнала продвигаются по ячейкам памяти первого элемента 3 задержки н качестве которого используется65 дискретно-аналоговая линия задерж 1062891ки. Количество ячеек первого элемента эадержки равно Й .в .3, При этом ячейки с первой по четвертую первого элемента З задержки подключены к соответствующим входаи блока 4, на выходе которого будет импульсный отклик (Фиг.20) сигналаР6 п-(О - х,Т), а ячейки с пятой по восьмую - к другим соответствующим входам блока 4, на выходе которого будет импульсный отклик (Фиг.2 в) сигналаБп -,с)= в ,(тЛ),тКак видно из временных диаграмм (фиг.2 б,в),сумма этих двух импульсных откликов представляет собой полный отклик Фильтра, согласованного с сигналом 1. (У на интервале анализа 0 ( т,1 Т, Для сигналов с Фазовой манипуляцией(.,(1,Н.) можно показать, что алгоритм оптимальной обработки в условиях межсимвольной интерференции сводится к вычислению значения функции корреляции сигнала ,с входным сигналом (Фиг,2 а) в моменты времени 1;Т (К=1,2)и сравнению этих значений с пороговым уровнем, который определяется, как результат всевозможных комбинаций предыдущих и последующих сигналов. Для определения этого порогового напряжения в предлагаемом демодуляторе используются соответствующие блоки, на которых осуществляется выбор максимального напряжения (для рассматриваемых 5 10 15 20 25 30 35 40 сигналов с фазовой манипуляцией) с учетом симметричности отклика(С),При этом для перебора всевозмохных комбинаций предыдущих и последующих символов (1 1 1,-1 1 1, 1 1 -1, -1 1 -1) применяется задержка при помощи второго элемента 6 задержки суммарного отклика сигнала ) 1 т.) на время Т (фиг.2 г), Второй элемент 6 задержки может представлять собой двухтактную линию (выборочные значения поступают одновременно на два входа и параллельно продвигактся как бы по ячейкам двух линий), к двум средним отводам которой (с двух параллельных линий подключен второй сумматор 12, а крайние отводы подсоединены к первой ячейке одной линии и к последней ячейке другой линии., Таким образом, осуществляется задержка откликов (фиг.2 б) на время 2 Т (Фиг.2 д).Осуществляя перебор комбинаций сигналов (Фиг,2 в,д), На решающем блоке 13 в соответствии с алгоритмом будет осуществляться сравнение напряжения (Фиг.2 е и порогового напряжения (Фиг,2 ж,При этом регистрируется символ "1", если напряжение (Фиг.2 е) в моменты времени КТ больше напряжения (Фиг.2 ж) и регистрируется символ "-1", если напряжение (Фиг.2 е в моменты времени КТ меньше напряжения (Фиг, 2 ж) .Таким образом, такая реализация предлагаемого демодулятора дискретных сигналов применительно к сигналам с Фазовой манипуляцией позволяет существенно увеличить быстродействие.1062891 каз 10262/59 Тираж 677 П ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., писно 5 ППП "Патент", г. Ужгород, ул. Проектная,Составитель А. Москевичктор Н. Данкулич ТехредМ,Гергель Корректор Г. Решетник

СмотретьЗаявка

3500315, 20.10.1982

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. М. И. КАЛИНИНА

МАКАРОВ СЕРГЕЙ БОРИСОВИЧ, ЦИКИН ИГОРЬ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: H04L 27/22

Метки: демодулятор, дискретных, сигналов

Опубликовано: 23.12.1983

Код ссылки

<a href="https://patents.su/6-1062891-demodulyator-diskretnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Демодулятор дискретных сигналов</a>

Предыдущий патент: Цифровой приемник многопозиционных сигналов

Следующий патент: Электронный тастатурный номеронабиратель

Случайный патент: Дезинфицирующее средство