Устройство для реализации микропрограммных автоматов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

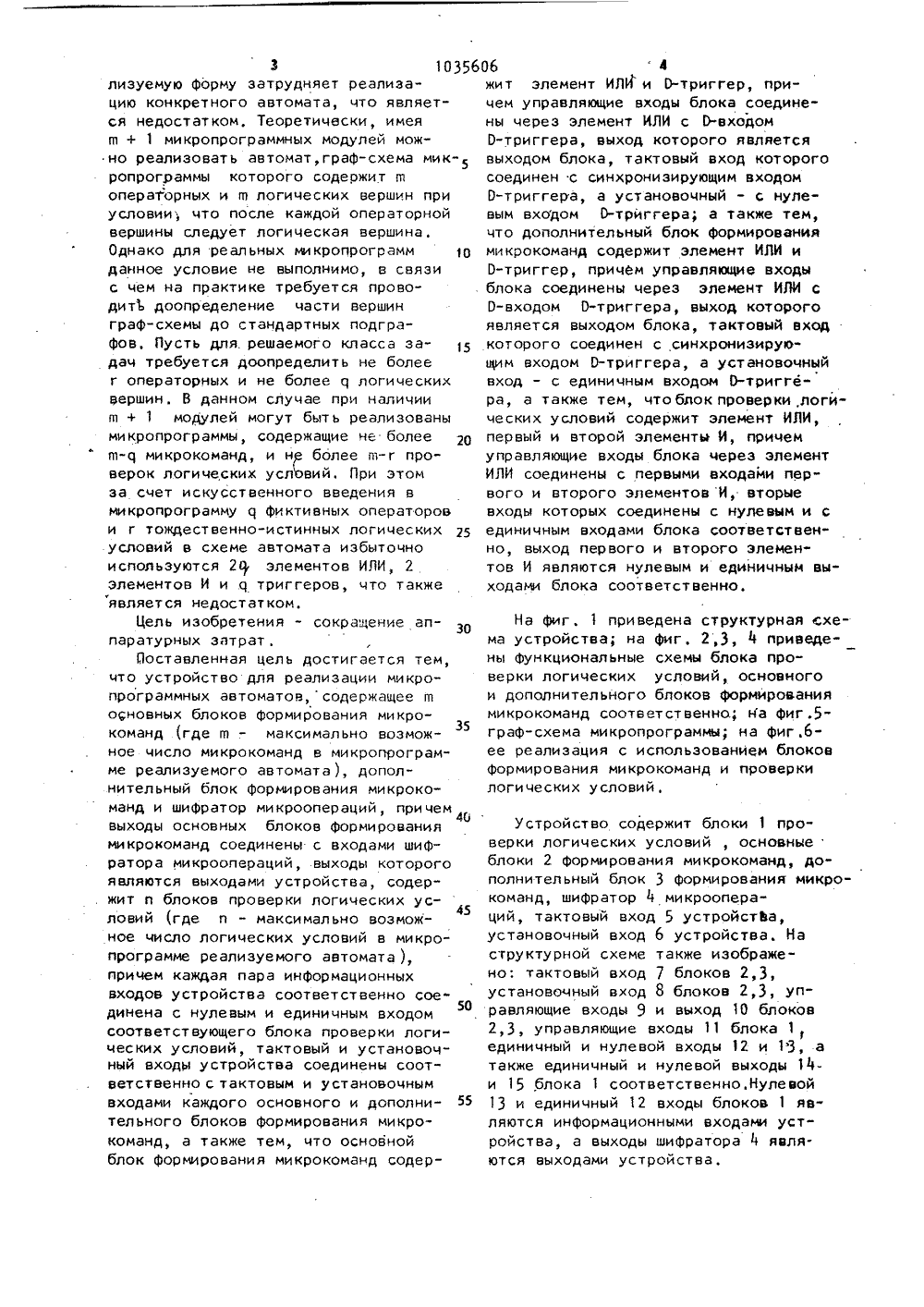

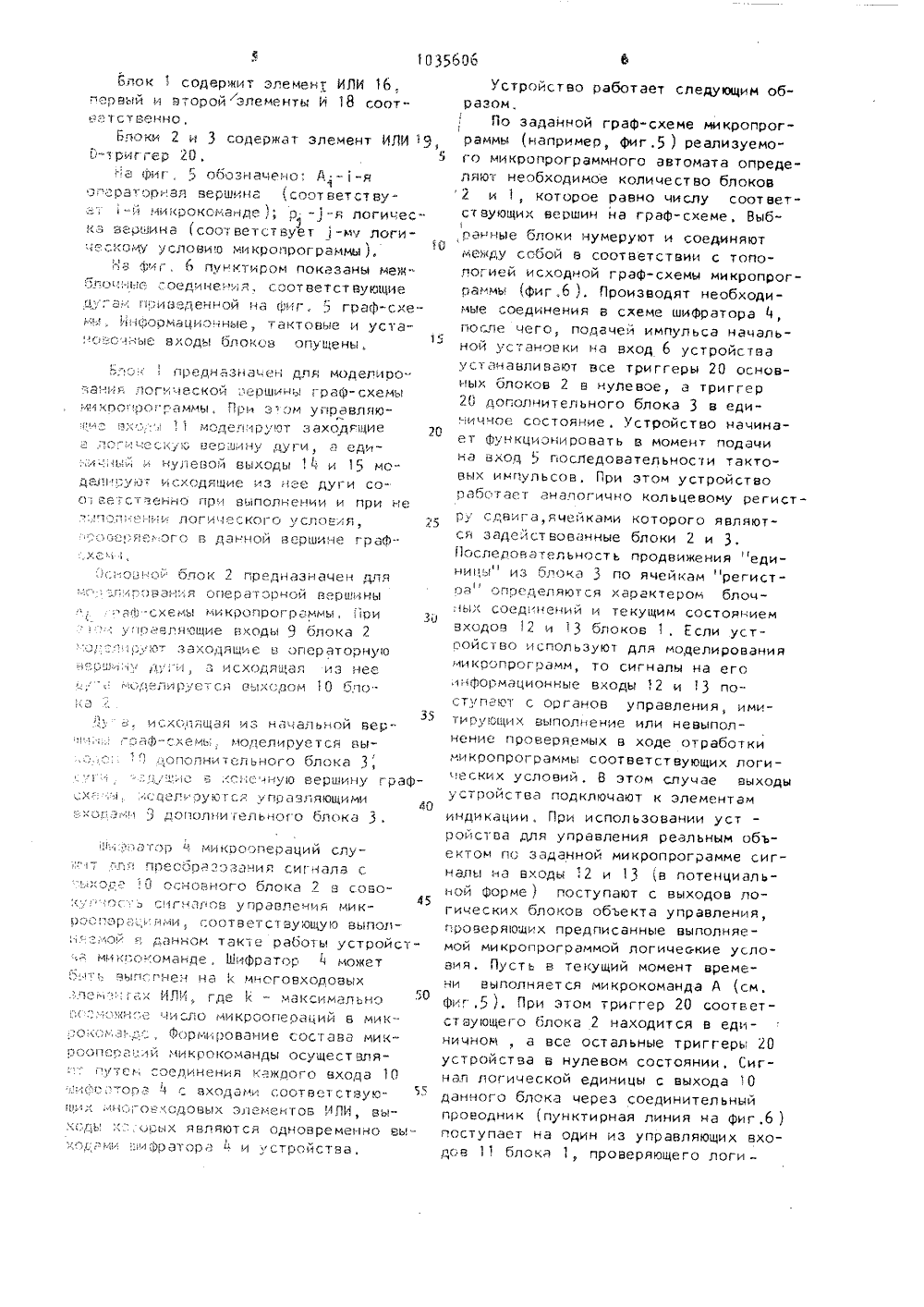

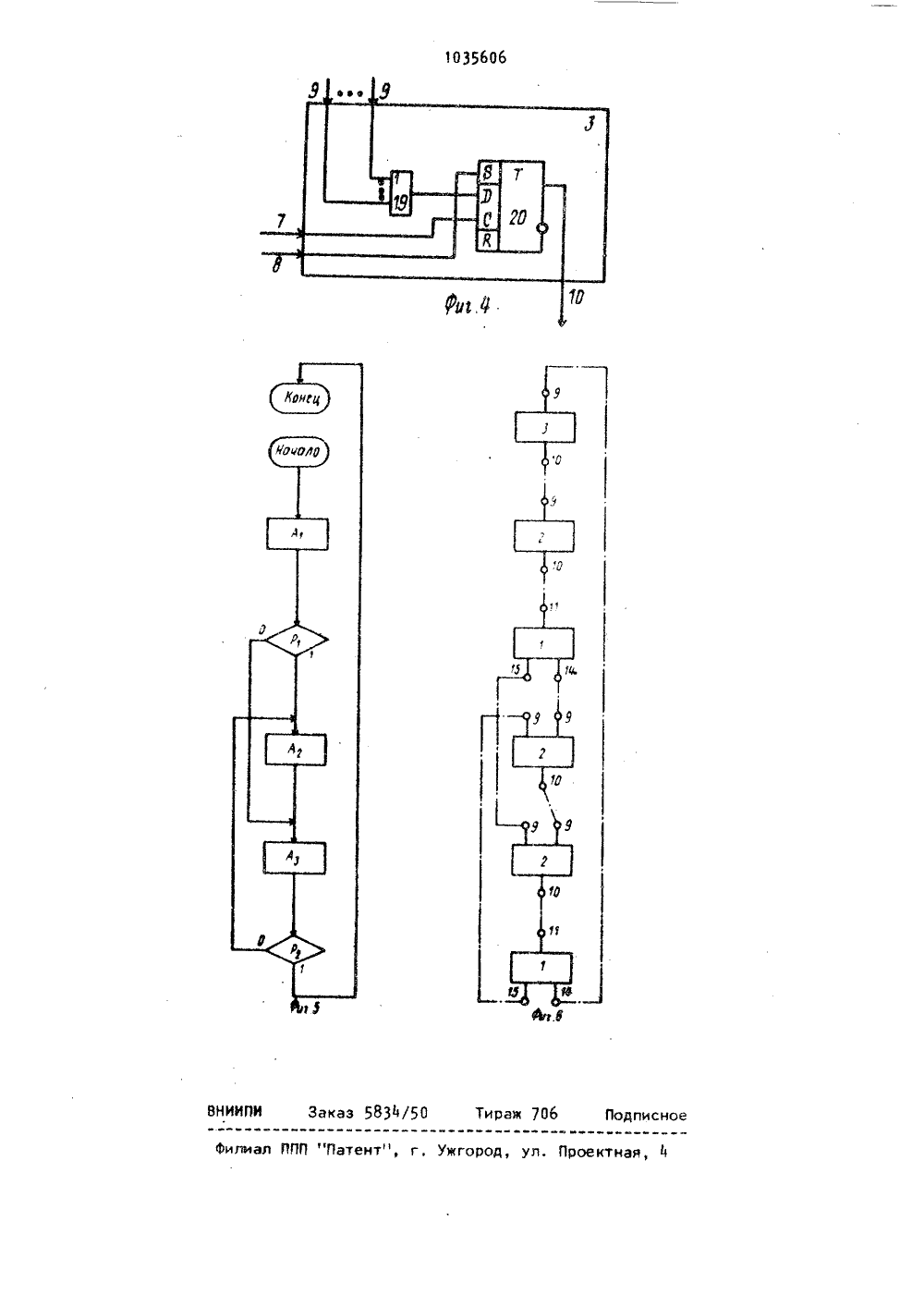

союз советснихСОЦИАЛИСТИЧЕСНРЕСПУБЛИН 356 11 О 06 Г 9/00 ч НИЕ ИЗОБРЕТЕН Д. П бн л ьств 6, 19 Синте1, Х с,118 микроьков,госудАРственный номитет сссРпо делАм изОБРетений и ОтнРытий АВТОРСКОМУ СВИДЕТЕЛЬСТ(54)(57) 1. УСТРОЙСТВО ДНЯ РЕАЛИЗАЦИИ МИКРОПРОГРАММНЫХ АВТОМАТОВ, содержащее щ основных блоков Формирования микрокоманд (где в - максимально воз можное число микрокоманд в микропрограмме реализуемого автомата), дополнительный блок Формирования микрокоманд и шифратор микроопераций, причем выходы основных блоков формирования микрокоманд соединены с входами шифратора микроопераций., выходы которого являются выходами устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит и блоков проверки логических условий (где и - максимально возможное число логических условий в микропрограмме реализуемого автомата), причем каждая пара информационных входов устройства соот-, ветственно соединена с нулевым и единичным входом соответствующего блока проверки логических условий, тактовый и установочный входы устройства соединены соответственно с так- Е товым и установочным входами каждого основного и дополнительного блоков формирования микрокоманд,1035606 2, Устройство по и. 1, о т л ич а ю щ е е с я тем, что основной блок формирования микрокоманд содержит элемент ИЛИ и О"триггер при чем угравляющие входы блока соединены через элемент ИЛИ с О-входом О-триггера, выход которого является выходом блокатактовый вход которого соединен с синхронизирующим входом О-триггера, а установочный - с нулевым входом О-триггера,3. ,Устройство по и, 1, о т л ич а ю щ е е с я тем, что дополниельньй олок формирования микрогрограмм содержит элемент ИЛИ иО-триггер, причем управляющие входы блока соединены через элемент ИЛИ с О-входом О-триггера выход которого Изобретение относится к автомати" , е и вычислительной технике , в частности к устройствам управления и конт" роля и может быть использовано как для моделирования микропрограмм, опи сывающих процесс Функционирования управляющих автоматов, так и для управления исполнительными устройствами объектов управления по заданной микропрограмме,1 ОИзвестно устройство для реализации конечных автоматов на вычислительной среде, содержащее вычислительную средуавтомат настройки, дешифраторц,триггеры элементы И 1.15Недостатками этого устоойства являются сложность схемы и большой объем оборудования.Наиболее близким техническим решением к иэобоетению является микропрограммный автомат, содержащий группу микропрограммнцх модулей, выходыкоторцх через шифратор микрооперацийсоединены с выходами автомата,Настройку автомата на заданнуюмикропрограмму осуществляют путемсоответствующей коммутации входоввыходов микропрограммных модулей,".ля этого выполняют следующее: выделяют на граФ-схеме реализуемой микРопрограммы стандартные подграфц,предсазляющие собой последовательное соединение операторной и логичеявляется выходом блока, тактовый вход которого соединен с синхронизирующим входом О-триггера а установочный вход - с единичным входом О-триггера.Устройство по и, 1, о т л ич а ю щ е е с я тем, что блок проверки логических условий содержит элемент ИЛИ, первый и второй элементы И, причем управляющие входы блока через элемент ИЛИ соединены с первыми входами первого и второго элементов И, вторые входы которых соединены с нулевым и с единичным входами блока соответственно, вцходы первого и второго элементов И являются нулевым и единичным выходами блока соответственно. ской вершины; доопределяют до стандартного подграфа оставшиеся операторные вершины (кроме начальной ) введением тождественно-истинных логических вершин; доопределяют до стандартного подграфа оставшиеся логические вершины введением Фиктивных операторных вершин; сопоставляют с каждым стандартным подграфом соответствующий микропрограммный модуль; сопоставляют с каждым стандартнымподграфом соответствующие информационные входы автомата , а для подграфов,содержащих тождественно-истинные логические вершины, предусматривают специальный вход для нейтрализации неиспользуемого нулевого выхода соответствующего микропрограммного модуля; сопоставляют с каждым стандартным подграфом уставоночные входы соответствующего микропрограммного модуля, указав для них номера тех микропрограммных модулей, выходные сигналы которых должны быть использованы для возвращения данного микропрограммного модуля в исходное состояние; произвс- дят соединение входов и выходов используемых микропрограммных модулей в соответствии с топологией полученной структурно-реализуемой граф-схемой микропрограммы2,Необходимость преобразования исходной граф-схемц в структурно-реа606 4 3 1035лизуемую Форму затрудняет реализацию конкретного автомата, что является недостатком, Теоретически, имеяш + 1 микропрограммных модулей можно реализовать автомат, граф-схема мик ропрограммы которого содержит шопераТорных и щ логических вершин приусловии что после каждой операторнойвершины следует логическая вершина,Однако для реальных микропрограмм 10данное условие не выполнимо, в связис чем на практике требуется проводить доопределение части вершинграф-схемы до стандартных подграФов, Пусть для. решаемого класса задач требуется доопределить не болеег операторных и не более ц логическихвершин. В данном случае при наличиищ + 1 модулей могут быть реализованымикропрограммы, содержащие не более 20щ-с 1 микрокоманд, и нв более ш-г проверок логических условий. При этомза счет искусственного введения вмикропрограмму с 1 фиктивных операторови г тождественно-истинных логических 25условий в схеме автомата избыточноиспользуются 2 ф элементов ИЛИ, 2элементов И и .ц триггеров, что такжеюявляется недостатком.Цель изобретения - сокращение апЗОпаратурных затрат,Поставленная цель достигается тем,что устройство для реализации микропрограммных автоматов,содержащее щосновных блоков формирования микрокоманд (где щ . - максимально возмож 35ное число микрокоманд в микропрограмме реализуемого автомата), дополнительный блок формирования микрокоманд и шифратор микроопераций, причемвыходы основных блоков Формирования40микрокоманд соединены с входами шифратора микроопераций, выходы которогоявляются выходами устройства, содер"жит и блоков проверки логических усч У45ловии (где и - максимально возможное число логических условий в микропрограмме реализуемого автомата ),причем каждая пара информационныхвходов устройства соответственно соединена с нулевым и единичным входом50соответствующего блока проверки логических условий, тактовый и установочный входы у строй ства соединены соответственно с тактовым и установочнымвходами каждого основного и дополнительного блоков формирования микрокоманд, а также тем, что основнойблок формирования микрокоманд содержит элемент ИЛИ и О-триггер, причем управляющие входы блока соединены через элемент ИЛИ с О-входомО-триггера, выход которого являетсявыходом блока, тактовый вход которогосоединен с синхронизирующим входомО-триггера, а установочный - с нулевым входом О-триггера; а также тем,что дополнительный блок Формированиямикрокоманд содержит элемент ИЛИ иО-триггер, причем управляющие входыблока соединены через элемент ИЛИ сО-входом О-триггера, выход которогоявляется выходом блока, тактовый входкоторого соединен с синхронизирующим входом О-триггера, а установочныйвход - с единичным входом О-тригге"ра, а также тем, чтоблок проверки, логических условий содержит элемент ИЛИ,первый и второй элементы И, причемуправляющие входы блока через элементИПИ соединены с первыми входами первого и второго элементов И, вторыевходы которых соединены с нулевым и сединичным входами блока соответственно, выход первого и второго элементов И являются нулевым и единичным выходами блока соответственно. На фиг. 1 приведена структурная схема устройства; на фиг. 2,3, 4 приведены Функциональные схемы блока проверки логических условий, основного и дополнительного блоков Формирования микрокоманд соответственна; на Фиг.5- граф-схема микропрограммы; на Фиг,6- ее реализация с использованием блоков Формирования микрокоманд и проверки логических условий,Устройство содержит блоки 1 проверки логических условий , основныеблоки 2 Формирования микрокоманд, дополнительный блок 3 Формирования микрокоманд, шифратор 4 микроопераций, тактовый вход 5 устройстЬа,установочный вход 6 устройства. Наструктурной схеме также изображено: тактовый вход 7 блоков 2,3,установочный вход 8 блоков 2,3, управляющие входы 9 и выход 10 блоков2,3, управляющие входы 11 блокаединичный и нулевой входы 12 и 13, атакже единичный и нулевой выходы 14 и 15 блока 1 соответственно. Нулевой13 и единичный 12 входы блоков 1 являются информационными входами устройства, а выходы шифратора 4 являются выходами устройства,1035606 Ф5 япк 1 содврж 1 лэлемент ИЛИпервый и второй лементы И 18 соотВВТСТВ 8 ННО,Блоки 2 и 3 содержат элемент ИЛИ 19,:" с Фиг " Обозначено. А -1-ЯЗгеРатОРНал ВЕРШИНа (СООтВЕтСтВУ -й микрокоманде / р"я лоГич 8 с"ка Вершина (соответствует 1-му логическому условио микропрОГраммы )1-1 а Фиг, 6 пунктиром показаны межбго 1 нь 18;Оедине 1 Я, соответствующи 8В Га;:к;иведенной на фиг, 5 граф-схем;, й 11 йоомационные тактовы 8 и уста15,.с,.с -1 нь 18 входы олоков опущены. О1 Г 1 рецназначен ДлЯ модели ро" анИ л ЛОГИ Ч ВСКОЙ ЗВРШИНЫ ГРВФ СХЕМЫ микоог 1 ОО,: раммы, При э. Ом уг 1 равляюмодег 1 ир,"от заходл 1 циел лзГлШЛНу лу 1 Иа едл :-,и-:, ы; " нулевой Вь;ходы 11 и 15 МО" О 8.ПНРУЮт ИСХОДЛЩИ 8 ИЗ НВЕ ДУГИ СОО;, 88 Гот ВВННО ЛРИ ВЫГ 1 ОЛН 8 НИИ И ПРИ НЕ -:,1 ПСП -8, 11 л 1 ЛОГИЧ 8 СКОГО ."СЛОВЛЯ,, Яе. ОГО В данной Вершине Граф.,:;,Озго:. блок 2 предназначен для л.1 Г О В а Н Я О Пе Р а Т О Р Ч ОЙ В 8 Р ШИ Н Ы аф.схемы мг кропрограммы. Пои (18 Вляощие Входы 9 блока 2 Ол;,С, Ют ЗВХОДЛЦИЕ В ОП 8 РатОРНУ 1 О ,рш 1" д 1, ,. а исходящая из нее1 О,:;,ели 1 уст сл Выходом 0 блоа, исходящая и 3 наал ьнои ВерГоаф-:хемгы моделлруетсл Выополнительного блока 3;. 8 В ,.Оно"ную Вершину граФ;.Х-:1. ОДВЛИРУЮТСЛ УПРВЗЛЯЮЦИМИ Щ хо 1 и 9 дополни.18 льного блока 3. шн,;агар ц микроопераций слуппеоооазоаания сигнала с "л.хол: :0 основного блока 2 В сово о э сигналов управления мик 5 роо 1.Ор 8-,1, лми, соотв ет ст Бу Оцую Вып 011- , :змой -: данном такте работы устройст:,л микпокоманде, Шифратор 11 может ,"иГГ: ВЫПСПНЕН НаМНСГОВХОДОВЫХЦП 11 ГО 8- МаКСммаЛЬНО:";,н."8 -1 исло микроопераций В мик;Окомз,;:., Форм 1:,рование состава микроопера:.лй микрокоманды осуществлягутен соединения кажвого Входа 10йо Опэ 4 " Входами соответствую Х ии108 ХОДОВЫХ ЭЛВМВНТОВ ЛИ, ВЫ- я:ды .Орых лвляются Одновременно Выи ,:Гг,м 1 л 81 л Фр а 1 Ор а Я л у строист В а Устройство работает следуоцим образомПо заданной граф-схеме микропрограммы (например, фиг.5 ) реализуемого микропрограммного автомата определяют необходимое количество блоков 2 и 1, которое равно числу соответствующих вершин на граф-схеме, Выбранные блоки нумеруют и соединяют между ссбой в соответствии с топологией исходной граф-схемы микропрограммы (Фиг,б ), Производят необходимые соединения в схеме шиФратора погпе чего, подачей импульса начальной установки на вход 6 устройства устанавливают все триГгеры 20 основных олоков 2 В нулевое, а триггер 20 доголнительного блока 3 в единичное состояние . Устройство начинает Функционировать в момент подачи на Вход 5 Госледовательности тактоВых импульсов, При этом устройство рабстает аналогично кольцевому регистсдвиГа,ячейками котороГО являются задействованные блоки 2 и 3, Последовательность продвижения "едиНИ 11 ы" из блока 3 по ячейкам "регистраопределяются характером блоч,1 ых соединений и текущим состоянием Входов 12 и 13 блоков 1. Если устройство используют для моделирования микропрограмм, то сигналы на его нформационные входы 12 и 13 поступают с органов управления, имитиру;ощих Выполнение или невыполнение проверяемых В ходе отработки микропрограммы соответствующих логических условий, В этом случае Выходы устройства подключают к элементам индикации, При использовании уст ройства,цля управления реальным объектом пс заданной микропрограмме сигналы на входы 12 и 13 (в потенциальной Форме ) поступают с выходов логических блоков объекта управления, проверяющих предписанные выполняемой микропрограммой логические условия, Пусть В текущий момент времени выполняется микрокоманда А (см, Фиг.5 ). При этом триггер 20 соответствующего блока 2 находится в единичном , а все остальные триггерь 20 устройства В нулевом состоянии, бигнап логической единицы с выхода 10 данного блока через соединительный проводник (пунктирная линия на Фиг.б ) поступает на один из управляющих вхо- ДОВ 11 блока 1, проверяющего логическое условие Р . Через элемент ИЛИ 16 данного блока этот сигнал будет приложен к первым входам элементов И 17, 18 того же блока, Если логическое условие Р, проверяемое данным блоком, не выполнено, в этом случае на втором входе элемента И 17 рассматриваемого блока 1 присутствует сигнал логической единицы, что приводит к появлению единичного сиг 1 О нала на нулевом выходе 15Через соответствующий соединительный проводник этот сигнал приложен к одному из уп,равляющих входов 9 блока 2, моделирующего операторную вершину А и далее через элемент ИЛИ 19 этого блокак 0-входу соответствующего триггера 20, В момент появления на входе 5 устройства очередного тактового импульса данный триггер переходит в единичное состояние , а предыдущий возвращается в нулевое состояние . Таким образом прекращается выполнение микрокоманды А , а сигналом с выхода 10 сработавшего блока 2 в шифраторе сформируется микрокоманда А. Если же логическое условие Р, в момент его проверки окажется выполненным, то очередным тактовым импульсом в единичное состояние будет переведен триггер 20 дополнительного блока 3. Срабатывание этого триггера прекращает по-; дачу тактовых импульсов на вход 5, что вызывает останов устройства (генератор тактовых импульсов и цепи управ ления на фиг. 1 не показаны ).Для повторного запуска устройства необходимо вновь включить генератор тактовых импульсов.Введение в устройство блоков позволяет реализовать конкретный микропрограммный автомат непосредственно по исходной граф-схеме микропрограммы, минуя этап преобразования ее в структурно-реализуемую форму, Это упрощает структуру межблочных соедине" ний и процедуру, реализации автомата в целом.Аппаратурные затраты на изготовление предложенных одного блока 1 и одного блока 2 равны аппаратурным затратам на изготовление известного бло" ка. Поэтому при использовании в предложенном устройстве одинакового числа этих блоков (п=щ ) суммарные аппа ратурные затраты на его изготовление меньше по сравнению с известным устройством на два элемента И, входящих в состав его (в+1)-го блока, модулирующего конечную вершину граф-схемы.Это достигается за счет отсутствия подобных элементов в дополнительном блоке 3, выполняющем в предложенном устройстве аналогичную функцию. При пФа эффект от использования изобретения , выражающийся в сокращении аппаратурных затрат, пропорционален абсолютной величине разности щ-и и зависит от класса решаемых с его помощью задач.Применение изобретения позволяет упростить процедуру реализации микропрограммного автомата и сокра-. тить объем оборудования устройства.1935606 ИИПИ Заказ 5834/50 Тираж илиал ППП "Патент", г. Ужгород,оектн исно

СмотретьЗаявка

3365908, 17.12.1981

РИЖСКОЕ ВЫСШЕЕ ВОЕННО-ПОЛИТИЧЕСКОЕ КРАСНОЗНАМЕННОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА БИРЮЗОВА С. С

КУДРЯВЦЕВ АЛЕКСАНДР ВЛАДИМИРОВИЧ, ПОТЕБНЯ ЛЕОНИД ДМИТРИЕВИЧ

МПК / Метки

МПК: G06F 9/00

Метки: автоматов, микропрограммных, реализации

Опубликовано: 15.08.1983

Код ссылки

<a href="https://patents.su/6-1035606-ustrojjstvo-dlya-realizacii-mikroprogrammnykh-avtomatov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для реализации микропрограммных автоматов</a>

Предыдущий патент: Цифровой интегратор

Следующий патент: Многоканальное приоритетное устройство для подключения абонентов к общей магистрали

Случайный патент: Способ изготовления шлифовальнойшкурки c прерывистой режущей поверхно-стью