Формирователь сложной функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 995312

Авторы: Комаров, Никольченко

Текст

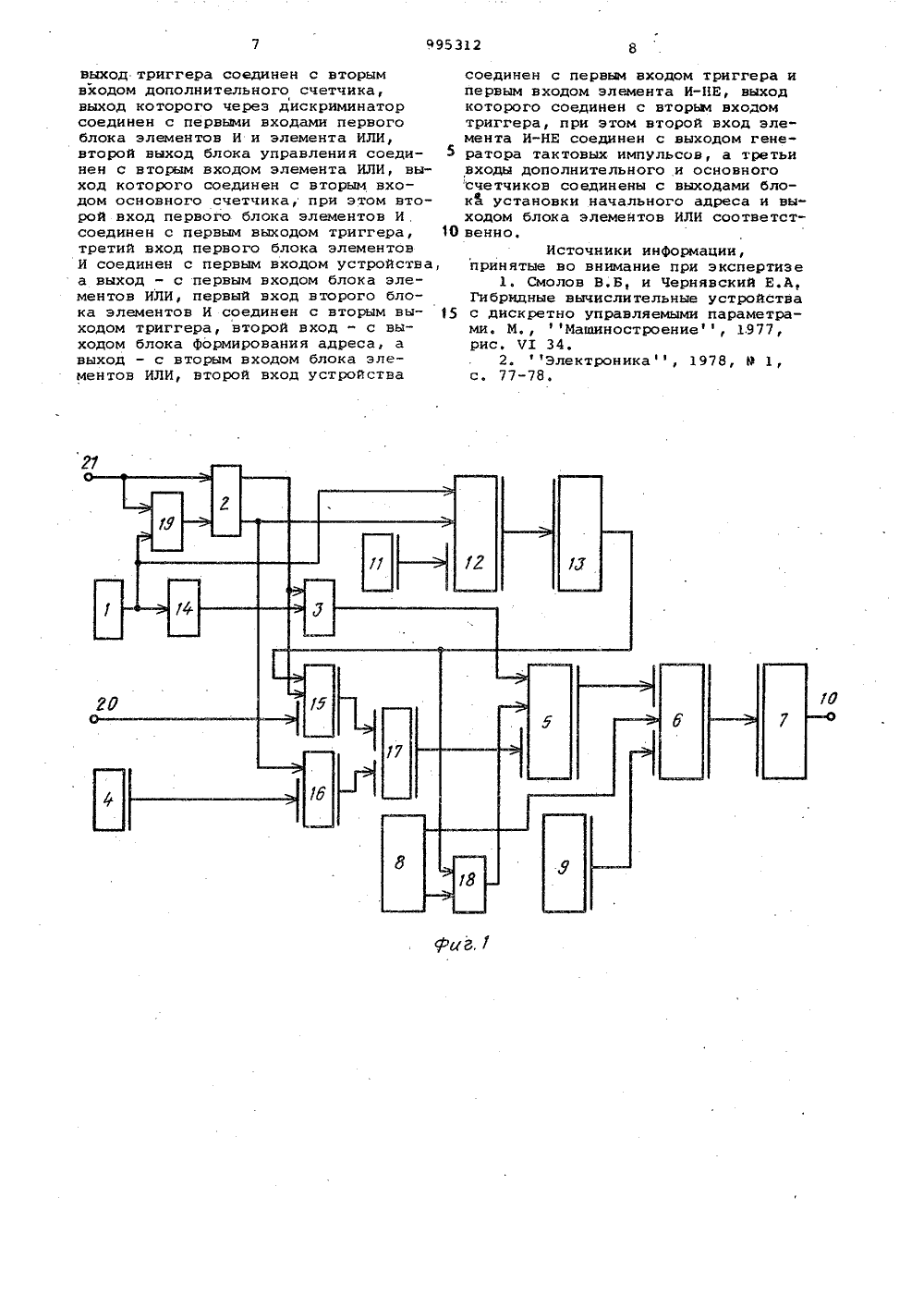

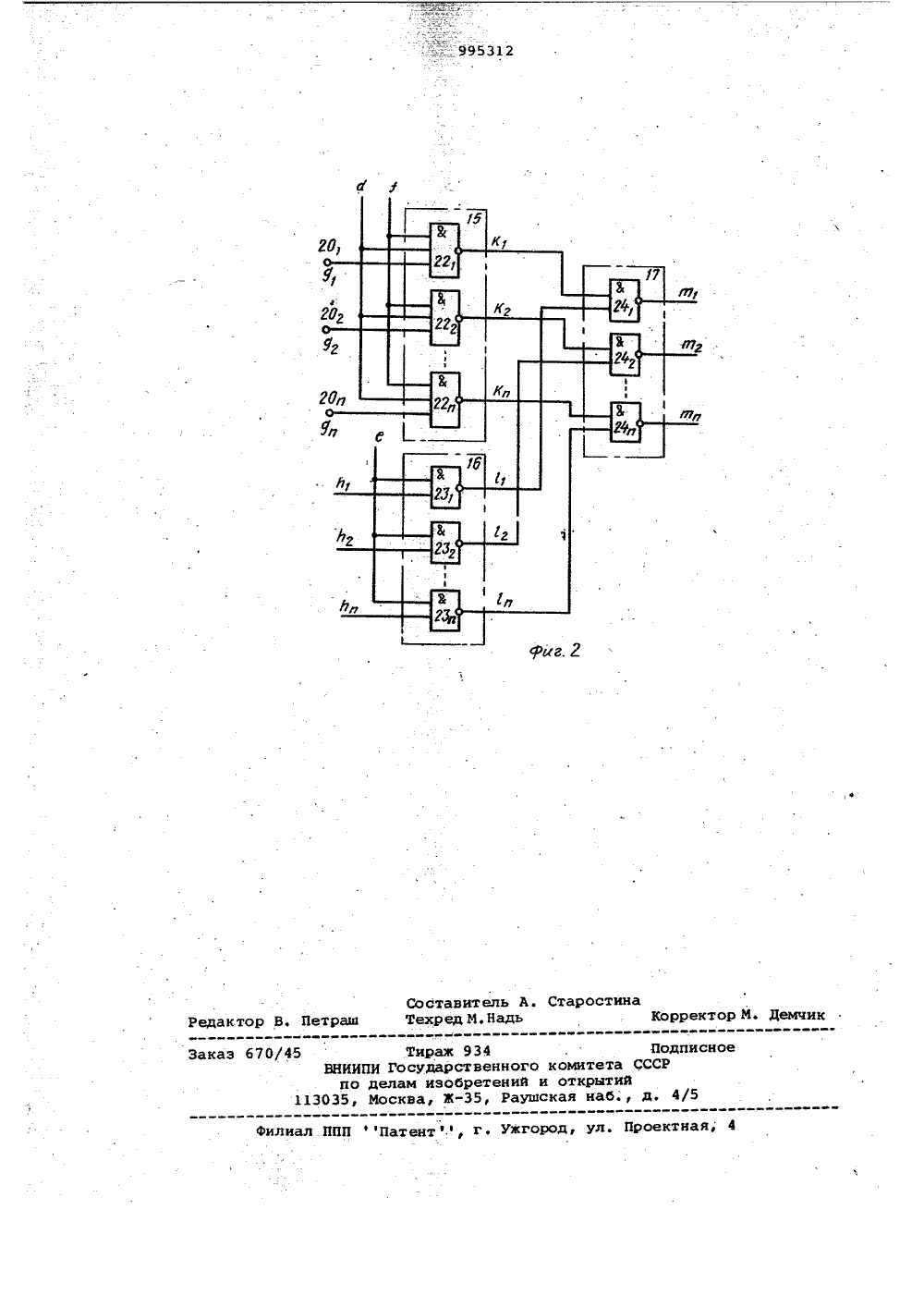

ОПИСАНИЕ ИЗОБРЕТЕНИЯ он 995312 Соеэ СоветскихСоциалистическихРеспублик К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(22) Заявлено 07.09. 81 (21) 3335828/18-21 И 1 М.КЯ.з с присоединением заявки Йо(23) ПриоритетН 03 К 13/02 Государственный комитет СССР по делам изобретений н открытийОпубликовано 0702 ВЗ, Бюллетень Йо 5 Дата опубликования описания 0-7.02,83(54) ФОРМИРОВАТЕЛЬ СЛОЖНОЙ ФУНКЦИ Изобретение относится к аналого"цифровой вычислительной технике иможет быть использовано в аналого"цифровых вычислительных комплексахи устройствах автоматики.Известен преобразователь код " Фа;за, содержащий блок квадратурных напряжений, коммутатор опорных напряжений, ключи. которого управляютсядвумя старшими разрядами и-разрядногб кода Н, функциональные преобразователи, блоки умножения и двухвходовый бпок суммирования 1),Недостатком преобразователя явля-.ется возможность преобразования сигналов только синусоидальной ФормыНаиболее близким к предлагаемомуявляется Формирователь сложной функции, содержащий генератор тактовыхИМпульсов, триггер, элемеят И, блокФормирования адреса в который входятпереключатели с двоично-кодированныминаборными дисками Б 1 - Б 3 и четырепреобраэоватеЛя двоично-кодированного сигнала, в двоичный, основной счетчик, оперативный запоминающий узел,цифроаналоговый преобразователь, .блокуправления, включающий триггер управления записью и триггер загрУзкиадреса, блок Формирования информации с пеРеключателями Б, Б 5., пРичем выход основного счетчика соединен спервым входом оперативного запоминающего узла, выход которого черезцифроаналоговый преобразователь соединен с выходом устройства, второйи третий входы оперативного запоминающего узла соединены с первым выходом блока управления и с выходом бло"ка Формирования информации соответственно, первый выход триггера сое"динен с первым входом элемента И, выход которого соединен с первым входом основного счетчика, а второй итретий входы основного счгчика соединены с выходами блока управления иблока формирования адреса соответственно, выход генератора тактовых импульсов соединен с вторым взводом элемента И 2) .Недостатком известного устройства является невозможность реализации ре-. жима преобразователя код - фаза.Цель изобретения - расширение функциональных возможностей устройи. ства.Поставленная цель достигается тем, что в известный Формирователь, содержащий генератор тактовых импульсов, триггер, .элемент И, блок формирова"держки, первый блок 15 элементов И,второй блок 16 элементов И, блок 17элементов ИЛИ элемент ИЛИ 18, элемент И-НЕ 19, оперативный запоминающий узел (ОЗУ) б, цифроаналоговыйпреобразователь 7 (ЦАП), блок 8 управления (БУ) блок 9 формирования информации (БФИ), блок 11 установки наЖльного адреса (БУНА), дополнительный счетчик 12 (ДС), дискриминатор13 (Д),Устройство функционирует в двухрежимах: программирования ОЗУ б ипреобразования код - фаза. Следуетотметить, что первые входы ОС 5 иДС 12 являются счетными, вторыевходами синхронизации, а третьи - установочными. При этом единичное значение сигнала на входе синхронизации (высокий уровень) разрешает занесение информации с установочныхвходов. Нулевое значение сигнала навходе синхронизации разрешает заполнение счетчика счетными импульсами.Режим программирования ОЗУ б устанавливается нулевым сигналом на второмвходе 21 устройства, При этом единичный сигнал на втором выходе Т 2 открывает второй блок 16 элементов Ки устанавливает ДС 12 в режим приемакода по третьему входу (установочному) из БУНА 11. Нулевой сигнал напервом выходе Т 2 закоывает элементИ 3 и первый блок 15 элементов И. Приэтом блокируется поступление тактовых импульсов на первый (счетный)вход ОС 5 и запрещается пеоедача.кодас первого входа устройства 20.Дальнейшая работа устройства неотличается от работы прототипа в аналогичном режиме. Б БФА 4 устанавливается код адреса, который черезоткрытый второй блок 16 элементов Ии блок 17 элементов ИЛИ поступает натретий вход ОС 5. Прием этого кода вОС 5 синхронизируется импульсом, который с первого выхода БУ 8 черезэлемент ИЛИ 18 поступает на второйвход ОС 5. Необходимая информация,которая должна быть записана по выбранному адресу в ОЗУ 6, формируетсяв БФИ 9. Занесение информации в ОЗУ 6синхронизируется сигналом Запись,который по второму выходу БУ 8 поступает на второй вход (запись/считывание) ОЗУ б. Режим преобразованиякод - фаза устанавливается единичнымсигналом на втором входе 21 устройства,ния адреса, основной счетчик, оператинный запоминающий узел, цифроаналоговый преобразователь, блок управления, блок формирования информации,причем выход основного счетчика соединен с первым входом оперативного 5запоминающего узла, выход которогочерез цифроаналоговый преобразователь соединен с выходом устройства,второй и третий входы оперативногорапоминающего узла соединены с первым 10выходом блока управления .и выходомблока формирования информации соответственно, первый выход триггерасоединен с первым входом элемента И,выход которого соединен с первым вхо дом основного счетчика, дополнительно введены блок установки начальногоадреса, дополнительный счетчик, дискриминатор, блок задержки, первый ивторой блоки элементов И, блок элементов ИЛИ, элемент ИЛИ, элементИ-НЕ, причем генератор тактовых импульсов соединен с первым входом дополнительного счетчика и через блокзадержки с вторым входом элемента И,второй выход триггера соединен с вторым входом дополнительного счетчика,выход которого через дискриминаторсоединен с первыми входами дополнительных первого блока элементов И иэлементов ИЛИ, второй выход блока управления соединен с вторым входомэлемента ИЛИ, выход которого соединен с вторым входом основного счетчика, при этом второй вход первогоблока элементов И соединен с первым 35выходом триггера, третий вход первого блока элементов И соединен с первым входом устройства, а выход - спервым входом блока элементов ИЛИ,первый вход второго блока элементов 4 ОИ.соединен с вторым выходом триггера,второй вход - с выходом блока формирования адреса, а выход - с вторымвходом блока элементов ИЛИ, второйвход устройства соединен с первымвходом триггером и первым входом элемента И-НЕ, выход которого соединен,с вторым входом триггера, при этомвторой вход элемента И-НЕ соединенс выходом генератора тактовых импуль сов, а третьи входы дополнительногои основного счетчиков соединены свыходом блока установки начальногоадреса и выходом блока элементов ИЛИсоответственно,5 На фиг. 1 показана функциональная схема устройства на фиг. 2 - принципиальные схемы первого блока элементов И, второго блока элементов И и блока элементов ИЛИ.формирователь сложной функции содержит генератор тактовых импульсов (ГТИ)1, триггер (Т)2, элемент И 3, блок 4 формирования адреса (БФА)4, основной счетчик (ОС)5, блок 14 заПри этом после прихода первого тактового импульса с ГТИ 1 на первом выходе Т 2 появляется единичный сигнал, который открывает элемент И 3, разрешая прохождение тактовых импульсов с выхода. блока 14 задержки на первый вход ОС 5, и подготавливает к открыванию первый блок 15 элементов И,Нулевой сигнал на втором выходе Т 2, который появляется в момент времени С, закрывает второй блок 16 элементов И и открывает первый (счетный) вход ДС 12. ДС 12 хранит код фВсе единицы (который был в него занесен из БУНА 11), поэтому первый после смены режима импульс с выхода ГТИ 1 сбрасывает его в 1 О Нулевое состояние ДС 12 продлится до прихода второго после смены режима импульса с ГТИ 1.В течение нулевого состояния ДС 12 Д 13 формирует единичный сигнал на своем выходе., который открывает первый блок 15 элементов И, обеспечивая 5 прохождение информации от первого входа 20 устройства (входы управления фазой выходного напряжения устройства) через первый блок 15 элементов И и блок 17 элементов ИЛИ на третий 2 О (установочный) вход ОС 5, Одновременно с этим сигналом на выходе Д 13 синхронизирует прием кода, который от первого входа 20 устройства поступает на третий вход ОС 5, прохо дя через элемент ИЛИ 18 на второй вход ОС 5; При этом блокируется действие первого после смены режима импульса на выходе блока 14 задержки, который через открытый элемент И 3 поступает на первый (счетный) вход ОС 5.Далее в течение 2" "(где и - число разрядов ДС 12) импульсов тактовой частоты устройство работает так35 же, как прототип в режиме,воспроизведения сложной функции, т.е. такто" вые импульсы с выхода блока 14 задержки увеличивают содержимое ОС 5.При этом выбираются коды из после довательно расположенных 2. ячеек ОЗУ б, которые с помощью ЦАП 7 преобразуются в аналоговое напряжение.После прохождения 2" импульсов тактовой частоты после смены режима работы на выходе Д 13 снова формируется единичный сигнал и начинается новый цикл работы преобразователяАнализ работы преобразователя по" казывает, что в начале цикла преобразователя в ОС .5 заносится код адреса от первого входа 20 устройства, с которого начинается Формирование выходного напряжения, Изменением кода на первом входе 20 устройства можно управлять Фазой выходного напряжения в диапазоне 0-60 О. Первый блок 15 элементов И, второй блок 1 6 элементов И и блок 17 элементов ИЛИ реализованы на двух- и трехвходовых элементах И-НЕ 22), 222 220 231, 232,. ф., 23 д, 241 ф 242,.. ф24 п (фиг. 2) .Анализ принципа действия предлага- емого устройства показывает,что оно, сохраняя лучшие свойства прототипа 65(возможность воспроизведения любойсложной Функции с высокой точностью)обладает возможностями преобразователя код - фаза. Это свойство можетиспользоваться для создания линейных и нелинейных аналого-цифровых ицифроаналоговых преобразователей саналоговыми. величинами в виде напряжений переменного тока для связи сЦВМ, а также гибридных вычислительных устройств, обеспечивающих выполнение математических операций над цифрами и аналоговыми величинами в виденапряжения переменного тока.В предлагаемом устройстве можноуправлять фазой любой Функции,;в товремя как в известном -только гармонической. Кроме того, оно болеетехнологично, поскольку состоит только из серийно изготавливаемых элементов (интегральных микросхем)счетчиков, дешифраторов, полупроводниковых ЗУ и т.п. Известное устройство содержит дискретный преобразователь код - проводимость, воспроизводящий функцию специального вида,который серийно не выпускается. Линейность управляющей характеристики:предлагаемого устройства выше, чем уизвестного, и ограничена только числомразрядов. дополнительно введенных блоков,Формула изобретенияФормирователь сложной ФункциМ, содержащий генератор тактовых импульсов, триггер, элемент И, блок формирования адреса, основной счетчик,.оперативный запоминающий узел, цифроаналоговый преобразователь, блок управления, блок формирования информации, причем выход основногб счетчика соединен с первым входом оперативного запоминацщего узла, выход которого через цифроаналоговый преобразователь соединен с выходом устройства, второй и третий входы оперативного запоминающего узла соединены с первым выходом блока управления и выходом блока формирования информации соответственно, первый выход триггера соединен с первым входом элемента И, выход которого соединен с первым входом основного счетчика, о тл и ч а ю щ и й с я тем, что, с целью расширения Функциональных воэможностей, в него дополнительно введены блок установки начального адреса дополнительный счетчик, дискриминатор, блок задержки, первый и второй блоки элементов И, блок элементов ИЛИ, элемент ИЛИ, элемент И-НЕ при" чем генератор тактовых импульсов со" единен с первым входом дополнительного счетчика и через блок задержки с вторым входом элемента И, второйвыход триггера соединен с вторымвходом дополнительного счетчика,выход которого через дискриминаторсоединен с первыми входами первогоблока элементов И и элемента ИЛИ,второй выход блока управления соединен с вторым входом элемента ИЛИ, выход которого соединен с вторым входом основного счетчика, при этом второй вход первого блока элементов И,соединен с первым выходом триггера,третий вход первого блока элементовИ соединен с первым входом устройства,а выход - с первым входом блока элементов ИЛИ, первый вход второго блока элементов И соединен с вторым выходом триггера, второй вход - с выходом блока формирования адреса, авыход - с вторым входом блока элементов ИЛИ, второй вход устройства соединен с первык входом триггера и первым входом элемента И-НЕ, выход которого соединен с вторьм входом триггера, при этом второй вход элемента И-НЕ соединен с выходом гене ратора тактовых импульсов, а третьивходы дополнительного и основного счетчиков соединены с выходами блока установки начального адреса и выходом блока элементов ИЛИ соответст О венно,Источники информации,принятые во внимание при экспертизе1. Смолов В.Б, и Чернявский Е.А,Гибридные вычислительные устройства35 с дискретно управляемыми параметрами. М Машиностроение, 1.977,рис. ЧХ 34.2. фЭлектроника, 1978, Р 1,с. 77-78./5 ал ППП ф Патент ф., г. Ужгород, ул. Проектная, 4 з 670/45 Тираж 934 ВНИИПИ Государствен по делам изобрет 113035, Москва, Ж, Поого комитета СССнй и открытийаушская наб., д,

СмотретьЗаявка

3335828, 07.09.1981

ФИЛИАЛ "ВОСХОД" МОСКОВСКОГО ОРДЕНА ЛЕНИНА И ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ АВИАЦИОННОГО ИНСТИТУТА ИМ. СЕРГО ОРДЖОНИКИДЗЕ

КОМАРОВ АНАТОЛИЙ ВЕНИАМИНОВИЧ, НИКОЛЬЧЕНКО МАРИНА ЭДУАРДОВНА

МПК / Метки

МПК: H03K 13/02

Метки: сложной, формирователь, функции

Опубликовано: 07.02.1983

Код ссылки

<a href="https://patents.su/5-995312-formirovatel-slozhnojj-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь сложной функции</a>

Предыдущий патент: Многоканальный цифроаналоговый преобразователь

Следующий патент: Параллельно-последовательный аналого-цифровой преобразователь

Случайный патент: Способ анализа полимерной матрицы в тонком слое