Устройство для обнаружения и исправления ошибок в системе остаточных классов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

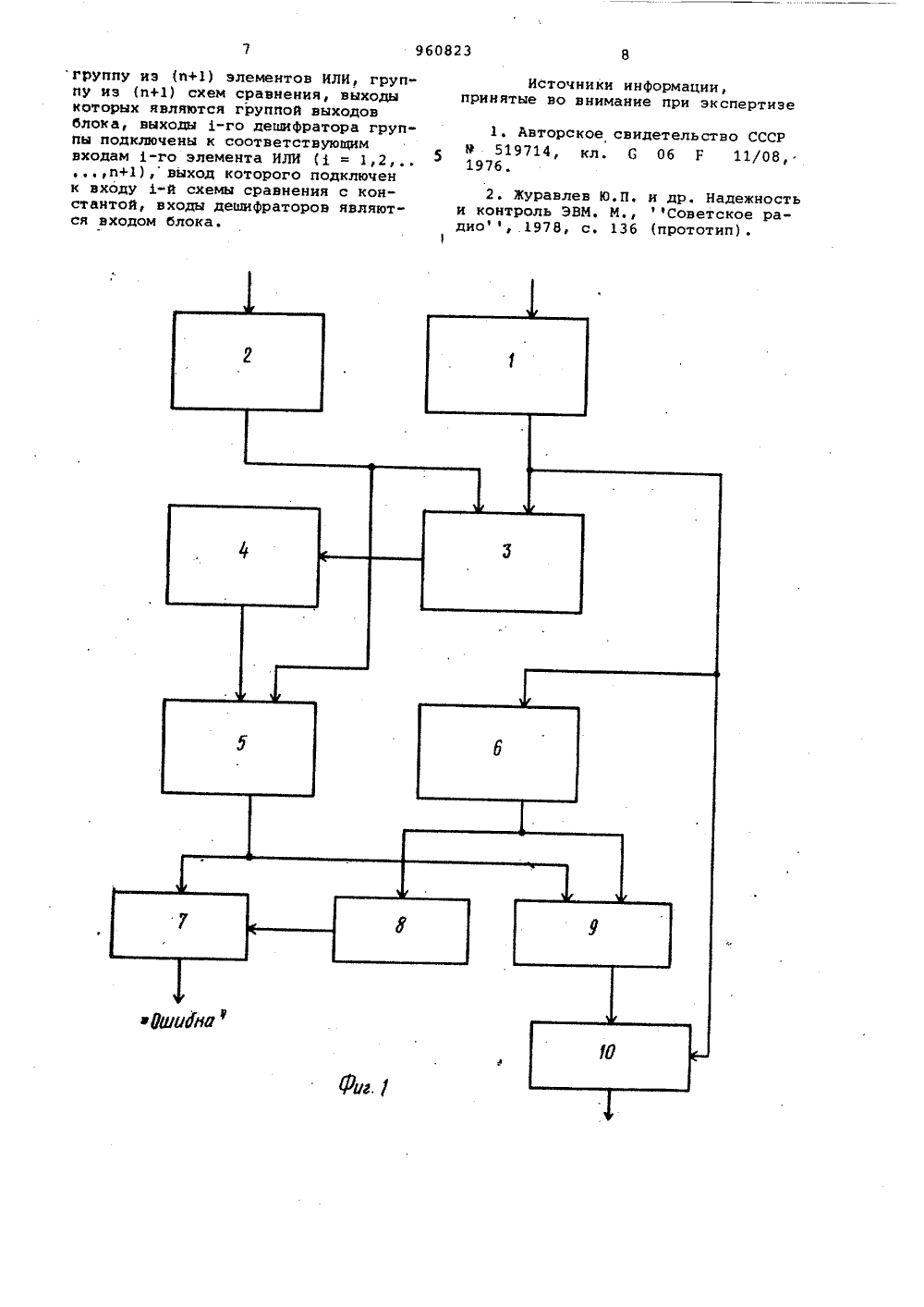

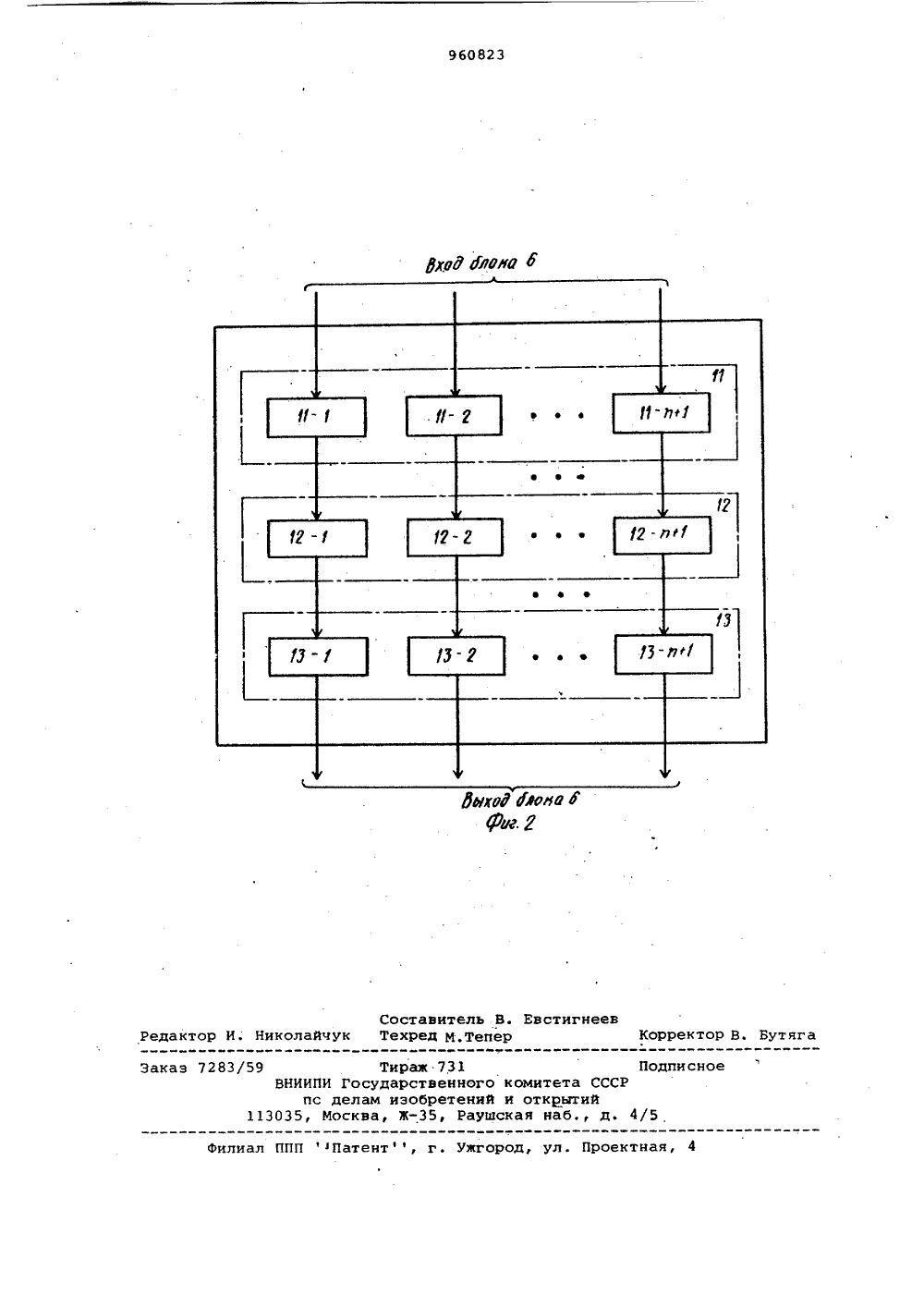

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик ц 960823(22) Заявлено 040880 (21) 2967296/18-24с присоединением заявки Мо(5) М. Кп.з С 06 Р 11/08 Государственный комитет СССР по делам изобретений и открйтий .(54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЬ 1 Х КЛАССОВ Изобретение относится к вычислительной технике и предназначено для обнаружения ошибок, возникающих в арифметическом устройстве ЭВМ в процессе вычислений.Известно устройство для обнаружения ошибок в системе остаточных классов, содержащее два блока памяти, три сумматора, три преобразователя в дополнительный код, сумматор по модулю Р первого уровня, два сумматора по модулям Р и Рк первого уровня, два сумматора по модулям Р и Рк второго уровня и блок формирования сигнала ошибки, причем ивходов устройства соединены с входами первого блока памяти, выходы которого связаны соответственно с входами сумматоров, выход .первого сумматора подключен к первому входу сумматора по модулю Ри первого уровня, второй вход которого через йервый преобразователь в дополнительный код соединен с и-м входом устройства, а выход - с входом второго блока памяти (11.В этом устройстве с помощью сумматоров и преобразователей, блоков ,памяти и сумматоров по контрольным модулям первого и второго уровней обеспечивается получение разностеймежду кодом контрольных частейслова и свертками кода информационной части слова по контрольным модулям Рк и Рк . Анализ полученныхразностей позволяет сформироватьсигналы о знаке числа, наличии ошибки в его представлении и выполнитьисправление ошибок определенногокласса. Но имеющаяся большая избыточность используется лишь для формирования указанных двух сигналов.Исправление ошибок при этом не производится.Наиболее близким к изобретениютехническим решениемявляется устройство для обнаружения ошибок всистеме остаточных классов, содержащее регистры информационной и контрольной частей слова, входы которыхявляются входами устройства, преобразователь кода иэ системы остаточных классов в позиционную систему счисления, блок свертки словапо контрольным основаниям, схемусравнения, первый вход которой подключен к .выходу регистра контрольной части слова, а второй - к выходублока свертки слова по контрольным ЗО основаниям, входом .подключенного квыходу преобразователя кода из системы остаточных классов в позицион-ную систему счисления, первый входкоторого подключен к выходу регистра информационной части слова, авторой - к выходу регистра контрольной части слова, выход схемысравнения является выходом устройства 2.Недостатком устройства являетсяотсутствие возможности исправления 1 Оошибок.Цель изобретения - расширениефункциональных возможностей устройства за счет обнаружения всех одиночных ошибок и исправления одиночных ошибок, не выводящих величинуконтролируемого числа за пределаИ+4диапазона Г 1 Р,Поставленная цель достигаетсятем, что устройство содержит блоквыделения ошибочного основания, элемент И, блок хранения поправок, сумматор, элемент ИЛИ-НЕ, причем выходсхемы сравнения подключен к первсмувходу элемента И и управляющемувходу блока хранения поправок, группа адресных входов которого объединена с соответствующими входами элемента ИЛИ-НЕ и подключена к группевыходов блока выделения ошибочногооснования, входы которого объединеныс ссответствующими входами первойгруппы входов сумматора и,подключены к соответствующим выходам регистров информационной и контрольной 35частей слова, вторая группа входовсумматора подключена к соответствующим выходам блока хранения поправок, второй вход элемента И подключен к выходу элемента ИЛИ-НЕ, выход 40сумматора является информационнымвыходом устройства, выход элементаИ является выходом Ошибкаф устройства.При этом блок выделения ошибочного основания содержит группу из(и+1) дешифраторов, группу из (и+1)элементов ИЛИ, группу из (и+1) схемсравнения, выходы которых являютсягруппой выхода блока, выходы 1-годешифратора группы подключены к соответствующим входам 1-го элементаИЛИ (3. = 1,2п+1), выход которого подключен к входу 1"й схемысраВнения с константой, входы дешифратЬров являются входом блока.На фиг.1 представлена блок-схемаустройства; на фиг.2 - схема блокавыделения ошибочного основания,Устройство содержит регистры 1и 2 инФормационной и контрольной 60частей слова, преобразователь 3 кода из системы остаточных классовв позиционную систему счисления,блок 4 свертки слова по контрольнымоснованиям, схему 5 сравнения, блок 65 б выделения ошибочного основания,элемент И 7, элемент ИЛИ-НЕ 8, блок9 хранения поправок, сумматор 10,группу дешифраторов 11, группу элементов ИЛИ 12, группу схем 13 сравнения.Блок 4 свертки слова по контроль.ным основаниям представляет собоймногоярусную схему, в каждом ярусекоторой установлены сумматор и умножитель (не показаны), К первымвходам сумматора каждого последующего яруса подключены выходы сумматорапредыдущего яруса, На вторые входысумматоров через умножители подключены разряды позиционного представления информационной части слова свыхода преобразователя 3Блок б выделения ошибочного основания преобразует вычеты по основаниям системы в унитарный код, который через элементы ИЛИ 12 поступает на входы схем сравнения 13, гдепроисходит его сравнение с константой -1. Если вычет по некоторомумодулю не имеет ошибки, на выходесхемы 5 сравнения по данному модулюсигнал равен нулю . Если вычет понекоторому модулю ошибочен или неправильно дешифрирован, на выходесхемы 5 сравнения по данному модулюсигнал равен единице,Блок хранения поправок 9 представляет собой, например, одностороннее запоминающее устройство, вкотором хранятся величины поправок.Адрес ячейки этого запоминающегоустройства задается кодами с выходов блока б выделения оажбочногооснования и схемы 5 сравнения,Сумматор 10 представляет собойнабор сумматоров, каждый из которыхобеспечивает сложение по соответствующему основанию вычетов, поступающих на его входы,Устройство. работает следующимобразом.На регистры 1 и 2 из арифметического устройства ЭВМ поступаетконтролируемый код слова, состояший из совокупности вычетов числапо контрольным и информационным основаниям. Информационная часть слова преобразуется в преобразователе3 в позиционный код, Цифры позиционного кода слова по мере их формирования подаются на блок 4, где вумножителях вычисляется произведение по контрольному основанию данной цифры позиционного кода слована величину произведений оснований,по которым Формирование цифр позиционного кода закончено, т.е. Формирование величиныгде а - 1-ая цифра позиционного кода слова;Р - л -ое информационное основание;Х)Р - нычисление вычета величиныкх по основанию Р .Полученная величина я; в 1-м сумматоре блока 4 суммируется с результатом сложения в (1-1)-м сумматоре, При этом в первом из сумматоров производится сложение кода нуля с вели- чиной В результате этого на ныходе последнего сумматора блока 4 формируется свертка по контрольному основаниюинформационной части слова, котораяв схеме 5 сравнения вычитается изкода контрольной части слова. Еслиэта разность равна нулю, сигналошибки не выдается, так как исходное число правильное и его коррекция не требуется. В этом случае навыходе блока 9 хранения поправокформируется нулевой вектор коррекции, к исходное число без изменениячерез сумматор 10 поступает на информационный выход устройства. Впротивном случае код на выходе схемы 5 сравнения совместно с кодомна выходе блока б выделения ошибочного основания используется дляФормирования адреса ячейки в блоке9 хранения поправок или формирования сигнала ошибки на выходах Ошибка устройства,При обнаружении ошибочного нычета н блоке б его выходные сигналысовместно с выходными сигналамисхемы 5 сравнения используются дляобращения в блок 9 хранения поправок.Считанная из блока 9 поправкав сумматоре 10 складывается с кодомкорректируемого слова. Скорректированное таким образом слово выдается на информационный выход устройства. Если на выходе схемы 5 сравнения сигнал ошйбки не равен нулю,а блохом б ошибочное основание необнаружено, то информация для исправления ошибки недостаточна, изблока 9 хранения поправок считывает-ся нулевой вектор коррекции и контролируемое слово выдается черезсумматор без изменения. При этомна выходе элемента ИЛИ-НЕ 8 формируется сигнал, который разрешаетвыдачу сигнала ошибки на выходыОшибка устройства через группуэлементов И 7.Предлагаемое устройство за счетболее рационального использованияимеющейся избыточности позволяет нетолько обнаруживать те ошибки, чтои известное, но и кооректировать наиболее вероятную группу ошибок при той же самой избыточности кода. Это дает возможность сократить среднее время восстановления ЭВМ, повысить коэффициент готовности и производительность ЭВМ.Формула изобретения10 1. Устройство для обнаружения иисправления ошибок в системе остаточных классов, содержащее регистрыинформационной и контрольной частейслова, входы которых являются соот ветстнующими входами устройства,преобразователь кода иэ системы остаточных классов в позиционную систему счисления, блок свертки словапо контрольным оснОваниям, схемусравнения, первый вход которой подключен к выходу регистра контрольнойчасти слона, а второй - к выходублока свертки слова по контрольнымоснованиям, входом подключенного квыходу преобразователя кода из системы остаточных классов в позиционную систему счисления, первый входкоторого подключен к выходу регистраинформационной части слова, авторой вход - к выходу регистраконтрольной части слова, о т л ич а ю щ е е с я тем, что, с цельюрасширения функциональных возможностей за счет обнаружения всех одиночных ошибок и исправления одиноч ных ошибок, не выводящих величинуконтролируемого числа за пределыи+лдиапазона П Р, оно содержит блок1:4выделения ошибочного основания, 40 элемент И, блок хранения поправок,сумматор, элемент ИЛИ-НЕ, причемвыход схемы сравнения подключен кпервому входу элемента И и .управляющему входу блока хранения поправок, ф 5 группа адресных входов которогообъединена с соответствующими входами элемента ИЛИ-НЕ и подключена кгруппе выходов блока выделения оши. бочного основания, входы которого у объединены с соответствующими входами первой группы входов сумматораи подключены к соответствующим выходам регистров информационной иконтрольной частей слона, втораягРуппа. входов сумматора подключенак соответствующим выходам блокахранения пойравок, второй вход элемента И подключен к выходу элементаИЛИ-НЕ, выход сумматора являетсяинФормационным выходом устройства, 6 О выход элемента И является выходомОшибка устройства2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок выделения ошибочного основания содер жит группу из (п+1) дешифраторов, 960823группу из (и+1) элементов ИЛИ, группу из (и+1) схем сравнения, вйходыкоторых являются группой выходовблока, выходы 1-го дешифратора группы подключены к соответствующимвходам 1-го элемента ИЛИ (1 = 1,2,п+1), выход которого подключенк входу 1-й схемы сравнения с константой, входы дешифраторов являются входом блока. Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР 9 519714, кл. С 06 Е 11/08, 1976.2. Журавлев (0.П. и др. Надежность и контроль ЭВМ. М., Советское радио, 1978, с. 136 (прототип)..г Составитель В. Евстигнеевк Техред М.Тепер ор И ко Ред орректор В. Бутяга Заказ 7283/ 1ного к омытений и откРаушская н одписи илиал ППП Патент ф, г . Ужгород, ул. Проектн 9 Тираж 7ВНИИПИ Государственпс делам иэобрет 13035, Москва, ж,а СССРытийд. 4/5

СмотретьЗаявка

2967296, 04.08.1980

ВОЕННАЯ ИНЖЕНЕРНАЯ РАДИОТЕХНИЧЕСКАЯ ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ И ОРДЕНА ОТЕЧЕСТВЕННОЙ ВОЙНЫ АКАДЕМИЯ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА ГОВОРОВА Л. А

ВАСИЛЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ГРИГОРЬЕВ СЕРГЕЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: исправления, классов, обнаружения, остаточных, ошибок, системе

Опубликовано: 23.09.1982

Код ссылки

<a href="https://patents.su/5-960823-ustrojjstvo-dlya-obnaruzheniya-i-ispravleniya-oshibok-v-sisteme-ostatochnykh-klassov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и исправления ошибок в системе остаточных классов</a>

Предыдущий патент: Устройство для контроля схем сравнения

Следующий патент: Устройство для контроля передачи информации между каналом и процессором

Случайный патент: Устройство для автоматической правки шлифовальных кругов