Устройство для вычисления оптимальных параметров микроэлектронных схем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

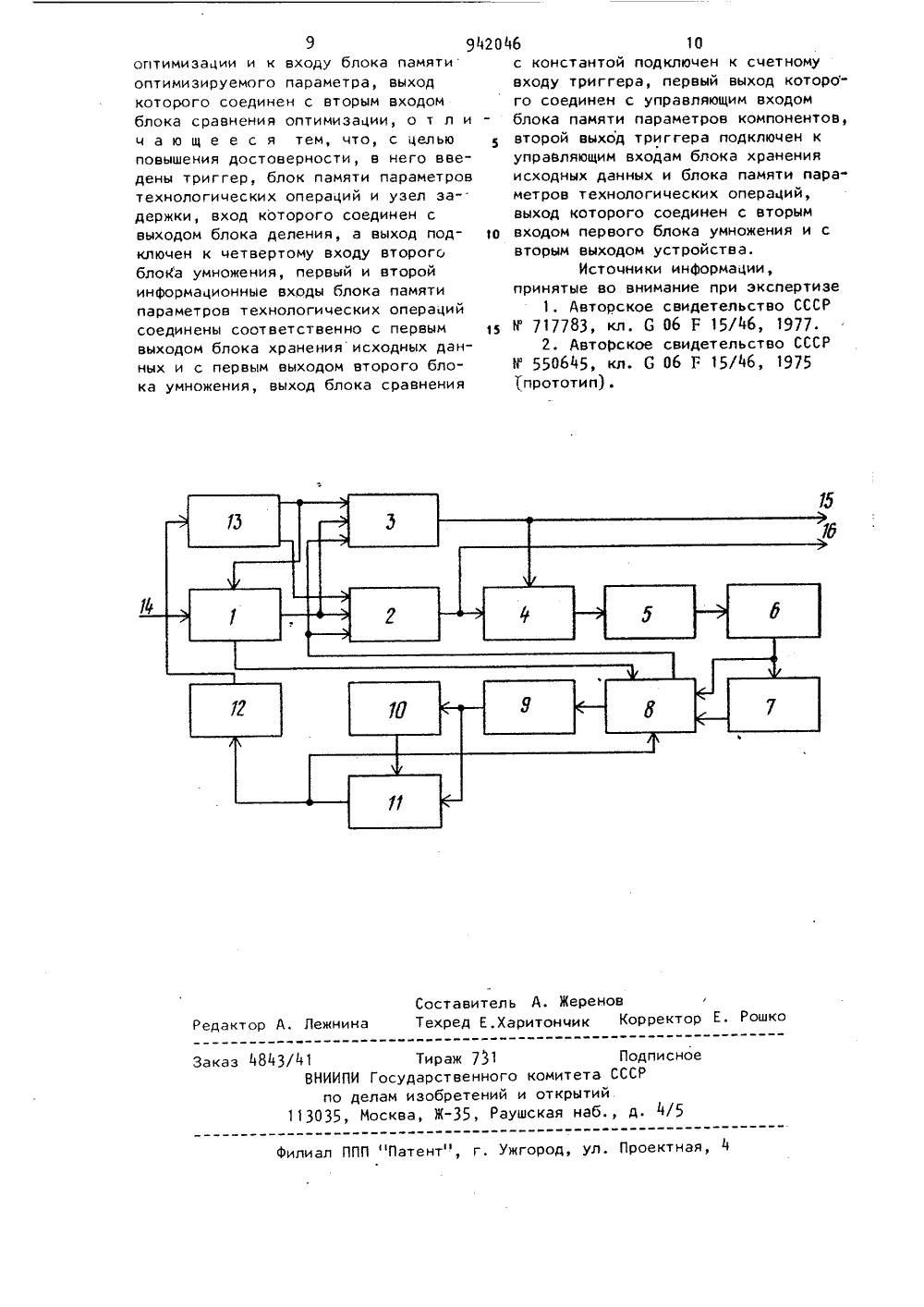

(23) Приоритетов С Об Р 15/6 Ьсударствснный квинтет во делан имбретаннй и открытийДата опубликования описания 07, 07. 82Харьковский ордена Ленина авиационный институт им. Н.Е.Жуковского(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ОПТИМАЛЬНЫХ ПАРАМЕТРОВ МИКРОЭЛЕКТРОННЫХ СХЕМ Изобретение о 1 ;, ится к вычис - лительной техн; ке и может оыть использовано для определения оптимальных параметров микроэлектронных схем при их разрабо-ке и проектировании.Известно у стройство, содержащее блок Формирования управляющих сигналов, генератор тактовых импульсов, распределитель опроса параметров модели, элементы коммутации, блоко физической модели, блок контроля выходных параметоов физической модели, блск памяти параметров отказов по параметрам, блок сдвиговых регистров, блок счетчиков Формирова 15 ния допусковой области, блок регистров коррекции положения допусковой области, блок выдачи команд проверки работоспособности 11 ). гоОднако в данном устройстве неучитываются особенности технологических операций подготавливаемых схем. Наиболее близким к предлагаемому по технической сущности является устройство, содержащее блок памяти, блок хранения матриц и последовательно соединенные блок регистрации, блок умножения, первый сумматор, блок деления, управляемый блок умножения, второй сумматор, блок сравнения и компаратор, причем первый выход блока хранения матриц подключен к второму входу управляемого блока умножения, а второй его выход связан с первым входом блока регистрации, вход блока хранения матриц подсоединен к входу устройства, второй выход управляемого блока умножения связан с вторым входом блока регистоации,выход второго сумматора подключен к входу блока памяти, выход:которого соединен с вторым входом блока сравнения, связанного по выходу с управляющим входомуправляемого блока умножения 21,Однако в данном устройстве недостаточно эффективно используется исБлок 1 предназначен для хранениярезультатов реализации матрицы плазонирования активного эксперимента,которые получают при изготовленииопытной партии микросхем.Блок 2 служит для записи частиданных матрицы, содержащейся в блоке1 и несущей информации о выходных55в- характеристиках и параметрах компонентов микросхемы, а также для запоминания текущих и окончательныхрезультатов оптимизации этой схемы. 3 с 142ходная информация, которая поступаетна вход и используется для построения регрессионной зависимости, связывающей выходные параметры схем ипараметры ее компонентов,Кроме того, в случае проектирования микроэлектронных схем этаинформация, обычно представляемаяв виде результатов реализации матрицы планирования активного эксперимента, который может быть легко реализован при изготовлении опытнойпартии проектируемых схем, содержитсведения не только о параметрах компонентов в выходных характеристикахсхемы, а также о статистических ифункциональных связях этих параметров и характеристик, но и об особенностях технологических операцийтехпроцесса изготовления этих схем,что никаким образом не учитываетсяв известных устройствах оптимизации.К этому следует также добавить, чтоизвестное устройство предполагает моделирование электронной схемы путемавтоматической сборки физическоймодели, а это практически неприемле-,мо при проектировании микроэлектронных схем, так как вносит большуюпогрешность в конечный результат изза неадекватности физической моделии реальной микросхемы.Цель изобретения - повышение достоверности получаемых результатовпри работе устройства.Поставленная цель достигается тем,что в устройство, содержащее блокпамяти оптимизируемого параметра,блок хранения исходных данных, первыйблок умножения, выход которого соединен с входом первого сумматора, выход которого соединен с входом блокаделения, второй блок умножения, второй сумматор, блок сравнения оптимизации," блок сравнения с константойи блок памяти параметров компонентов,выход которого соединен с первым входом первого блока умножения и с первым выходом устройства, информационный вход блока хранения исходных данных является входом устройства, первыйи второй выходы блока хранения исходных данных подключены соответственнок первому информационному входу блокапамяти параметров компонентов и кпервому входу второго блока умножениявторой вход которого и вход блока сранения с константой соединены с выходом блока сравнения оптимизации, третий вход второго блока умножения сое 046 фдинен с выходом блока деления, первыйвыход подключен к второму информационному входу блока памяти параметров компонентов, второй выход второго блока умножения соединен с входомвторого сумматора, выход которогоподключен к первому входу блока сравнения оптимизации и к входу блокапамяти оптимизируемого параметра,выход которого соединен с вторымвходом блока сравнения оптимизации,введены триггер, блок памяти параметров технологических операций иузел задержки, вход которого соединен с выходом блока деления, а выходподключен к четвертому входу второгоблока умножения, первый и второй информационные входы блока памяти параметров технологических операций соеодинены соответственно с первым выходом блока хранения исходных данныхи с первым выходом второго блока умножения, выход блока сравнения с константой подключен к счетному входутриггера, первый выход которого соединен с управляющим входом блока памяти параметров компонентов, второй выход триггера подключен к управляющим входам блока хранения исходных данных и блока памяти параметровтехнологических операций, выход которого соединен с вторым входом первого блока умножения и с вторым выходом устройства.На чертеже представлена схема35 предлагаемого устройства,Схема включает блок 1 храненияисходных данных, блок 2 памяти параметров компонентов, блок 3 памятипараметров технологических операций,40 блок 4 умножения, сумматор 5, блокб деления, узел / задержки, блок 8умножения, сумматор 9, блок 10 памяти оптимизируемого параметра, блок11 сравнения оптимизации, блок 1245 сравнения с константой, триггер 13,вход 14 и выходы 15 и 1 б устройства.Блок 3 предназначен для записичасти данных матрицы, содержащейсяв блоке 1 и несущей информацию о выходных характеристиках и параметрахтехнологических операций реализации 5микросхем, а также для запоминания-текущих и окончательных результатовоптимизации этих операций.Блок 4 умножения, блок 6 деленияи сумматор 5 служат для вычислениякоэффициентов уравнения регрессии.Узел 7 задержки предназначен длязадержки информации с выхода блокана время, равное времени вычисления оптимизируемого выходного параметра,Блок 8 умножения необходим дляопределения щагов изменения параметров при движении по градиенту оптимизируемой характеристики, 20Сумматор 9 предназначен для вычисления величины оптимизируемого выходного параметра на каждом шаге оптимизации,Блок 10 служит для запоминания 25значения оптимизируемого параметра,Блок 1 сравнения оптимизациипредназначен для сравнения оптимизируемого параметра на разных шагахоптимизации, зоБлок 12 сравнения с константойпредставляет собой пороговое устройство, состояние которого изменяется на противоположное, если входнойсигнал становится меньше определен 35ной наперед заданной величины,Триггер 13 предназначен для управления блоками 2 и 3, а также блоком 1.Рассмотрим работу устройства в случае, когда информация, поступающаяна его вход 14, представляет собойреализацию матрицы планирования активного эксперимента, полученную впроцессе проектирования пленочноймикросхемы, которое обычно включает45в себя и изготовление опытной партииэтих схем. Составление плана и реализация такого эксперимента в данномслучае предполагает, что варьируемыми параметрами, т.е, принудительно5 Оизменяемыми в процессе реализацииопытной партии микросхемы, являютсяне только параметры компонентов, нои параметры оптимизируемых технологических операцийДопустим, чтопараметром качества микросхемы служит 55один иэ ее выходных параметров, аоптимизируемой технологической операцией является операция, наиболее важня с точки зрения ее влияния на разброс параметров компонентов, Например, в случае пленочной технологиитакой операцией является напыление наподложку разистивного слоя. Задачаоптимизации решается данным устройством в два этапа. На первом этапеопределяется режим операции напыления, обеспечивающий минимальныйразброс параметров пленочных резисторов, Это и позволяет значительноулучшить результаты оптимизации навтором этапе, когда производитсяпараметрическая оптимизация микроэлектронной, схемы,Устройство работает следующим образом.При включении устройства блок 12находится в одном из устойчивых состояний, последнее устанавливаетсяпри воздействии на его вход начального выходного сигнала блока 11,который по величине значительно превышает порог опрокидывания блока 12за счет введения в блок 10 произвольной константы.Если блок 12 собран на базе логической схемы ИЛИ, то при вышеупомянутых условиях на ее выходе устанавливается логическая " 1", что, в своюочередь, установит триггер 13 в соСтояние, когда сигнал с его выходаоткрывает информационные входы блока3. При этом со входа 14 устройствав блок 1 поступает информация о результатах реализации матрицы планирования активного эксперимента, которая запоминается этим блоком. Одновременно с этим в блок 3 из блока 1переписывается часть хранящейся тамматрицы реализованного активного эксперимента, относящаяся к варьированиюпараметров оптимизируемой технологической операции. Далее эта информация последовательно поступает в блок4 умножения, сумматор 5 и блок 6 деления для вычисления коэффициентоврегрессионной зависимости, связывающей в нашем случае параметр качествас оптимизируемыми параметрами технологической операции. После этогоинформация с выхода блока 6 деленияпоступает на вход блока 8 умножения,а затем в сумматоре 9 определяетсяпараметр качества, значение которого заносится в блок 1 О вместо содержащейся там константы. Последниетри операции занимают время, равноезадержке, обеспечиваемой узлом 7задержки, после чего инФормация свыхода блока 6 д еле ни я ч -ре з задержки поступает также на ход блока 3 умножения. Б Везупьтэте зто,о в поспеднем определяются шаги пере. мещения по каждому .,з Г;араметров,Анформация постуГ 7 ает на вход ОлокаБ умножени я с вь 7 хОДВ Олока.,7 алееВ сумматоре Я определяются нозь 7 е 37 ацения параметров и новое 3 ацениепараметра кацества,. Вычислен, ое знаХОДИТ СРВВНЕНИЕ СтЭООГС :. 7 ОВОГО Значенлй параметра кацества, 7 здяисиМОсти от результата сравнения Гроиз Водится или короекция аззиетров в блоке 3 под воздействием и 1;ог 7 а ии о шагах, поступающей с вьхода блокд 8 умножения, и одновре мень ая корре ция шаГОВ путем Возд; йсВия выходнс го сигнапа блока .1 на вход бг;ока 3 в каждом цикле оптимиза.ии, и.г 7 и ращение процесса оптимзаци 7. Вслл вновь полученное значен:с паране;рд кацества отлицает я от Оанее вьц;-сленного на зеличину, н прев;7 шаюшуюпорога срабатывания бгок, 12. Р ГОследнем случае состояние блок: изменяется: в ;э поотивополо,ь 7 оо, т: 1 вы уа е= ппдб-.- 7 г д В сВОО Очередь ние триггера 13 ВПИРаНИЕ гм НГР ка "От пи рани блоа 7 и пере блока 1 аасти-у г пасаВиа ПИСЬ д ПОгпе,3 7 7 рЕ,77, . ,С 7 д аК 77 ВНО-О Зь -П в а р ь и о о = а н и.; п д рьм :. о :МИКРОСХЕМЫ . П)с ЛЕ аЕ 7да.: Гд Г . - . Второй зт ап ог.ГИМза,ии рлцес.:ая оптимизация,.Оо. - , .:Г, .7 оймикросхемы, Работа устройс Гва . Зто,СЛУЦаЕ Г 7 РОИСХОпнт адпо-ИННО на первом этапе с теь Г 7 Ишы ичи емцто на вцхопе -,л 7 Оэв КГ,-7 цо ПРОЦЕССа ОПТИМИЗдЦИЛ ПОЛУчав ;ПГ 7.маль 7 ные величины параме-ров:и росхемы, в то время гак на вцхоле бло Ка 3 ПОСЛЕ ОКОНЦаНИа ПЕРЯогО зтаПд ОПТИМИзаЦИИ ПОЛуцаЕМ ОПанап ьне, " 377 Ечения параметоов режима оп;имлзируемой технологической ,пердции.ОЦЕВИДНО, ЧтО ОПтИМИЗаЦИЯ ПВР 37 Етров оежимов технологлческлх Операций пОЗВОГ 7 яет значительно уменьГ 7 ить раз" брос параметров ком 7 онентов как в -:и ДЕЛаХ ОДНОЙ ПаРТИИ МИКООСХЕМ. Д;,чение параметра качества пола .тся В ОЛОКИ 1 0 И 1 1 Ядн 1 ПГЕ 7 ЕН, р ИМлющееся ранее в бпо;е 10 значение подается на вход блока 11., глс .- Пг,ос. от партлл к 7 артии, что, в свою очеред ь, вьзывае; уме 7 ьц 7 ение разбросов выходных параметров микросхем. Г 1 осколь 7 наряду с Зтим определяютсяогтимальнце параметры компонентов микросхемы, уже на зтапе реализацииВторой Г;артии микросхем можно получить улучшение их выходных характери:тик, значительно превышающее эффек от чисто парамстрической оптинизации компонентов, что как раз и обусловлено возможностью одновремен:-ого использования результатов опт 7 мизации и ОГ 1 ераций техпроцессаи ЯН,ТОЕННИХ ПВРаМЕтРОВ МИКРОСХЕМ.71: пользование Гредлагаемого устройства в автоматических системах управ ваЛЯ ПрОИЗВОдСТ ВОМ ЧИКрОЗЛЕКтрОННЫХ устройств позволит значительно улучшить технические характеристики последних, а также существенно повыситьпроцент выхода годных микросхем приих серийном роизводстве.Фонмула изобретенияУСТОЙСТВО ДЛЯ ВЬ 7 ЧИСЛЕНИЯ ОПТИМаЛЬНЫХ ГаРа 7 ЕТРОВ МИКРОЭЛЕКТРОННЫХ СХЕМ, содержащее блок пдмяти оптимизируемого пе:;аметра блок хранения исходных дан 7 цх, первый блок умножения, вьходвторого соединен с входом перВОГОсумматора вьход которого соединен с вд .м блока,пепения, второй блок ,.:МН 7 ожения, втооой су, атор, блок сравоптимиза 7 ии блок сравнения-1-с анпг" и бло ;амяти пдрамет -омг:.онен,ов, Выход которого соедиЕОВЬ 7 М ВХОпСМ ПЕРВОГО бЛОКа,;е:-ля ".:" Первь;м выходом устройсва, ин 77 ормачион ый вход блока храНЕН, Я ИСХОДНЬХ паН-ЫХ ЯВЛЯЕТСЯ ВХОДОМ.Йсгва, первь 7 й и второй выходы бГ 7 ока .ранения лсходных данных подлючены соответствено к первому инбгГма 7 ионному вхоп блока памяти парам-трс,в компонентов и . первому входу в-орого . лока умножения второй вход к. - Орого и вхоп блока сравнения с константойй соединень с выходом блока срав:- ения опт 7 лмизации, Гретий вход водого блока умно 77 ения соединен с выходом блока деления, первый выход подклсцен к ворсму информационному входу блока памяти параметров компонентов второй выход второго блока умножения соединен с входом Второго суммаГора, выход орого подключенпервому входу б.7 ока сравненияСоставитель А. ЖереновТехред Е.Харитончик Корректор Е. Рошко Редактор А. Лежнина Заказ 4843/41 Тираж 731 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб., д 4/5 филиал ППП "Патентн, г. Ужгород, ул. Проектная,оптимизации и к входу блока памятиоптимизируемого параметра, выходкоторого соединен с вторым входомблока сравнения оптимизации, о т л ич а ю щ е е с я тем, что, с цельюповышения достоверности, в него введены триггер, блок памяти параметровтехнологических операций и узел за-.держки, вход которого соединен свыходом блока деления, а выход подключен к четвертому входу второгоблока умножения, первый и второйинформационные входы блока памятипараметров технологических операцийсоединены соответственно с первымвыходом блока хранения исходных данных и с первым выходом второго блока умножения, выход блока сравнения 42046 1 Ос константой подключен к счетномувходу триггера, первый выход которо- го соединен с управляющим входомблока памяти параметров компонентов,второй выход триггера подключен куправляющим входам блока храненияисходных данных и блока памяти параметров технологических операций,выход которого соединен с вторым1 в входом первого блока умножения и свторым выходом устройства.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРй 717783, кл, С 06 Е 15/46, 1977.2. Авторское свидетельство СССРй 550645, кл. С 06 Г 15/46, 19757 прототип).

СмотретьЗаявка

3221659, 30.10.1980

ХАРЬКОВСКИЙ ОРДЕНА ЛЕНИНА АВИАЦИОННЫЙ ИНСТИТУТ ИМ. Н. Е. ЖУКОВСКОГО

КОЛПАКОВ ФЕДОР ФЕДОРОВИЧ, МИЛЬКЕВИЧ ЕВГЕНИЙ АЛЕКСЕЕВИЧ, ШЕВЕЛЕВ ВЛАДИМИР АЛЕКСЕЕВИЧ, СЫЧЕВ АЛЕКСЕЙ ЕГОРОВИЧ

МПК / Метки

МПК: G06F 17/00

Метки: вычисления, микроэлектронных, оптимальных, параметров, схем

Опубликовано: 07.07.1982

Код ссылки

<a href="https://patents.su/5-942046-ustrojjstvo-dlya-vychisleniya-optimalnykh-parametrov-mikroehlektronnykh-skhem.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления оптимальных параметров микроэлектронных схем</a>

Предыдущий патент: Устройство для прогнозирования надежности

Следующий патент: Пневматический нелинейный преобразователь

Случайный патент: Подъемное устройство