Преобразователь двоичных чисел в двоично-десятичные

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

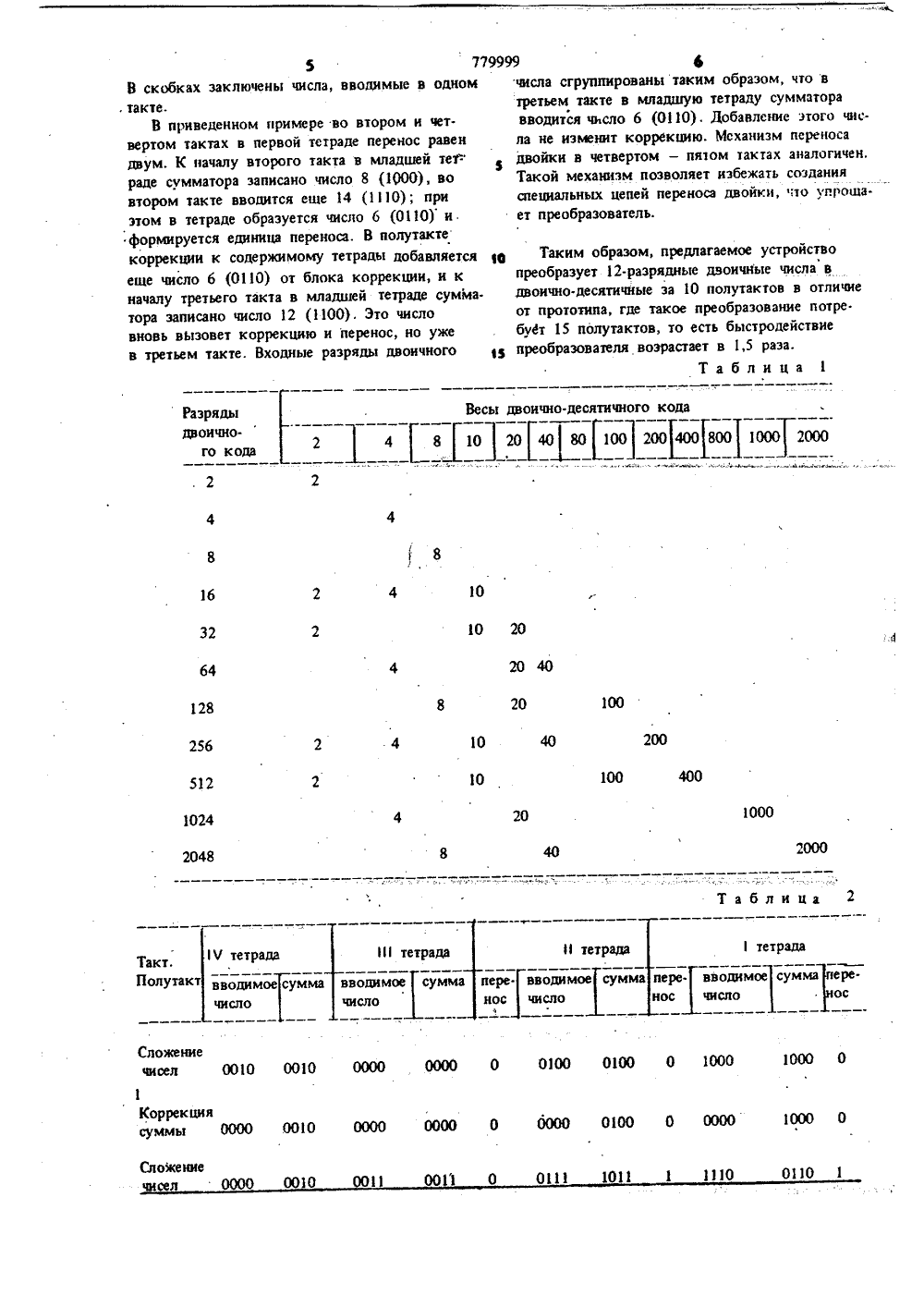

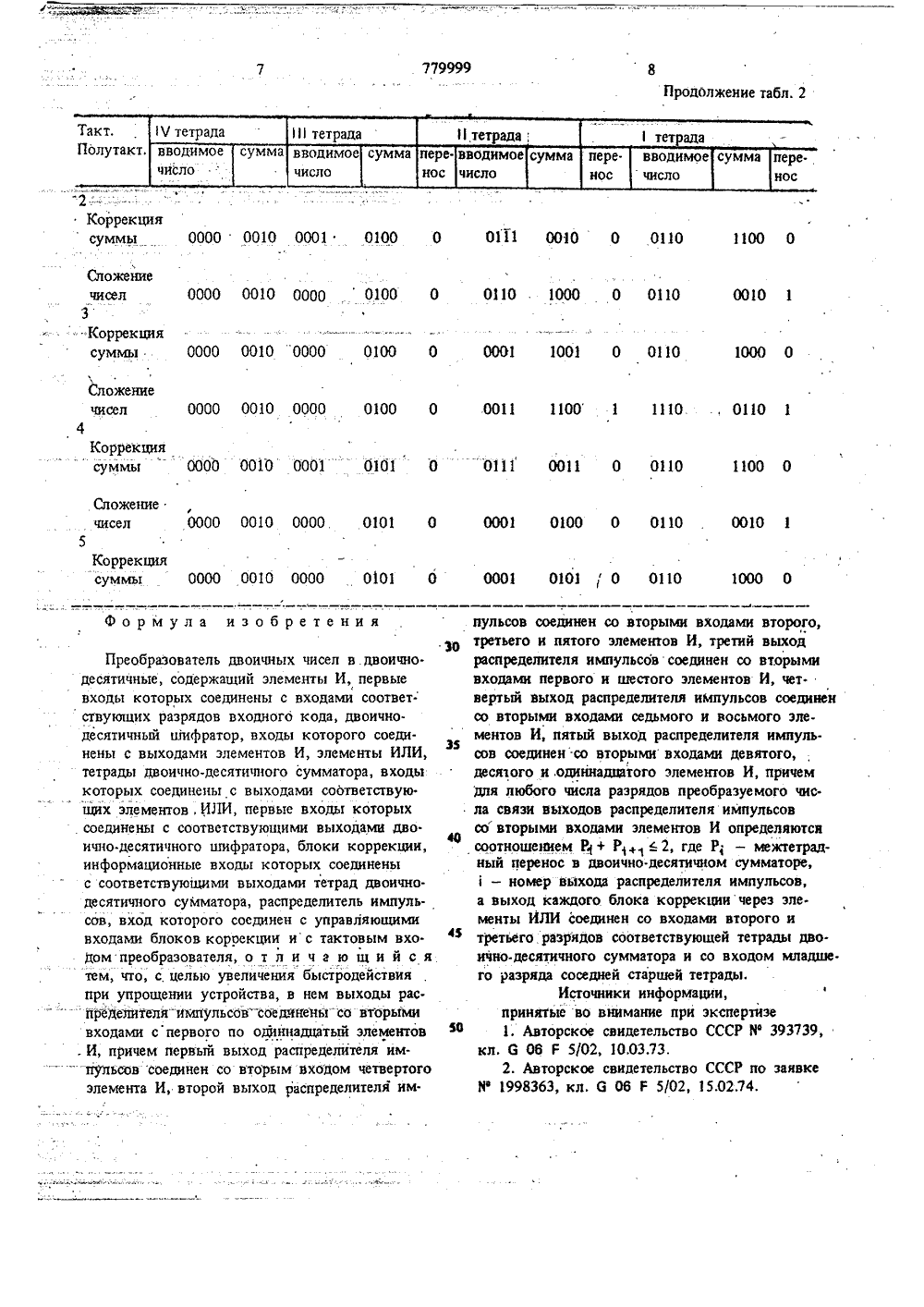

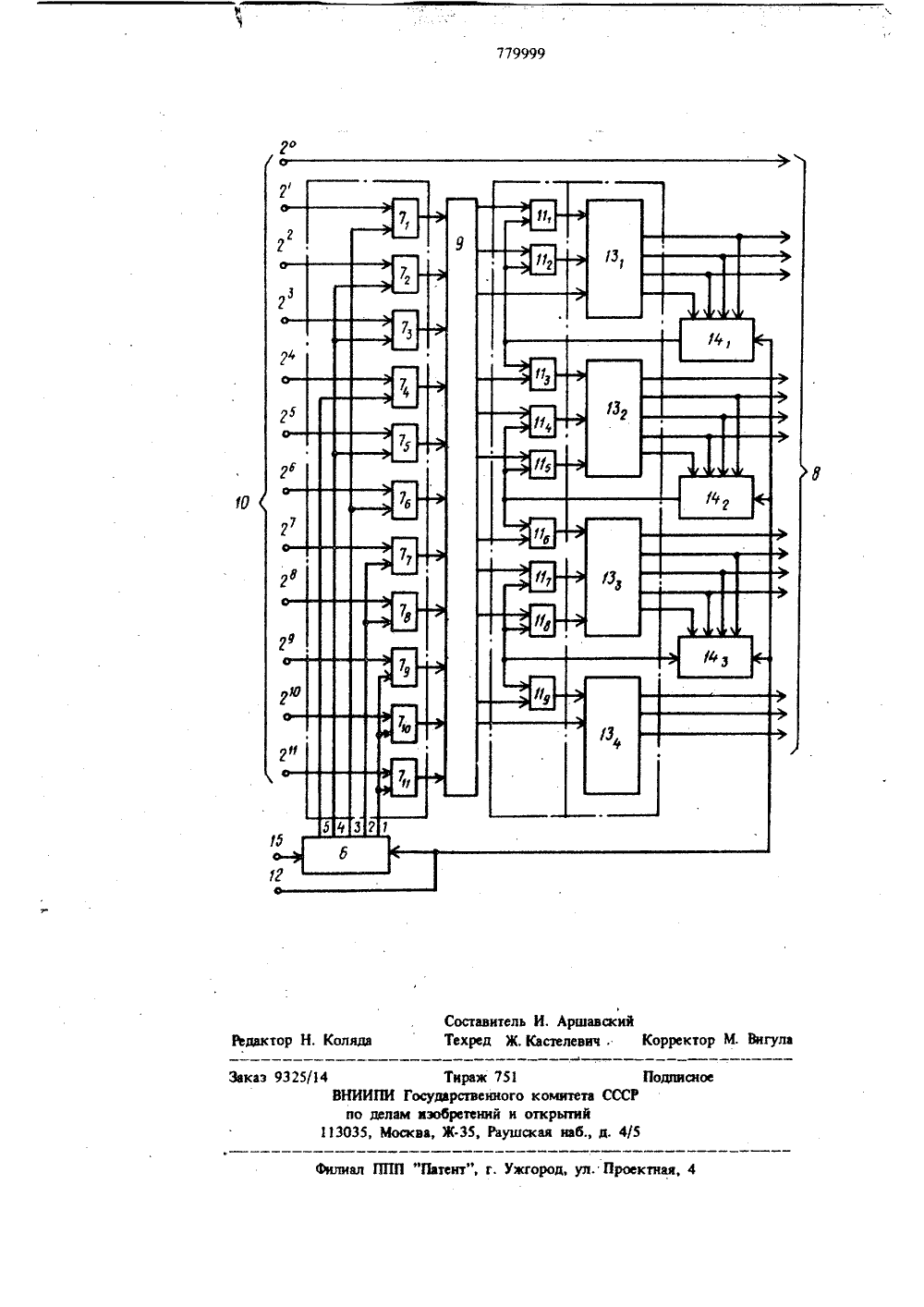

Оп ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1779999 Союз СоветскихСоциалистическихреспублик(51)М. Кл. 6 06 Е 5/02 ВЬфуаарстеенный комитет СССР в дюлак изюбретеииЯ и ютхрытиЯ(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНЫХ ЧИСЕЛ В ДВОИЧНО - ДЕСЯТИЧНЫЕ 1 зобретение относится к области автоматикии вычислительной техники и может быть испольэовано при построении двоично-десятичных пре.обраэователей,Известен преобразователь двоичных чисел в3двоично.десятнчные 1), содержащий группуэлементов И, шифратор эквивалентов, накопи.тельный сумматор и распределитель импульсов.Недостаток этого преобразователя состоит в низ.ком быстродействии, связанном с последовательной обработкой разрядов,Наиболее близким решением данной задачипо технической сущности и схемному решениюявляется преобразователь двоичных чисел в двоично.десятичные 2), содержащий элементы И, пер 1вые входы которых соединены с входами соответствукнцих разрядов входного кода, двоично.десятичный шифратор, входы которого соединеныс выходами элементов И, элементы ИЛИ, тет)1 адыдвоично-десятичного сумматора, входы которыхсоединены с выходами соответствующих элемен.тов ИЛИ, первые входы которых соединены ссоответствующими выходами двоично-десятичногошифратора, блоки коррекции, информационные входы которых соединены с соответствующими выходами тетрад двоично-десятнчного сумматора, распределитель импульсов, вход которого соединен с управляющими входами блоков коррекции и с тактовым входом преобразователя.Недостаток этого преобразователя так же сос. тоит в относительно низком быстродействии, связанном с возможностью многократного возникновения межтетрадного переноса.Целью изобретения является увеличение быст. родействня при упрощении устройства.Поставленная цельдостигается тем, что в преобразователе двоичных чисел в двончно.десятнч. ные, содержащем элементы И, первые входы которых соединены с входами соответствующих разрядов входного кода, двоично.десятичный шифратор, входы которого соединены с выхода./ми элементов И, элементы ИЛИ, тетрады двоично-десятичного сумматора, входы которых сое. динены с выходами соответствующих элементов ИЛИ, первые входы которых соединены с соответствующими выходами двоично-десятичного шифратора, блоки коррекции, ннформационньге входы которых соединены с соответствующими3 77Выходами тетрад двоично-десятичного сумматора,распределитель импульсов, вход которого соединен с управляющими входами блоков коррекциии с тактовым входом преобразователя, выходыраспределителя импульсов соединены со вторымивходами с первого Yо одиннадцатый элементов И,причем первый выход распределителя импульсовсоединен со вторыми входами четвертого элемен.та И, второй выход распределителя. импульсовсоединен со вторыми входами второго, третьегои.пятого элементов И, третий выход распределителя импульсов соединен со вторыми входамипервого и шестого элементов И, четвертый выход распределителя импульсов соединен со вторыми входами седьмого и восьмого элементовИ, пятый выход распределителя импульсов соединен со вторыми входами девятого,десятогои одиннадцатого элементов И, причем для любого числа разрядов преобразуемого числа связивыходов распределителя импульсов со вторымивходами элементов И соотношением Р + Р, (2,1+1где: Р; . межтетрадный перенос в двоично-десятичном сумматоре,- номер выхода распределителя импульсов, а выход каждого блока коррекции через элементы ИЛИ соединен со входа.ми второго и третьего разрядов соответствующей тетрады двоично-десятичного сумматора исо входом младшего разряда соседней старшейтетрады,9999 4если они имеются, поступают в двоично-десятич.ный шифратор 9, и сигналы с соответствующихвыходов шифратора черезэлементы ИЛИ 11 подаются на входы тетрад двоично-десятичногосумматора 13, В этом же полутакте происходитвыявление корректен и переносов блоками коррекции 14 - 14, которые формируют и запоминают сигнал коррекции, если число, записанноев соответствующей тетраде сумматора большеили равно десяти,сБлок коррекции реализует логическую функцию,К = (Я Ч Я )БЧР,где.Я, Я 4, Яо - выходы 2, 2, 2 тетрады15 соответственно;Р - выход переноса тетрады;К - сигнал коррекции.Коррекции суммы и сложения переносовв первом полутакте не происходит, поэтому20 сигнал коррекции запоминается до начала полутакта коррекции.Коррекция суммы и сложение переносовосуществляется добавлением числа шесть (0110)к содержимому тетрады сумматора, и добав 25 лением единицы переноса к содержимомуследующей старшей тетрады. Выявление коррекции и переносов в полутакте коррекции непроисходит,На этом заканчивается первый такт преобра.ЗО зования. В оставшиеся четыре такта преобразователь действует аналогично,Предлагаемая группировка входных инфор.мационных шин исключает одновременную подачу двух сигналов на один вход сумматора.Распределение весов двоично-десятичногокода по разрядам двоичного кода приведено втабл. 1,На чертеже представлена функциональная схе.ма устройства,Оно содержит выходы 1.5 распределителя импульсов 6, элементы И 7 - 7 ввода разрядов1 11с первого по одиннадцатый входного числа с1 1весами 22 соответственно, выходы 8 преобразователя, двоично.десятичный шифратор 9, входы 10 двоичного числа, элементы ИЛИ 11 - 11вход 12 тактовых импульсов, тетрады 13 - 1341двоично-десятичного сумматора, блоки коррек.ции 14 - 14, вход 15 импульса начала преобразования.Каждый такт преобразования состоит из двухполутактов. В первом полутакте (в течение так.тового импульса) производится ввод числа,запись его в сумматор, выявление коррекциии переносов схемами коррекции, Во второмполутакте (в течение паузы между тактовымиимпульсами) производится коррекция числазаписанного в сумматоре.Преобразование происходит следующим образом, Повходу 15 в устройство поступаетимпульс начала преобразования, запускающийв распределитель 6 импульсов, который форми.рует пять импульсов опроса, последовательновозникающих на его выходах. При возникновении первого импульса на выходе распределителя импульсов б открьпзаются три элементаИ 79, о, 7 соответствующие разрядам 2,2 О 2. Единицы со входов 10 этих разрядов,Каждый столбец таблицы соответствуеткакому. либо входу сумматора. Числа, стоящие0 в одном столбце, должны подаваться в сумма.тор в разные такты, Из таблицы видно, чтодля 12-разрядного числа минимально возмож.ное число тактов - пять,Другая особенность предлагаемого преобраэо.45 вателя заключается в следующем: если в про.цессе преобразования в каком-то такте перенос равен двум, то в следующем такте пере.нос в данной тетраде отсутствует; это позво.ляет распространять перенос, равный двум, эа50 два такта преобразования без усложнения уст.ройства,В табл. 2 в качестве примера, поясняющего особенности работы преобразователя, расписано55 по полутактам преобразование числа 2558. 2558 - (2048) +(256+128) + (64+2) + (32+8+4) +Весы двоично-десятичного кода Разряды двоично.го кода 2 4 8 10 20 40 80 100 200 400 800 1000 2000 1 8 16 32 10 20 64 128 20 10 256 10 512 1024 1000 20 2048 Таблица 2 1 тетрада 1 тетрада 111 тетрада ЧЧ тетрада Такт.Полутактпере- вводимое сумма ере. нос число ос пере. вводимое сумма нос число мма вводимое сумма вводимчисло число 00 0000 0 Сложени чисел 10000 0000 0 0100 0100 0 100 0010 00 оррексуммы 0000 0100 0000 0010 0000 00 ениел 0000 110 0 11 1 0111 0 0011 5 779999 4 В скобках заключены числа, вводимые в одном числа сгруппированы таким образом, что в . такте. третьем такте в младшую тетраду сумматораВ приведенном примере во втором и чет. вводится чьсло 6 (0110). Добавление этого чисвертом тактах в первой тетраде перенос равен ла не изменит коррекцию. Механизм переноса двум. К началу второго такта в младшей тет". двойки в четвертом - пятом тактах аналогичен.5раде сумматора записано число 8 (1000), во Такой механизм позволяет избежать создания втором такте вводится еще 14 (1110); при специальных цепей переноса двойки, что упроща. этом в тетраде образуется число 6 (0110) и ет преобразователь. формируется единица переноса. В полутактекоррекции к содержимому тетрады добавляется р Таким образом, предлагаемое устройство еше число 6 (0110) от блока коррекции, и к преобразует 12-разрядные двоичные числа в началу третьего такта в младшей тетраде сумма- двоично-десятичные за 10 полутактов в отличие тора записано число 12 (1100). Это число от прототипа, где такое преобразование потре. вновь вызовет коррекцию и перенос, но уже . будт 15 полутактов, то есть быстродействие в третьем такте. Входные разряды двоичногопреобразователя возрастает в 1,5 раза.Таблица 1779999 7 Продолжение табл. 2тетрада;тет ада ТактПЧ тетрадатетрада олутакт вводимое сумма вводимое суммачислочисло пере. вводимое сумманос число пере. вводимое сумма пере.нос число нос 2Коррекциясуммы 0000 0010 0001 0100 0 0111 0010 0 0110 1100 0 Сложениечисел3Коррекциясуммы 0000 0010 ОООО0100 0 0110 1000 0 0110 0010 1 0000 0010 0000 0100 0 0001 1001 0 0110 1000 0 Сложение чисел4 0000 0010 0000 0100 0 0011 1100 1 1110 ., 0110 1 Коррекциясуммы 0000 0010 00010101 0 0111 0011 0 0110 1100 0 Сложениечисел 0000 0010 0000. 0101 0 0001 5 0100 0 0110 , 0010 1 0000 0010 0000 0101 О 0001 0101 , 0 0110 Коррекциясуммы Формула изобретения Преобразователь двоичных чисел в. двоично.десятичные, содержащий элементы И, первыевходы которых соединены с входами соответствующих разрядов входного кода, двоичнодесятичный шифратор, входы которого соеди.иены с выходами элементов И, элементы ИЛИ,тетрады двоично-десятичного сумматора, входыкоторых соединены с выходами соответствующих элементов, ИЛИ, первые входы которыхсоединены с соответствующими выходами дво.ично-десятичного шифратора, блоки коррекции,информационные входы которых соединеныс соответствующими выходами тетрад двоичнодесятичного сумматора, распределитель импульсов, вход которого соединен с управляющимивходами блоков короекции и с тактовым вхо.дом преобразователя, о т л и ч а ю щ и й с ятем, что, с целью увеличения быстродействияпрн упрощении устройства, в нем выходы рас. "пределителя импульсовсоедннены "со вторымивходами с первого по одиннадцатый элементов, И, причем первый выход распределйтеля им- пульсов"соединен со вторым входом четвертогоэлемента И, второй выход распределителя импульсов соединен со вторыми входами второго,третьего и пятого элементов И, третий выходраспределителя импульсов соединен со вторымивходами первого и шестого элементов И, чет.вертый Выход распределителя импульсов соединенсо вторыми входами седьмого и восьмого элементов И, пятый выход распределителя импуль 35сов соединенсо вторыми входами девятого,десятого и,одиннадцатого элементов И, причем;для любого числа разрядов преобразуемого чис.ла связи выходов распределителя импульсовсо вторыми входами элементов И определяютсясоотношением Р+ Р+ 2, где Р; - межгетрадный перенос в двоично.десятичном сумматоре,- номер выхода распределителя импульсов,а выход каждого блока коррекции через эле.менты ИЛИ соединен со входами второго иф третьего разрядов соответствующей тетради двоично.десятичного сумматора и со входом младше.го разряда соседней старшей тетрады.Источники информации,принятые во внимание при экспертизезО 1, Авторское свидетельство СССР Иф 393739,кл. 6 06 Р 5/02, 10,03,73.2. Авторское свидетельство СССР по заявкеИе 1998363, кл. 6 06 Р 5/02, 15,02.74., Раушская наб., д. 4/5 одни сное Па аз 9325/14 ТираВНИИПИ Госуда по делам иэобре113035, Москва, Ж.З г. Ужгород, ул, Проектная, 4

СмотретьЗаявка

2576404, 02.02.1978

ПРЕДПРИЯТИЕ ПЯ М-5973

ВАКУРОВ ВЛАДИМИР ФИЛИППОВИЧ, МАРДЕР АЛЕКСАНДР ХАИМОВИЧ, ОЛЬШТЕЙН ЕФИМ ИЦКОВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоично-десятичные, двоичных, чисел

Опубликовано: 15.11.1980

Код ссылки

<a href="https://patents.su/5-779999-preobrazovatel-dvoichnykh-chisel-v-dvoichno-desyatichnye.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоичных чисел в двоично-десятичные</a>

Предыдущий патент: Преобразователь кодов

Следующий патент: Преобразователь двоичного кода в двоично-десятичный код градусов, минут, секунд

Случайный патент: Устройство для размещения кольцеобразных заготовок