Линейный интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

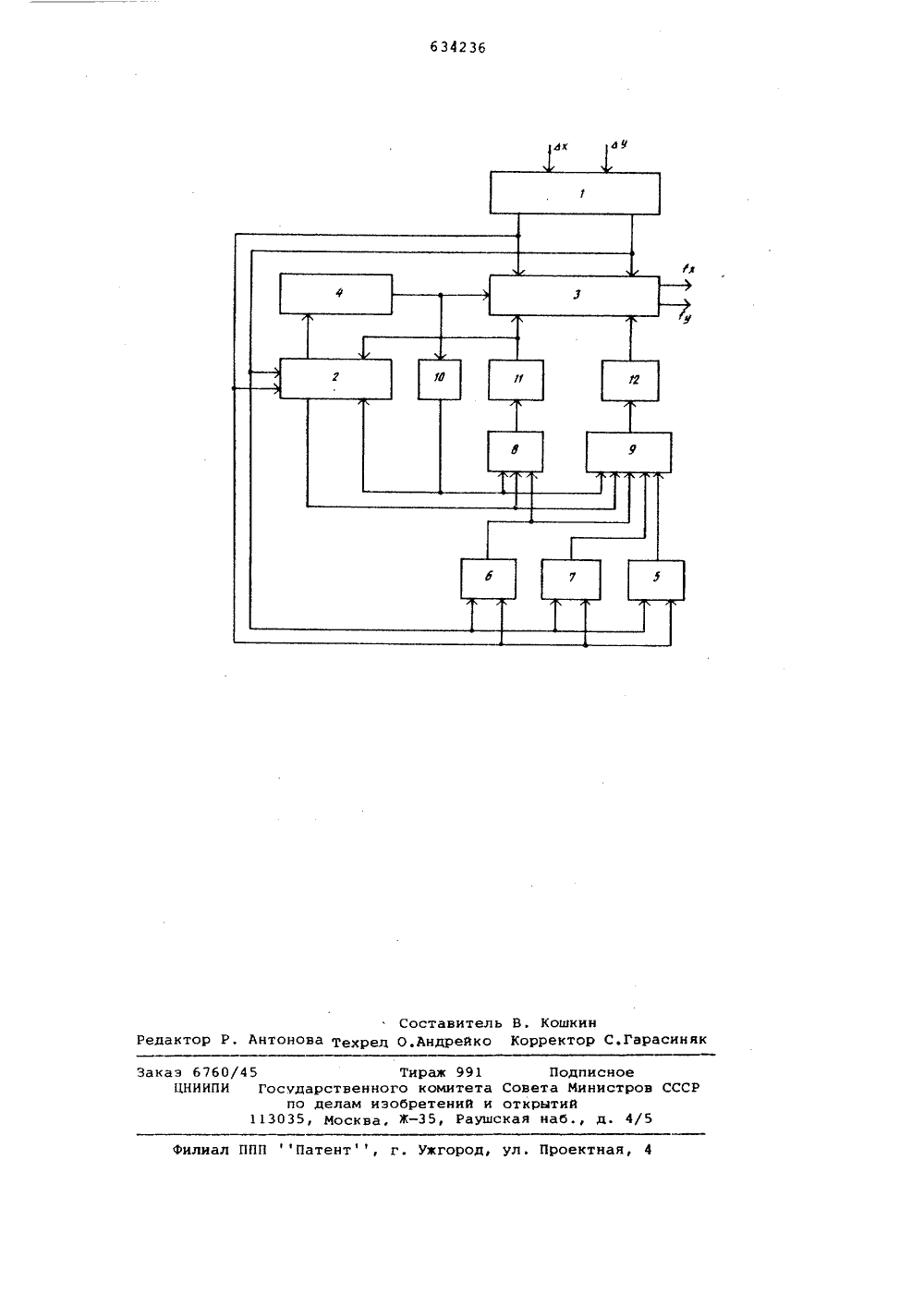

пн 634236 ОПИСАНИЕ ИЗОБРЕТЕНИЯ Союз Советскка Соцкаписткческих Реепубпнк(51) М. Кл рнсоединением заявки 7 та Го Со дарственны та Миннст делам изои откры и комитет ов СССР ретеиийий ори тет о) УД 43) Опубликовано 25.1178, бюллетень РЙ 43 45) Лата опубликования описания 30,11.78 1503(71) Заявитель Киевский технологический институт легкой промышленности(547 ЛИНЕЙНЫЙ ИНТЕРПОЛНТОРния ос- ает ие относится к и управления к рабочих орган и может быть х числового и ого интерполяпо координатемаксимальному Изобретен области автоматизаци онтурньм перемещением ов станков и агрегатов использовано в система рогоаммного 5 управления.Известны линейные интерполяторы, содержащие генератор тактовых импульсов, регистры координатных перемещений, делитель частоты, логические 10 схемы, выдающие импульсы интерполирования по соответствующим координатам и схему, обеспечивающую повышение скорости интерполирования путем укорачивания делителя частоты на число 15 разрядов, равное количеству нулей перед первым старшим значащим разрядом большего приращения 11, 2 .Наиболее близким техническим решением к изобретению является линей- ф 1 ный интерполятор, содержащий последовательно соединенные блок управления, делитель частоты, первый блок сравнения и блок регистров, выходы которого подключены ко входам блока 25 управления и первого блока сравнения131 .Недостатком известитора является то, чтос большим,но не равным приращением импульсы интерполирова выдаются не при каждом изменении с тояння делителя частоты, что сниж частоту интерполирования.Цель изобретения - повышение быстродействия линейного интерполятора на импульсных умножителях, таким образом, чтобы, путем изменения коэФФициента пересчета делителя частоты в зависимости от величины большего координатного приращения, обеспечить выдачу импульсов интерполирования по координате с большим прира щением при каждом изменении состояния делителя частоты.Для достижения указанной цели в ннтерполятор введены второй блок срав нения, гервый и второй элементы И, первый и второй триггеры и элемент НЕ, первый и второй блоки определения нулевых разрядов координатных приращений, входы которых и вход второго блока сравнения подключены к выходам блока регистров, выход первого блока определения нулевых разрядов координатных приращений подключен к входам первого и второго элементов И, два других входа которых присоединены к выходу блока управления и через элемент НЕ, к выходу делителя частоты, выходы второго блока сравненияи второго блока определения нулевыхразрядов координатных приращений присоединены к входам второго элементаИ, выходы первого и второго элементов И подключены к входам первого ивторого триггеров, выходы которых соединены с соответствующими входамипервого, блока сравнения, выход первЬго триггера соединен также со входом блока управления, другой вход которого подключен к выходу элемента ОНЕНа чертеже представлена схема линейного интерполятора, на которой показаны блок регистров 1, блок управления 2, первый блок сравнения 3,делитель частоты 4, второй блок сравнения 5, первый и нторой блоки определения нулевых разрядов координатныхприращений б и 7 соответственно,первый и второй элементы И 8 и 9, эле мент НЕ 10 и первый и второй триггеры 11 и 12 .Блок регистров 1 служит для хранения и последовательной выдачи значенийразрядон координатных приращений ивыполнен на динамических регистрах.Блок управления 2 формирует управляющие сигналы для делителя частоты 4и элементов И 8 и 9, Для делителячастоты 4 блок управления 2 вырабатывает сигнал на изменение его состоя-ЗОния, а для элементон И 8 и 9 вырабатывает сигнал управления, позволяющийопределить разряд делителя частоты 4,в котором произойдет переход из 0в 1 , если в следующем цикле прибавить 1 к разряду делителя частоты 4, соответствующему старшему значащему разряду приращений.Первый блок сравнения 3 по резуль татам анализа состояний первого и вто- рого триггеров 11 и 12, делителя частоты 4 и разрядов координатных приращений блока регистров 1 Формирует сигналы интерполирования по координатным осям.45Делитель частоты 4 выполнен на динамическом регистре по схеме сдвиговый регистр - сумматор и определяет разряд, в котором возможна выдача импульса интерполирования (то50 есть переход разряда из нулевого состояния в единичное) .Второй блок сравнения 5 производит сравнение старших значащих разрядов приращений.Первый блок определения нулевых разрядов координатных приращений б определяют нулевые разряды большего приращения. 60Второй блок определения нулевых разрядов координатных приращений 7 определяет нулевые разряды меньшего приращения, а на выход выдает инвертированный сигнал. 65 Элементы И 8 и 9 Формируют логические условия для того, чтобы установить в единичные состояния первый и второй триггеры 11 и 12 соответственно.Первый триггер 11 запоминает признак, что импульс интерполирования не может быть выдан в следующем цикле при прибавлении 1 - младшему значащему разряду делителя частоты 4.Второй триггер 12 запоминает состояние, когда н одном цикле интерполирования по координате с меньшим приращением требуется выдать два импульса интерполирования: один по единичному значению первого триггера 11, а второй - по переходу разряда делителя частоты 4 из 0 в 1 и наличию 1 н соответствующем разряде. меньшего приращения.Перед началом работы н блок регистров 1, построенных на динамических регистрах, ннодится информация о величинах приращений по координатам Х иСтаршие разряды приращений соответствуют младшему разряду делителя частоты 4, построенному на динамическом регистре. В процессе интерполирования информация о величинах координатных приращений не изменяется.Изменять состояние делителя частоты 4 разрешается блоком управления2 с тактовой частотой т тактпо началу динамического регистра. ПРи этом частота сдвига 1 дн инфоР- мации н динамическом регистре значительно выше тактовой частоты т :т. ( ( ттакт тактсан,По принципу работы интерполятора на импульсных умножителях импульсы интерполиронания могут выдаваться при переходе любого разряда делителя частоты 4 из состояния 0 н состояние 1 и наличии 1 в соответствующих разрядах координатных прираще- ний блока регистров 1. Для обесгечения выдачи импульов интерполирования по координате с большим приращением при каждом изменении состояния делителя частоты 4, пропускаются те его состояния, в которых импульсы интерполирования по этой координате не выдаются. При нулевых значениях старших разрядов координатных приращений блок управления 2 не выдает сигнала на прибавление 1 в делитель частоты 4, а переходит к оценке следующего разряда приращений. При появлении первого значащего старшего разряда приращений на выходах блоков регистра 1, блок упранления 2 прибавляет 1 к разряду делителя частоты 4, соответствующему этому разряду большего координатного приращения (младший значащий разряд делителя частоты 4). В этом же цикле интерполирования определяется, 634236может ли произойти выдача импульса интерполирования по координате с большим приращением при прибавлении в следующем цикле интерполирования 1 к младшему значащему разряду делителя ча.:тоты 4 (т.е. соответствует ли разряду делителя частоты 4, в котором должен будет произойти пере ход иэ О в 1, 1 в разряде большего приращения), Разряд делителя частоты 4, в котором должен будет произойти переход из нулевого состояния в единичное, определяется 10 единичными сигналами от блока управления 2 ( сигнал от блока управления 2 принимает единичное значение после обработки младшего значащего разряда делителя частоты 4, а снимается после обработки первого после значащего нулевого разряда делителя частоты 4) и от делителя частоты 4 через элемент НЕ 10, а значение соответствующего РазРяда большего приращения оп ределяется первым блоком определения нулевых разрядов координатных приращений б, на выходе которого устанавливается единичный сигнал при нулевом значении разряда большего приращения. Таким образом, если импульс интерполи-рования не может быть выдан в следУющем цикле при прибавлении 1 к младшему разряду делителя частоты 4, то на выходе первого элемента И 8 появится сигнал, который установит пер вый триггер 11 в единичное состояние. Это свидетельствует о том, что блок управления 2 должен в следующем цикле изменения состояния делителя частоты 4 прибавить не 1, а 2 к 35 младшему значащему разряду делителя частоты 4, т.е. пропустить состояние делителя частоты 4, в котором импульс интерполирования по координате с большим приращением не выдается. Логичес ки условия изменения состояния делителя 4 записываются следующим образом:если Эл Е=(,то+ц("кк.Если РЛ Е =1,то+ "1" к К;где 3 - признак старшего значащего разряда приращений (младшего значащего разряда делителя частоты 4);Г - признак единичного состояния первого триггера 11;К; - разряд делителя частоты 4, соответствующий старшему значащему разряду приращений (младший значащий разряд делителя частоты 4);К;, - сдедующий за К; разряд делителя частоты 4, 55Процесс интерполирования заканчивается после переполнения делителя 4. Выдача импульсов интерполирования по координатным осям производится первым блоком сравнения 3. 9) Если при изменении состояния делителя частоты 4 происходит увели чение его мчадшегс значащего разряда на 1 тс импульсы интерполирова-, ния пс большей координате выдаются, как обычно в интерполяторе на импульсных умножнтелях, по переходу разряда делителя частоты 4 из 0 в 1 и наличию 1 в соответствующем разряде приращения. При увеличении младшего значащего разряда делителя частоты 4 на 2 пропускается состояние делителя частоты 4, в котором этот разряд принимал нулевое значение. Поэтому, выдача импульса интерполирования по большей координате в этом случае производится по единичному значению первого триггера 11 и младшему значащему разряду делителя частоты 4.По координате с меньшим приращением, если старший значащий разряд этого приращения не совпадает со старшим значащим разрядом большего приращения, импульсы интерполирования выдаются топько по переходу разряда делителя частоты 4 иэ 0 ви наличию 1 в этом разряде меньшего приращения.Гри Равенстве старших значащих разрядов большего и меньшего приращений, по координате с меньшим приращением возможна ситуация, когда в одном цикле интерполирования требуется выпать импульсы интерполирования по единичному значению первого триггера 11, а также по переходу разряда делителя частоты 4 иэ 0 в 1 и наличию 1 в соответствующем разряде меньшего приращения.Такой случай возникает при переходе делителя частоты 4 из 0 в 1, в разряде, которому соответствует нулевой разряд большего приращения и единичный разряд меньшегс приращения, и запоминается вторым триггером 12, который устанавливается в единичное состояние по единичному сигналу на выходе второго элемента И 9, Формирующемуся по совпадению единичных сигналов от блока управления 2, элемента НЕ 10 - при нулевом разряде делителя частоты 4, второго блока сравнения 5, первоГО блока определения нулевых разрядов координатных приращений 6 и второго блока определения нулевых разрядов координатных приращений 7, на выходе которого единичный сигнал устанавливается при единичном значении разряда меньшегс приращения. Если выдать оба импульса в однои цикле интерполирования, то частота их следования будет выше тактовой, и они воспримутся приводом как один импульс. Для устранения этого явления по координате с меньшим приращением при равенстве старших значащих разрядов большего и меньшего приращений по единичному значению первого триггера 11 и младшему значащему Разряду5 Л(А,В,С,Р,Е,Г,Ь)=АВС ч СМ чАГСВ ччГСАВчГСАВЬ 30где А - признак того, что прираще. ние по данной координате больше или равно приращению по второй координате;В - признак перехода рассматриваемого разряда делителя частоты 4 35 из 0 в 1С - единичное значение выхода динамического регистра блока регистров 1, который соответствует рассматриваемой координате; 40Р - признак старшего значащего разряда приращений- признак единичного состояния первого триггера 11;Г - признак единичного состояния второго триггера 12;- единичное значение вы хода динамического регистра блока регистров 1, соответствующего второй координате. делителя частоты 4 импульс интерпо лирования выдается всегда, а по переходу разряда делителя частоты из 0 н 1 только при наличии 1 в соответствующих разрядах . большего и меньшего приращений. Импульс интерполиронания, запомненный вторым триггером 12, может быть 5 выдан по координате с меньшим прира.щением при нулевом значении разряда меньшего приращения и переходе соответствующего разряда делителя частоты 4 из 0 в 1 фф (т.е, н 10 том случае, когда другого импульса по координате с меньшим приращением не выдается).Первый и второй триггеры 11 и 12 устанавливаются в исходное (нулевое) состояние сразу же после выполнения операций, в которых они участвуют, а затем используются для последующего анализа разрядов приращений и делителя частоты 4.Таким образом, первый блок сравнения 3 реализует логические функции ,И-ИЛИ для поступающих в него сигналов от блока регистров 1, первого и втоРого тРиггеРов 11 и 12 и делителя 25 частоты 4 в соответствии с логической функцией Л для каждой из координатных осей: Импульсы интерполирования выдаются по координатам Х и У и при наличии единичного значения ФункцииЛ (А, В, С,З, Е, Г , Ь ) для соответствующей координаты.Формула изобретенияЛинейный интерполятор, содержащий последовательно соединенные блок управления, делитель частоты, первый блок сравнения и блок регистров, выходы которого подключены ко входам блока управления и первого блока сравнения, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия интерполятора, н него введены второй блок сравнения, первый и второй элементы,И, первый и второй триггеры и элемент НЕ, первый и второй блоки определения нулевых разрядов координатных приращений, входы которых и вход второго блока сравнения подключены к выходам блока регистров, выход первого блока определения нулевых разрядов координатных приращений подключен к входам первого и второго элементов И, дна других входа которых присоединены к выходу блока управления и через элемент НЕ к выходу делителя частоты, выходы второго блока сравнения и второго блока определения нулевых разрядон координатных приращений присоединены к входам второго элемента И, выходы первого и второго элементов И подключены к входам первого и нторого триггеров, выходы которого соединены с соответствуующими входами первого блока сравнения, выход первого триггера соединен со входом блока управления, другой вход которого подключен к выходу элемента НЕ.Источники информации, принятые во ннимание при экспертизе: 1. Меланченко Л. А., Немкова В. В. и др, Автоматические построители граФиков ЦВМ М Энергияф, 19 б 9. 2. Авторское свидетельство СССР М 344415, М. кл. 605 В 19/18, 1971 3. Авторское снидетельство СССР М 259492, М.кл , Ц Об б 7/30, 1968,634236Составитель В. Кошкин Редактор Р. йнтонова Текред О,йндрейко Корректор С.Гарасиняк Закаэ 6760/45 Тираж 991 Подписное 11 НИИПИ Государственного комитета Совета Министров СССРпо делам иэобретений и открытий113035, Москва, Ж, Раушская наб., д. 4/5Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

2185898, 29.10.1975

КИЕВСКИЙ ТЕХНОЛОГИЧЕСКИЙ ИНСТИТУТ ЛЕГКОЙ ПРОМЫШЛЕННОСТИ

ПАВЛЕНКО ЮРИЙ СТЕПАНОВИЧ, ПАНКОВ НИКОЛАЙ ДМИТРИЕВИЧ, КУЗЬМУК ВАЛЕРИЙ ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G05B 19/18, G05B 19/4103

Метки: интерполятор, линейный

Опубликовано: 25.11.1978

Код ссылки

<a href="https://patents.su/5-634236-linejjnyjj-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Линейный интерполятор</a>

Предыдущий патент: Самонастраивающаяся система для регулирования объектов с запаздыванием

Следующий патент: Устройство для программного управления приводом

Случайный патент: Топка для сжигания древесных отходов