Устройство для управления общими данными параллельных процессов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

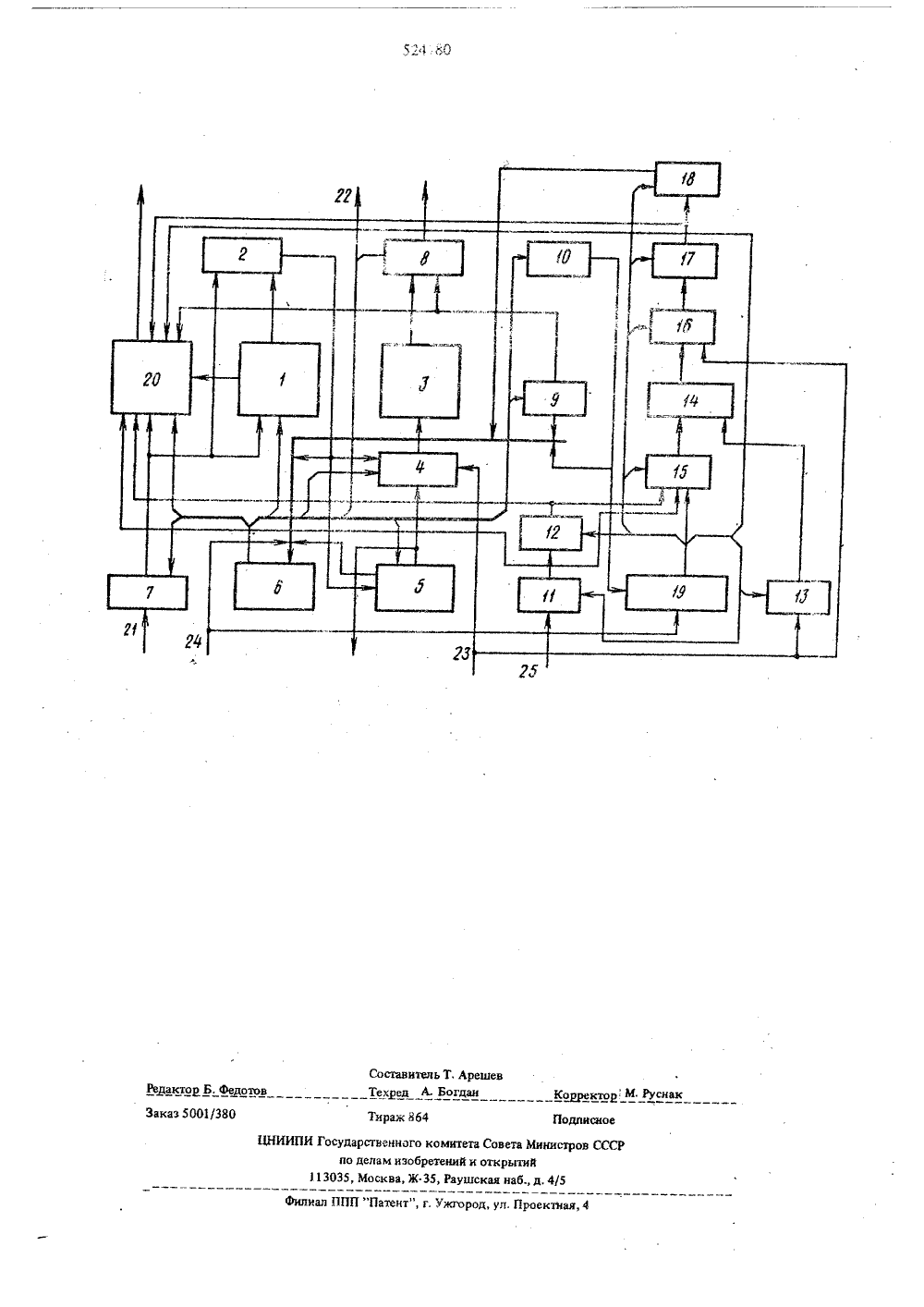

О П И С А ЧИ Е ИЗОБРЕТЕНИЯ Своз Советскии Социалистицеских Республикьиое к авт. свид-ву олии 2) Заявлено 30,12.74 (21) 2088330/24 1) М, Кл,е6 Об 7 9/19 606 У 13/06 присоединением заявки3) Приоритет Государственный коцит Совета Министров ССС по делам изобретенийи открытий) Опубликовано 0 Бюллетень 29 45) Дата опу иковаиия описания 19.01,7 2) Авторы изобретен абаян, Ю, Х. Сахин, А,(71) Заявитель(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОБЩИМИ ДАННЫМИ ПАРАЛЛЕЛЬНЫХ ПРОЦЕССОВ ни ия, выход реока адресных р ходом устройи информациИзобретение относится к вычислительной тех Известны устройства для управления общими данными параллельных процессов, содержашие ре. гистр адреса, регистр данных, блок памяти данных, коммутатор памяти, блок задания очередности использования ячеек памяти, блок индикаторов состояний ячеек памяти, блок управления, блок адресных регистров, блок сравнения адресов, входы которого соединены соответственно с выходом регистра адреса и первым выходом блока адресных регистров, выход соединен со входной шиной блока управления, со входами коммутатора памяти и блока задания очередности использования ячеек памяти, выход которого подключен к выходу устройства и через коммутатор памяти - ко входу блока памяти даннътх, выход которого соединен с первым входом регистра данных, второй вход ко. торого подключен к выходу блока индикаторов состояний ячеек памяги, управляющие вход и вы. ход которого соединены соответственно с выходнои и входнои шинами блока управл истра адреса подключен ко входу б нстров, вход соединен с адресным тва, первый информационный вх Жеренов, О, И. Невская и Н. П. Соловье онный выход устройства соединены соответственно с информационным входом коммутатора памяти и выходом регистра данных, управляющие входы регистра данных, регистра адреса, блока адресных регистров, коммутатора памяти, блока задания очередности использования ячеек памяти и управляющий выход устройства соединены с выходной шиной блока управления, входная шина которого соединена с управляющим входом устройства и выходом блока очередности использования ячеек памяти. В извест.ном устройстве содержится оборудование управ.ления быстродействующими блоками памяти (ассо.циатнвными запоминающими блоками), входящими в состав вычислительных машин системы и связанными с основной памятью, К быстродействующим блокам памяти обращаются либо в математических, либо в физических адресах; для хране.ния адресов данных, находжцихся в этих блоках памяти, применяются ассоциативные регистры. КогО да одна из машин записывает информацию в основ.ную память, устройство проверяет наличие инфор.мации с тем же адресом в ячейках блоков памяти остальных машин и исключает возможность обра.щения к этим ячейкам до тех пор, пока в них не Зб будет записана новая информация мэ основной,сед А. БогданТираж 864 по дедам113035, Моск Редактор Б, Федотовказ 5001/38 ЦНИИПИ Государстве ного комитета Советизобретений и открыа, Ж.35, Раушская н ктоо М РуснакПодписное Министров СССР тийб., д,4/5тов сравнения, но, кроме этого, он исполь;ется для дублирования регистра 13 при приеме кода времени, Содержимое регистра 17 передается в блок 20 для формирования контрольных разрядов и проверки результатов сравнений в блоке 14,Данные, записываемые в блок памяти 3 и считываемые из него, сопровождаются контрольными раз. рядами по модулю "три", а считанные данные проверяются в приемнике этих данных, например в арифметическом блоке. При выполнении записи контролируется состояние индикатора в блоке 9, соответствующего той ячейке, в которую идет запись, Если этот индикатор находится в единичном состоянии, в блоке 20 формируется сигнал ошибки. Для выполнения данного вида проверки выходы всех индикаторов блока 9 соединены со входами блока контроля 20Формула изобретенияУстройство для управления общими данными параллельных процессов; содержащее регистр адре.са, регистр данных, блок памяти данных, коммута. тор памяти, блок задания очередности использования ячеек памяти, блок индикаторов состояний ячеек памяти, блок управления, блок адресных регистров, блок сравнения адресов, входы которого соединены соответственчо с выходом регистра ад.реса и первым выходом блока адресных регистров :выход соединен со входной шиной блока управле-ния, со входами коммутатора памяти и блока задания очередности использования ячеек памяти, выход которого подключен к выходу устройства и через коммутатор памяти - ко входу блока памяти данных, выход которого соединен с первым входом регистра данных, второй вход которого подключен к выходу блока индикаторов состояний ячеек памяти, управляющие вход и выход которого соеди.иены соответственно с выходной и входной шинами блока управления, выход регистра адреса подключен ко входу блока адресных регистров. вход соединен с адресным входом устройства, первый информационный вход и информационный выход устройства соединены соответственно с информационным входом коммутатора памяти и выходом регистра данных, управляющие входы регистра данных, регистра адреса, блока адресных регистров, коммутатора памяти, блока задания очередности использования ячеек памяти и управляющий выход щ устройства соединены с выходной шиной блокауправления, входная шина которого соединена с управляющим входом устройства и выходом блока очередности использования ячеек памяти, о т л и " а:.ю щ е е с я тем, что, с целью повышения прсизвсд1 я тельности, в него введены регистры кода времен,блоки коммутаций, буферный регистр, формирова.тель, распределитель тактовых сигналов, выходы которого подключены к управляющим входам вве.денных блоков, регистров и формирователя, блок указателей обращений к ячейкам памяти и блок сравнения кодов времени, первый вход которого через первый блок. коммутации соединен с выходами первого и второго регистров кода времени, второй вход - с выходом третьего регистра кода щ времени, выход- через последовательно соединенные второй блок коммутации, буферный регистр и формирователь соединен со входной шиной блока управления, второй информационный вход устрой.ства подключен ко входу первого регистра кода З 1 времени выход которого подключен ко входувторого регистра кода времени, первый информационный вход устройства соединен со входами третьего регистра кода времени и второго блока коммутации, выход блока указателей обращений к ячейкам памяти подключен к первому управляющему входу распределителя тактовых сигналов и ко входной шине блока управления, выходная шина которого соединена со входом блока указателей обращений к ячейкам памя "и, второй управляю 4 р щий вход распределителя тактовых сигналов под.ключен к управляющему входу устройства.мирует сигналы управления для записи в выбранную ячейку блока 3 новых данных со входа 23 - ,стройства через коммутатор памяти 4. При отсут. ствии на выходе блока 2 сигнала сравнения поступившие данные и адрес этих данных записываются в ячейку блока 3 и соответствующий регистр блока 1, номер которого задается с помощью блока 5, Индикатор в блоке 9 после записи устанавливается в единичное состояние, подтверждающее, что содер. жнмое ячейки памяти блока 3 относится к адресу, записанному в регистр блока 1.При каждом обращении к паре адресный регистр блока 1 - ячейка памяти блока 3" по сигналу с блока управления 6 устанавливается в единичноессостояние соответствующий этой паре указатель в блоке 10, После перевода всех указателей в бло. ке 10 в единичное состояние формируется сигнал, фиксирующий данное состояние, Этот сигнал с блока 9 поступает в блок управления 6, который устанавливает все указатели блока 10 в исходное (нулевое) состояние (при последующих обраще. ниях к ячейкам памяти соответствующие им указа. тели снова будут переводиться в единичное состо. якие). Сформированный в блоке 10 сигнал посту. пает также на распределитель 19, который управля. ет записью текущего кода времени, поступающего со входа 25 устройства в регистр 11, и передачей содержимого регистра 11 в регистр 12, Таким образом, в регистрах 11 и 12 запоминаются моменты ,двух последних совпадений единичных значений всех указателей блока 10.В основной памяти, не показанной на чертеже, выделена ячейка, в которой при открытии "семафо. ра" одновременно с признаком открытия (установ. ка нулевого значения "семафорного" разряда) фиксируется время выполнения данного действия Когда в процессе обработки требуется обращение к общим данным, сначала содержимое указанной ячейки основной памяти считывается в регистр 13 и через блок коммутации 16 - в регистр 17 с последующим анализом значения "семафорного" раз. ряда. Если обращение к общим данным разрешается ("семафорный" разряд находится в нулевом состоянии), в блоке 14 по сигналам распределите. ля 19 содержимое регистра 13 последовательно сравнивается сначала с содержимым регистра 11, затем - с содержимым регистра 12, Если код времени последнего открытия "семафора, считыный в регистр 13, больше кода времени, записан. ного в регистр 11, данные, хранящиеся в блоке памяти 3, объявляются недействительными, так как в ячейках этого блока могут находиться устаревшие общие данные, которые невозможно распо. знать и выделить.Процесс объявления недействительности дан. ных включает этапы анализа результата сравнения, записанного в отведенные для этой цели разряды буферного регистра 17, и выработку сигнала, соответствующего полученному результату, в формн. рователе 18, Этот сигнал поступает в блок управ. ления 6, который устанавливает в нуль все нндика. торы блока 9, При указанном выше исходе щдер, жимое регистра 13 не сравнивается с содержимым регистра 12. В противном случае это сравнение происходит и, если оказывается, что код регист. ра 13 меньше кода, хранящегося в регистре 12, все данные в блоке памяти 3 сохраняются, так как они не менее двух раз полностью сменились после открытия "семафора".,При получении третьего результата сравнения сохраняются только те данные блока 3, которым соответствуют единичные значения указателей в блоке 10, так как среди данных с нулевым значе. нием указателей в блоке 10 могутбыть устаревшие после открытия "семафора" общие данные, В этом случае в формирователе 18 вырабатывается сигнал, соответствующий третьему результату сравнения, который поступает в блок управления 6, и послед. ний устанавливает в нуль те индикаторы блока 9, которые соответствуют ячейкам с нулевым значе. нием указателей в блоке 10. Если обращение к общим данным запрещено ("семафорный" разряд находится в единичном состоянии), в вичислительной машине организуется ре.жим периодического обращения к семафорной ячейке до момента получения нулевого значения семафорного разряда либо переход к решению другой задачи. Сигналы на выходе формировате.ля 18 не вырабатываются. Лостоверность выполнен.ных устройством операций подтверждается с помощью блока контроля 20. Для этого принимаемые в регистр 7 и записываемые в регистры блока 1 адреса, а в регистры 11,12 - коды времени сопровождаются контрольными разрядами (сверткой по модулю три) . Для адреса принятого в регистр 7, в блоке 20 формируются контрольные разряды (свертка по модулю "три"), которые затем сравниваются с контрольными разрядами, поступившими вместе с адресом в регистр 7. Когда в блоке 2 формируется сигнал сравнения,контрольные разряды адреса, с которым произошло сравнение содержиьюго регистра 7, считываются в блок 20, где проверяется соответствие их контрольным разрядам, хранящимся в регистре 7, т.е. подтверждается результат обращения к заданной ячейке памяти.В целях экономии оборудования при требуемом быстродействии, операции сравнения в блоке 14, как уже отмечалось, выполняются последовательно, т.е. сначала содержимое регистра 13 сравнивается с содержимым регистра 11, затем содер. жимое регистра 13 - с содержимым регистра 12.Отмеченные этапы сравнения сопровождаются проверкой функционирования блока сравнения ко. дов времени 14, который реализуется, например, в виде сумматора. Код времещ, записываемый в регистр 13 из ячейки основной памяти, передается также через блок коммутации 16 для записи в буферный регистр 17. Основное назначение буферного регистра - хранение промежуточных реэульта.

СмотретьЗаявка

2088330, 30.12.1974

ПРЕДПРИЯТИЕ ПЯ А-3162

БАБАЯН БОРИС АРТАШЕСОВИЧ, САХИН ЮЛИЙ ХАНАНОВИЧ, ЖЕРЕНОВ АНАТОЛИЙ ИВАНОВИЧ, НЕВСКАЯ ОЛЬГА ИВАНОВНА, СОЛОВЬЕВА НАТАЛЬЯ ПЕТРОВНА

МПК / Метки

МПК: G06F 9/19

Метки: данными, общими, параллельных, процессов

Опубликовано: 05.08.1976

Код ссылки

<a href="https://patents.su/5-524180-ustrojjstvo-dlya-upravleniya-obshhimi-dannymi-parallelnykh-processov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для управления общими данными параллельных процессов</a>

Предыдущий патент: Оптико-электронное устройство для суммирования одноразрядных чисел

Следующий патент: Система для синтеза тестовых сигналов

Случайный патент: Устройство для прямого массажа сердца