Устройство для формирования адресов табличных функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

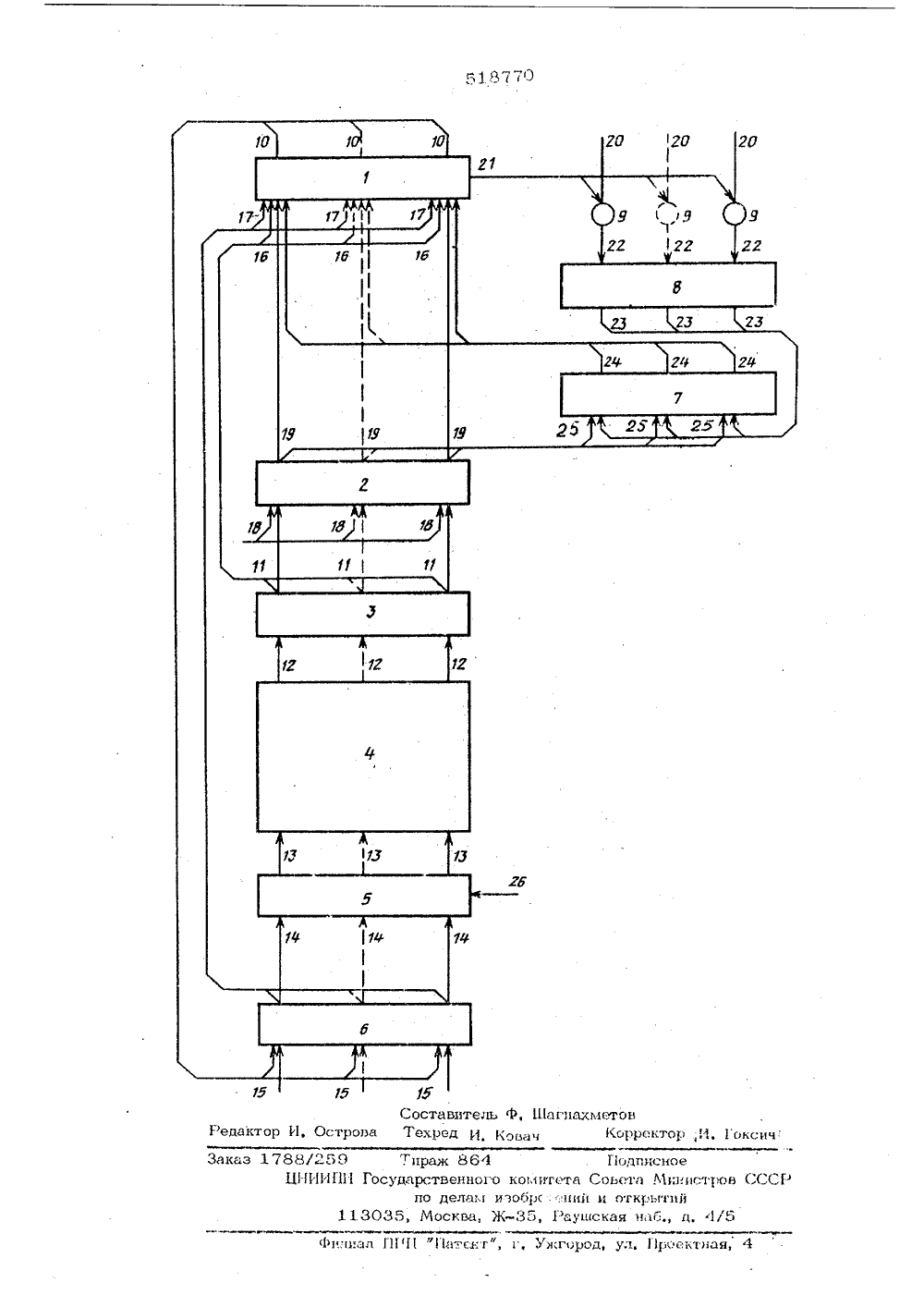

О П И С А Н И Е 11) бт.8770ИЗОБРЕТЕНИЯ Союз СоветскихСоциалистицескихРеспублик УОРСКОМУ СВИДЕПЛЬСТВУприсоединением заев и Яо Гааударатееннын комнтет Совета Инннотроа СССР ка делам нэаоретеннк н открытей(72) Авторы изобретения Палагин А ургаев и(71) Заявител Украинской Ордена Ленина институт кибернетики(54) УСТРОЙСТ Я ФОРМИРОВАНИЯ АДРЕСОЧНЫХ ФУНКЦИЙ ельамфункИзобретение относится ной технике, в частности для формирования адресов дий и может быть яспольз троевии цифровых вычисл ного устройсттратами на обоо создание извесо с большими вычи за связан рудование.Цель изобрет устройабличных ение обдрупри п к маш ок 0 Извес."но устройство для формированияадресов табличных функций, содержащеерегистр адреса команд, выходы которогосоединены с первой группой входов сум-матора и через регистр - счетчик адресасо входамй блока памяти, выходы которого через выходной регистр соединены совторой группой входов сумматора и с первой группой входов индексного регистра,выходы которого соединены с третьейгруппой входов сумматора, выходы которого соединены с первой группой входоврегистра адреса команд, вторая группавходов которого соединена с первой группой входов устройства, управляюший входкрторого со .динен со счетным входом регистра-счетчика адг са, а вторая группавходов индексного регистра соединена совторой группс.а входов устройства,дования.Для этого устройство содержит регистблокировки, первую и вторую группы элементов И, причем выходы индексного регистра и регистра блокировки соединены1 О со входемн элементов И первой группы,выходы которых соединены с четвертой1,группой входов сумматора, выход знакового разряда которого соединен с,однимивходами элементов И второй группы, дру 15 1 ие входы которых соединены с третьейгруппой входов устройства, а выходы -со входами регистра блокировки.Блок-схема устройства приведена начертеже,2Устройство для формирования адресовтабличных функций содержит сумматор 1, индексный регистр 2, вы.ходной регистр 3, блок. памяти 4, регистрсчетчик адреса 5, регистр адреса команд25,6, элементы И 7 первой группы, регистрб 110 к 11)овин 8, э 1 ОлВ 11 ты И 9 Второй Групы, Выходов с 5"мат Ора, ВьеходцОГО регистщра, бло 1 са памяти, ре 1 ч стра-счетчика адреса и ре 1 пстра адрес,". команд соответстВенно 10-14, Входи регистра адреса команд 15, входы сумматора 16, 17, вхо-.ды и Выходы ендексного регистра 18, 19,информационные входы элементов И второй группы 20, выход знакового разряда сул 1-матора 21, входы и Выходы регистра бло-,кировки 22, 23, выходы и входы элеелентов И первой группы 24, 25 счетныйвход регистра-счетчика адреса 26,Регистр"адреса команд 6, блок памяти 4 с регистром - счетчиком адреса 5,подключенныл ко входам 13 и выходньЕЛрегистром 3, гОдк поченным к выходал 12,иедексный регистр 2 и сумматор 1 соединены последовате Еьно, Кроме того, сумлвтор 1 Выходамп 10 подыцочен ко входам регистра адреса команд 6, а входами 17 к Вьходам регисчра адреса коляиц6, Входами 16 к вь 1 ходам 11 выходногорегистра 3, Входами 24 к выходам элелентов И 7 первой группы, информационные входы 25 которой соединены с вь 1 ходами индексного регистра 2, а управляюцие - с Выходами 23 регистра блокировки 8, Выход 21 знакового разрядасумматора 1 через элементы И 9 втоой группы подкл 1 ОЕец ко входам 22 реГистра блокировки 8, Входы 18 шдексИОГО реГистра 2 по;КлОчецы к итоговому регистру арифметического устройстване чертеже не показан), а Выходь 19 ко входам сумлатора 1, Входы 15 регистра аг 1 реса команды 6 подключены к выхо 1дам ЕцЗОГ 1 алл 1 ВОГО зяиомицаОшего устро ъства ,Иа чертеже пе показано),На Входы 20 последовательо во Времени няч 11 яя с л 11 адпего разряда поступают "ед 11 пп 111:е" сигналы 11 я Вход 26ре 1.истра- с 11 етч 1 ка 5 Оступаут сиГналь 1Ф 1/IБ блоке памяти 4 хранятся табли иыезначения Функций, расположенные в ячейках имяти В виде тябл 1 ц (массивами) спосто нно-переменным шагом но адресам,и зцачени ЯРгУмецта Хг, Г = 1,Р,соотвегствуесшие смене шага расположения табличных значений функций. Прпэтом для каждой из функцнй диапазон измепения аргумента, например 0,Ц, узловыми; цячениял;1 Х1,разщбнвается на поддияцазоныОХ ) Г Х Хс) Х Х ) Х 1)вцутри которых ц 1 аг расположения по адресу и яр ументу табличных значенийфу 1 КЕии посто- цый и равен соответстВсчпО 1;11, 11 ц 1, а при пе 1 сегходе из одного поддияпазоця в другойуцваивается, т,е. Н+,1 =- 2 1 г е 1,Рр %где Е, - минимальный шаг, равный целой степени Р основания системы счисления (.в данном случае целой степени2), т.е, 1=2 й И, . Вели цена 1.еи значения аргумента х, г:1, 1 храссчитываются исходя из заданной погрец-"ности Я приближения функции 1 х), на: .16пример по следуюшей методике,Из равенства ос.аточпого члена интерполяционного полинома Ньютона нулевогопорядка заданной погрешности ползучим 4определяется зна111где, 10 - целое, не меньшее ау альный 1 цаг 111 -"- ЕЕ,1, чных значений фуцкш 1 и онаи, х, 3 . Зцачезцачеция ХР = 1, М у,п,тате рец 1 еипя уравЗатем по значению чение Р = 1(Оц Означает ближайшее и тем самым миил по аргументу табли 1 (х) для поддияпаз цие А и пруИе определяются в рез цецийСМ Получеш 1 ые таким обр,"зом значенияХГ, Г= 1, к представляют собой и обшемслучае полцоразрядные значения аргумента Х Количество узловапазона определяетс, ДХ,=Х - ХПри этом объем в Ва) значений каждя1 =Г Хегде с ", - количествозначений одной из функций при постоянно,переле 1 еном ц 1 аге, равнее количеству ячеек памяти, занятых табличными значениями этой функции;1= З 1 10 1 С - разрядность ячеек паЬ 2мяти. Для реализации постоянно-переменного шага необходимо хранить для каждой из вычисляемых функций, кроме того, значения аргумента Х 1 = 1 Й содт- ветствуюшце смене шага расположения табличных значений функции для чего требустся Объем памяти в битах, равный д. =-В игрыш В объеме памяти при постоянно-п, ременном 1 паге расположения табличнь 1 х значений функций по ср" в 11 ен 1 цо спостоянпыи 1 цагом оценивается для каж- ностью не более 6 = 2-с 1. (3 соотвотдой из функций отношением ствии с изложенной вьпие методикой дляд2 заданных исходцьгх данных рассчитацы, " дХ , дхг+1,+.Рги.д 2-Р Рзначения2 "р,д 2ц 2б11 усть, напримео, необходимо вычис лять функцию бЮ ф Х, К (-0,1) с погреш- М, Р=, Ц=Ь, =2, =-и, =-, , =-0,00000110100; дХ,=-0,000001100111 =100011111002, 1=111011111 =1101012, 1 =.1 1012,О +1 г+ф101101100012 1451=1 1,у=14570 бит; д = Н =50 бит1 с = 2 =2048 Чс=1 с=20480 бит.Выигрыш в объеме памяти при посто- др по шилам 12 выбирается значение аргуяцно-переменном ииге расположения таб мента Й, Затем на сумматоре 1 опре-личных значений функции ВЖ - 1 по;62деляется разность х -х 1 между содерсравнению с постоя 1 п 1 ым шагом равен жимыми регистров 2 и 3, На ппце 20,2 одво соответствующей младшему разряду регистЧ дЛ 626 ра блокировки 8, генерируется "единицыЫ",Устройство работает следующим обра- сигнал, который проходит через соответзом, Аргумент Х из итогового регистра ствующий элемент И 7 и записывается варифметического устройства (на чертеже младший разряд регистра 8, если знакце показан) цо шинам 18 пересылается разности х - х, положительный в случаена регистр 2 и располагается в его млад- ЭО вычисления функции с монотонно-убываюиих разрядах, оставляя, в простейшем щей производной 1 (х), Затем к сослучае, нулевыми старшие разряды, коли- держимому регистра-счетчика 5 прибавлячество которых не менее орк , ется единица" его младшдго разряда, игде К -множество вычисляемых функций, соответственно полученому результатуНа регистр адреса колсанд 6 по шинам 15(адресу) из блока памяти 4 выбираетсяпересылается адресная часть команды на регистр 3 значение Х, На сумматофункция", означающей вычисление функ- ре 1 определяется разность, х - хг, НаЪции (элементарной или сложной) от аргу- шине 20, соответствующей разряду регистмента Х ра 8, следующему за младшим, генерируСодержимое регистра 6 является ис- р ется единичный" сигнал, который прохополнительным адресом, по которому рас- дит через соответствующий элемент И 7положено в памяти значение аргумента и записывается в соответствуюп 1 ий разХ д, соответствующее началу поддиапа- ряд регистра блокировки 8, если знакзона (.х 1, х) , в котором выпол- . разности х - х 2 положителен и т,л, до,1 яется перв.1 е удвоение шага табличных ,д первого результата сравнения Х -ХГ ( Означений функции. Остальные значения ,или до перебора всех значений ХГ, Г =Я.аргумента Х Г = 1,1 распОложены в Для функций с мо 1 отоцно-возрастаювсейпорядке возрастания нолера г по адре- ,производной( Х,) процесс форлсировасам, следующим за адресом значения ар ,ния содержимого регистра 8 сводится кгумента Хд, Расположение Х Г = 1,К щ описанному при определении ЯЯП (Хг в Х ),по разрядам ячейки блока памяти 4 ана Затем из регистра 2 цо шинам 25 аргулогично расположен 1 по аргуменга Х в ре- мент Х, а по шинам 23 пз регистр 8гистре 2, Старшая часть разрядов регист- сформированная величина поступает нора 6, разл 1 ер 1 ость которой рава ЯГсц; К(., входы группь 1 элеиецтов И Э, где опрепс;где К - множество аычислчемых функ- д ляется резуцьтси логическса о умноженияций, содержит адрес таблицы значений аргуме; а Х и инверсии содержимого ревычисляемой функш 1 и, Гистра 8, 1-дезусьтат по 1 ип 1 ам 24 сФСодержимое регистра 6 по шинам 14 сылвется в сумлдатор 1, 11 осле этого .иапересы;1 ается в регистр-счетчик 5 и из сумл 1 аторе 1 вь 11 01 нгется с ум миро ес 1 1:,блока памяти 4 - на выходной регис 16 3 ФО результатом котор;,го 6 пляс.тся сои.61тельный адрес таблн шого значения фунз- пии, его содержимого с содержимым старших разрядов регистра б, определяющих вид вычисляемой функции, т,е, ЯП Х,сдьХ или оХ и т,д. Из су 1;:ьа.ора 1 по шинам 10 результат операции пересылается в регистр 6 и затем из него по шинам 14 - в регистрлсчетчик адреса 5, Окон чательным результатом выполнения коман ды функция будет число (табличное зна- чение вычисляемой функции), выбранное иэ блока памяти 4 на регистр 3 по исполнительному адресу регистра 5,Ф Формула изобретенияУстройство для формирования адресовтаблипплх функций, содержащее регистрадреса команд, выходы которого соединены с первой группой входов сумматора ичерез регистр-счетчик адреса - со входами блока памыги, выходы которого черезвыходной регистр соединены со второйгрупгой входов сумматора и с первой группой Входов индексного регистра, Выфходы которого соединены с третьей группой входов сумматора, выходы которогосоединены с первой группой входов регистра ацреса команд, вторая; группа входов которого соединена с первой группойвходов устройства, управляющий вход которого соединен со счетным входом регистра-счетчика адреса, а вторая группавходов индексного регистра; соединена совторой группой входов устройства, о тл и ч а ю щ е е с я тем,. что, с цельюсокращения оборудования, оно содержитрегистр блокировки, первую и вторую груп )Ьпы элементов И, причем выходы индексного регистра и регистра блокировки соединены со входами элементов Й первойгруппы, выходы которых соединены с чеъвертой группой входов сумматора, выходзнакового разряда которого соединен с ф одними входами элементов И второй грунь .пы, другие входы которых соединены стретьей группой входов устройства, а вЦэходы - со входами регистра блокировки,г87,0 Составите,пь Ф, Шагиахметов акт ор И, Острова Техред И 1;о ва Корректор; И, 1 окс и ч;ССР 1 Ч 1 ф 11 атсят"и, Ултород, ул, 111:оектаи, 4 лига 88/259 Тираж 864 ЦНИИ ПИ Государственнопо делам11.3035, Москва,о комитета изо 61 к:. иЖ 3,э Пидпнсное Совета Мииистроии открьгеий нская наГ, д, 1/Г

СмотретьЗаявка

2031528, 10.06.1974

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УКРАИНСКОЙ ССР

КУРГАЕВ АЛЕКСАНДР ФИЛИППОВИЧ, ПАЛАГИН АЛЕКСАНДР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 9/00

Метки: адресов, табличных, формирования, функций

Опубликовано: 25.06.1976

Код ссылки

<a href="https://patents.su/5-518770-ustrojjstvo-dlya-formirovaniya-adresov-tablichnykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования адресов табличных функций</a>

Предыдущий патент: Устройство управления каналами

Следующий патент: Блок приоритета

Случайный патент: Устройство для цикловой синхронизации