Кодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

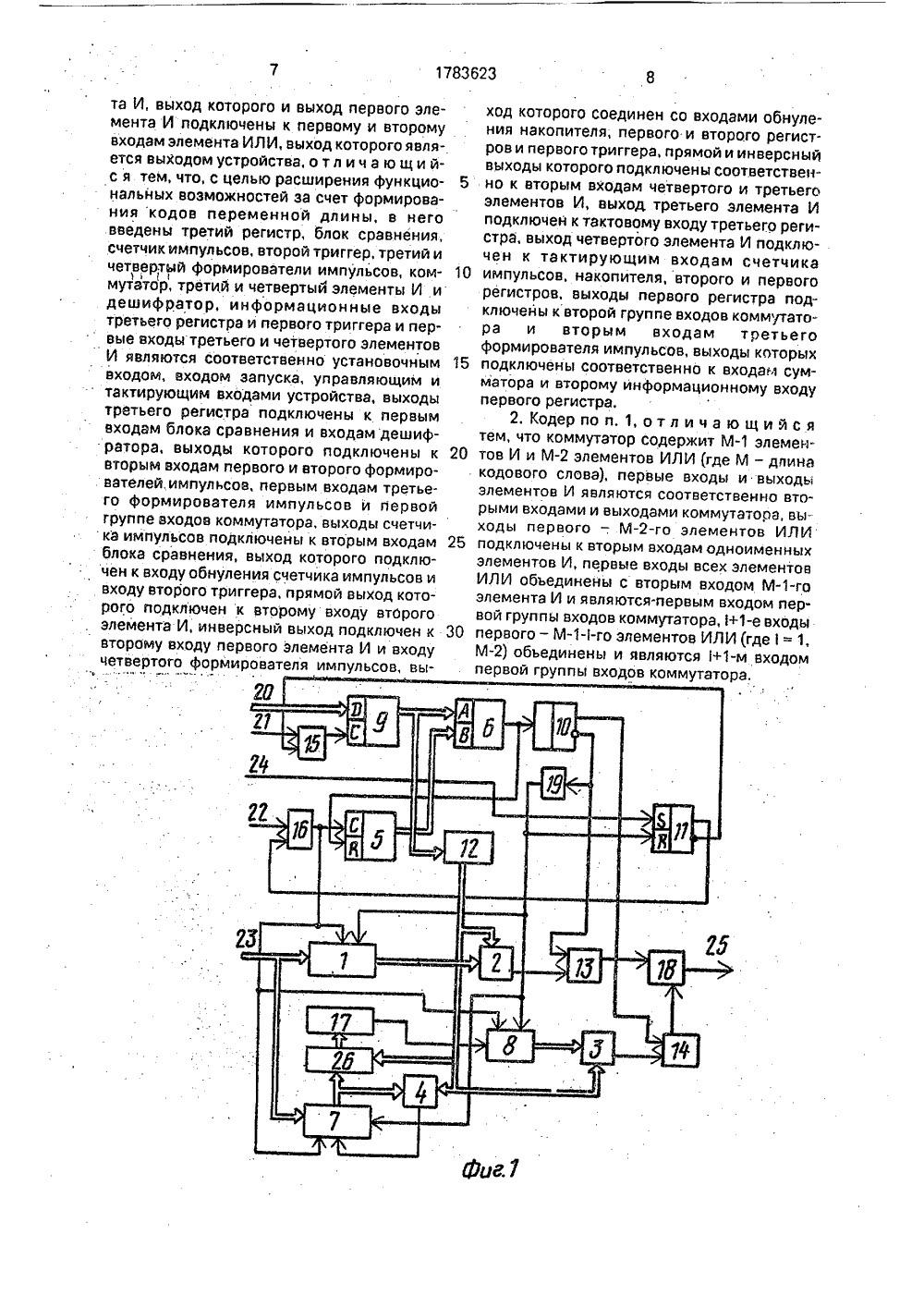

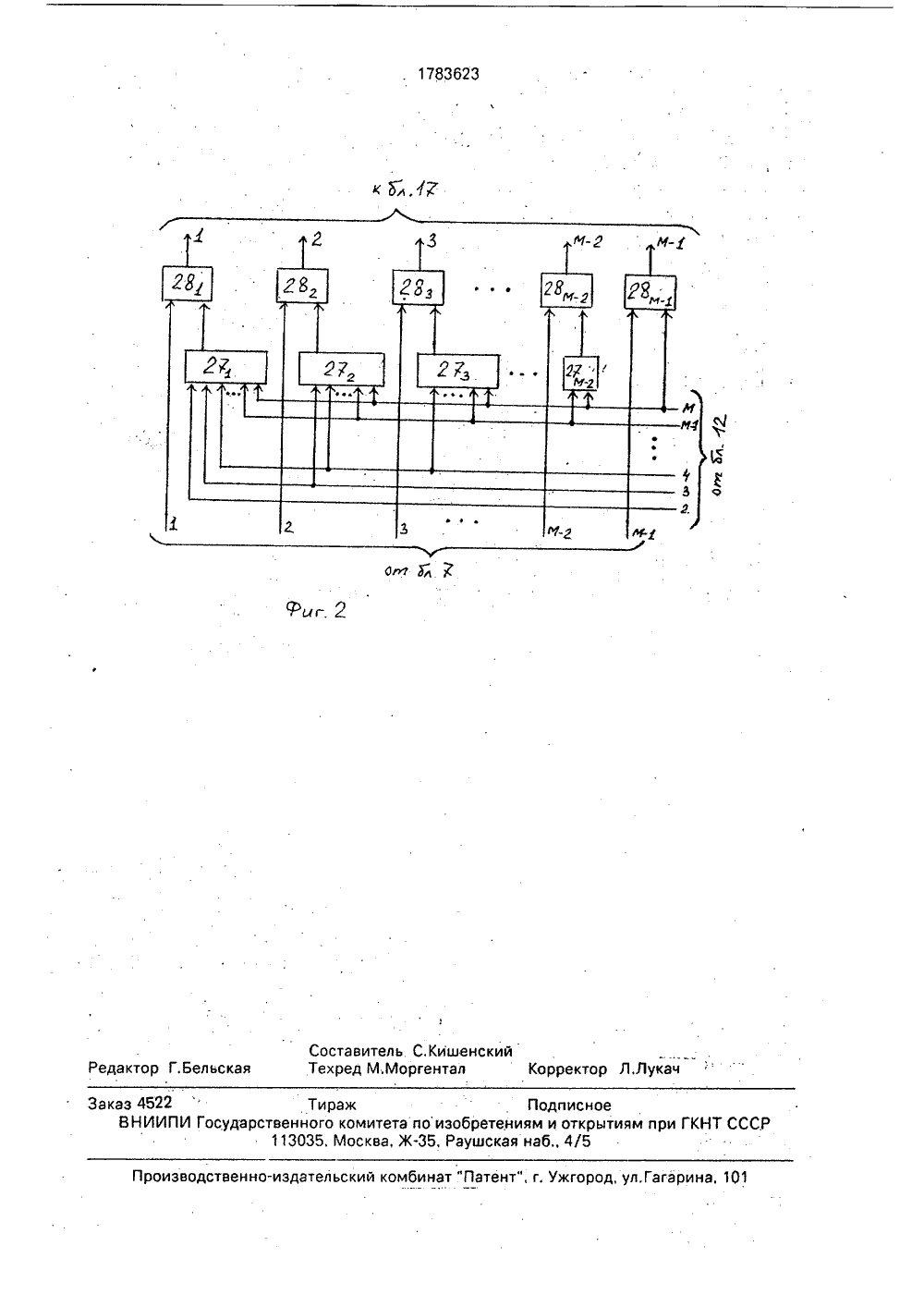

)5 Н 03 3/ Т имо чиин кодо й накопи- , триггер и ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(71) Московский институт инженеров гражданской авиации(56) Блейхут Р. Теория и практика кодов, контролирующих ошибки. М.: Мир, 1986, с.24, рис. 1.4.Авторское свидетельство СССРЬ 1399894, кл. Н 03 М 13/00, 04.01,87. (54) КОДЕР(57) Изобретение относится к электросвязии может быть использовано в системах передачи информации. кодированной инверсными кодами, Целью изобретения является зобретение относится к электросвязи ет использоваться в системах переда- формации для кодирования инверсных Известен кодер, содержащитель, распределитель импульсовэлемент ИЛИ.Недостатками известного кодера являются низкое быстродействие и узкая область применения.Наиболее близким по технической сущности к изобретению является кодер, содержащий накопитель, первый и второй распредели импульсов, первый формирователь импульсов, триггер и элемент ИЛИ, сумматор, два регистра, второй формирователь импульсов и два элемента И.Недостатками прототипа являются узкие функциональные возможности. расширение функциональных возможностей устройства за счет формирования кодов переменной длины. Кодер содержит первый триггер, накопитель, информационные входы которого объединены с информационными входами первого регистра и являются информационными входами устройства, сумматор, второй регистр, два формирователя импульсов, два элемента И, выходами подключенных к входам элемента ИЛИ, выход которого является выходом устройства. Для достижения цели в кодер введены третий регистр, блока сравнения, счетчик импульсов. второй триггер, третий и четвертый формирователи импульсов, коммутатор, третий и четвертый элементы И и дешифратор. 1 з,п. ф-лы, 2 ил,Цель изобретения - расширение функциональных возможностей кодера за счет формирования кодов переменной длины.Поставленная цель достигается тем, что в кодер, содержащий первый триггер, накопитель, информационные входы которого объединены с первичными информационными входами первого регистра и являются информационными входами устройства, выходы накопителя подключены к первым входам первого формирователя импульсов, выход которого подключен к первому входу первого элемента И, сумматор, выход которого подключен к первому входу второго регистра, выходы которого соединен с первыми входами второго формирователя им-пульсов, выход которого подключен к первому входу второго элемента И, выход которого и выход первого элемента И под-. ключены к пеовомч и втооомч входам эле5 10 5055 мента ИЛИ, выход которого является выходом устройства, введены третий регистр, блок сравнения, счетчик импульсов, второй триггер. третий и четвертый формирователи импульсов, коммутатор, третий и четвертый элементы И и дешифратор, информационные входытретьего регистра и первого триггера и первые входы третьего и четвертого элементов И являются соответственно установочным входом, входом запуска, управляющим и тактирующим входами устройства, выходы третьего регистра подключены к первым входам блока сравнения и входам дешифратора, выходы которого подключены к первым входам первого и второго формирователей импульсов, первым входам третьего формирователя импульсов и первой группе входов коммутатора, выходы счетчика импульсов подключены к вторым входам блока сравнения, выход которого подключен к входу обнуления счетчика импульсов и входу второго триггера, прямой выход которого подключен к второму входу второго элемента И, инверсный выход подключен к второму входу первого элемента, И и входу четвертого формирователя импульсов, выход которого соединен с входами обнуления накопителя, первого и второго регистров и первого триггера, прямой и инверсный выходы которого подключены соответственно к вторым входам третьего и четвертого элементов И, выход третьего элемента И подключен к тактирующим входам счетчика импульсов, накопителя, второго и первого регистров, выходы первого регистра подключены к второй группе входов коммутатора и вторым входам третьего формирователя импульсов, выходы которых подключены соответственно к входам сумматора и второму информационному входу первого регистра,Кроме того, коммутатор содержит Мэлементов И и Мэлементов ИЛИ, где М - длина кодового слова, первые входы и выходы элементов И являются соответственно вторыми входами и выходами коммутатора, выходы с первого.по (М)-й элементов ИЛИ подключены к вторым входам одноименных элементов И, первые входы всех элементов ИЛИ обьединены с вторым входом (М)-го элемента И и являются первым входом первой группы входов коммутатора, + 1)-е входы с первого по(М-)-й элементов ИЛИ, где 1= 1,М, объединены и являются +1)-м входом первой группы входов коммутатора,На фиг. 1 представлена структурная . схема кодера; на фиг, 2 - структурная схема коммутатора,Кодер содержит накопитель 1, первый формирователь 2 импульсов, второй и третий формировали 3 и 4 импульсов, счетчик 5, блок 6 сравнения, с первого по третий регистры 7-9, второй триггер 10, первый триггер 11, дешифратор 12, элементы 13-16 И с первого по четвертый, сумматор 17, элемент 18 ИЛИ, четвертый формирователь 19 импульсов, установочный вход 20, управляющий вход 21, тактирующий вход 22, информационный вход 23, вход 24 записи, выход 25, коммутатор 26,Коммутатор 26 (фиг. 2) содержит элементы ИЛИ 271-27 ыи элементы И 281-28 м,Изобретение обеспечивает кодирование информации инверсными кодами при15 длинах информационных слов до некоторого числа М включительно; максимальнаядлина выходного кодового слова - 2 х М.Допустимы любые длины информационныхслов от 1 до М, Разрядность накопителя,20 первого и второго регистров - блоков 1, 7 и8 - равна М. Формирователи 2-4 импульсовпредставляют собой совокупности двухвходовых элементов И, первые входы которыхсоединены соответственно с выходами бло 25 ков 1,8 и 7, а вторые одноименные входы,всех формирователей обьединены и соединены с выходами дешифратора 12. В каждом формирователе импульсов выходы всехэлементов И объединены на входах М-вхо 30 довогоэлемента ИЛИ, выход которого является выходом соответствующегоформирователя импульсов.Регистр 9 предназначен для.хранениядвоичного числа, представляющего длину35 кодового слова от 1 до М соответственно).В накопителе 1 записывается и выдвигаетсяв канал связи информационное кодовое слово. В регистре 7 информационное кодовоеслово циклически сдвигается для формиро 40 вания проверочных символов, которые записываются в регистре 8 и из негопоступают в канал связи,Пусть необходимо передавать информацию в виде слов, закодированных(2 х К,45 К) - инверсным кодом, где К - число информационных символов, КМ,Перед началом работы кодера в регистре 9 устанавливается текущая разрядностьинформационного кодового слова "К": ее двоичный код устанавливается на входе 20, управляющим сигналом на входе 21 через открытый сигналом с триггера 11 элемент И 15 данный код записывается в регистр, Исходное состояние триггера 11 - нулевое. В исходном состоянии все регистры также обнулены, как и триггеры; содержимое счетчика - нулевое. Тактовые импульсы на устройство не поступают, так как элемент И 16 закрыт нулевым сигналом с прямого выхода триггера 11,Информационное слово параллельным кодом заносится в накопитель, представляющий собой регистр памяти, а также в регистр 7. Процесс кодирования начинается подачей импульса запуска на вход 24. Триггер 11 устанавливается в единичное состояние и разрешает поступленйе на входе кодера тактовых импульсов. Модуль счета счетчика 5 равен "М",В нулевом такте работы разрешающий потенциал формируется на первом выходе дешифратора 12, При этом первый информационный символ информационного кодо вого слова с первого выхода накопителя 1 через блок 2 поступает на вход элемента 13, открытого сигналом с инверсного выхода триггера 10, и через элемент 18 поступает в канал связи. На нулевом такте на сумматоре (многовходовом сумматоре по модулю два) 17 формируется первый проверочный сим. вол в соответствии с проверочной матрицей инверсного кода, имеющей видО 1111 1 О О,О г о 1,11 о г о .о1 1 1 1 .0 О О 0из которой следует, что 1-й проверочный символ кода равен сумме по модулю два всех информационных символов, за исключением одноименного 1-го,Таким образом, с входами сумматора 17 соединяются все разряды регистра 7 через коммутатор 26, который работает следующим образом(фиг. 2): если информационное слово имеет К разрядов. с К-го выхода дешифратора 12 получают положительный потенциал, через элементы ИЛИ 271-27 коткрывающий соответствующие элементы И 281-28 к-г, которые коммути руют значения соответствующих информационных символов, кроме старшего символа, для формирования текущего проверочного символа.Формирователи импульсов 2 и 3 коммутируют соответственно. старшие символы кодовых слов в элементы И 13 и 14. Формирователь 4 коммутирует К-й (старший) символ на последовательный информационный вход (младшего разряда) регистра 7,В момент поступления первого тактового импульса значение первого проверочного символа записывается в первый разряд регистра 8, далее осуществляетСя сдвиг информационного слова в накопителе 1; в течение следующего такта работы кодера в канал связи поступает вторбй информационный символ. Производится так-же циклический сдвиг информационного слова в регистре 7, а счетчик 5 инкрементируется. Так продолжается до тех пор, пока сидержимое счетчика (после Ктактов с приходом К-го тактового импульса) не станетравным содержимомурегистра 9. При этоц 5 срабатывает блок сравйения и сбрасывает.счетчик, а также-устайавлйвает триггер 10 ц единичное состояние; закрывая" элемент И 13 и открывая элемент И 14. В течение следующих К тактовыхинтерваловпроисходит 10 вывод в канал связи проверочных символов.Вторичное достижение содержимымсчетчика 5 равенства с содержимым регист- ра 9 вызывает повторное срабатывание блока сравнения, триггер 10 устанавливается в 15 нулевое состояние, и сбрасывается счетчик5, По фронту сигнала с триггера 10 срабатывает формирователь 19, который выходным импульсом сбрасывает в исходное состояние триггер 11, регистры 7 и 8, устанавливая 20 кодер в исходное состояние,В процессе кодирования триггер 11 запрещает запись нового кодового слова в регистр 9.Информационное слово записывается в25 младшие разряды блоков 1 и 7, при этом содержимое из старших разрядов (например, при переходе к кодированию кодовыхслов с меньшей разрядностью) не имеетзначения, что обеспечивается формировате 30 лями импульсов.Регистры и накопитель могут быть вы полнены на основе, например, микросхемтипа К 155 ИР 1, блок сравнения - на основемикросхемы К 555 СП 1,35 Таким образом, изобретение позволяетлегко модифицировать разрядность кода впроизвольных пределах с сохранением корректирующих свойств кода. Наличие регистра, содержащего длину кодового слова,40 позволяет реализовать управление ксдеромот ЭВМ, Это дает возможность использовать кодер в адаптивных системах передачиданных, т.е, расширить его функциональныеВозможности,45Формула изобретения 1, Кодер, содержащий первый триггер,накопитель, информационные входы которого обьединены с первыми информацион ными входами первого регистра и являютсяинформационными входами устройства, выходы накопителя подключены к первым вхо-.дам первого формирователя импульсов, выход которого подключен к первому входу 55 первого элемента И, сумматор, выход которого соединен с информационным входом второго регистра, выходы которого соединены с первыми входами второго формирователя импульсов, выход которого подключен к первому входу второго элемента И, выход которого и выход первого элемента И подключены к первому и второму входам элемента ИЛИ, выход которого является выходом устройства, о т л и ч а ю щ и йс я тем, что, с целью расширения функциональных возможностей за счет формирования кодов переменной длины, в него введены третий регистр, блок сравнения, счетчик импульсов, второй триггер, третий и четвертый формирователи импульсов, коммутатор, третий и четвертый элементы И и дешифратор, информационные входы третьего регистра и первого триггера и первые входы третьего и четвертого элементов И являются соответственно установочным входом, входом запуска, управляющим и тактирующим входами устройства, выходы третьего регистра подключены к первым входам блока сравнения и входам дешифратора, выходы которого подключены к вторым входам первого и второго формирователей.импульсов, первым входам третьего формирователя импульсов и первой группе входов коммутатора, выходы счетчика импульсов подключены к вторым входам блока сравнения, выход которого подключен к входу обнуления счетчика импульсов и входу второго триггера, прямой выход которого подключен к второму входу второго элемента И, инверсный выход подключен к второму входу первого элемента И и входу четвертого формирователя импульсов, выход которого соединен со входами обнуления накопителя, первого и второго регистров и первого триггера, прямой и инверсный выходы которого подключены соответствен но к вторым входам четвертого и третьегоэлементов И, выход третьего элемента И подключен к тактовому входу третьего регистра, выход четвертого элемента И подключен к тактирующим входам счетчика 10 импульсов, накопителя, второго и первогорегистров, выходы первого регистра подключены к второй группе входов коммутатора и вторым входам третьего формирователя импульсов, выходы которых 15 подключены соответственно к входам сумматора и второму информационному входу первого регистра.2. Кодер по и, 1, о т л и ч а ю щ и й с ятем, что коммутатор содержит Мэлемен тов И и Мэлементов ИЛИ (где М - длинакодового слова), первые входы и выходы элементов И являются соответственно вторыми входами и выходами коммутатооа, выходы первого - , М-го элементов ИЛИ 25 подключены к вторым входам одноименныхэлементов И, первые входы всех элементов ИЛИ объединены с вторым входом М-го элемента И и являютсяпервым входом первой группы входов коммутатора, 1+1-е входы 30 первого - М-1-го элементов ИЛИ(где 1=1,М) объединены и являются 1+1-м входом первой группы входов коммутатора,1783623 О л 7 Й Составитель С,КишенскТех ед М.Моргентал аказ 4522 Тираж ПодписноеВНИИПИ Государственного комитета поизобретениям и открытиям и113035, Москва, Ж, Раушская наб., 4/5 Т СССР Гагарина. 1 О Производственно-издательский комбинат "Патент", г. Ужгор ииедактор Г.Бельская Р Корректор Л.Лукач

СмотретьЗаявка

4798972, 05.03.1990

МОСКОВСКИЙ ИНСТИТУТ ИНЖЕНЕРОВ ГРАЖДАНСКОЙ АВИАЦИИ

КИШЕНСКИЙ СЕРГЕЙ ЖАНОВИЧ, ИГНАТЬЕВ ВАЛЕРИЙ ЭДМУНДОВИЧ, КАМЕНСКИЙ СЕРГЕЙ ВЕНИАМИНОВИЧ, ХРИСТЕНКО ОЛЬГА ЮРЬЕВНА

МПК / Метки

МПК: H03M 13/00

Метки: кодер

Опубликовано: 23.12.1992

Код ссылки

<a href="https://patents.su/5-1783623-koder.html" target="_blank" rel="follow" title="База патентов СССР">Кодер</a>

Предыдущий патент: Устройство для исправления ошибок

Следующий патент: Устройство для мажоритарного декодирования

Случайный патент: Форсунка для распыления расплавов водой