Устройство для исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1783622

Автор: Василенко

Текст

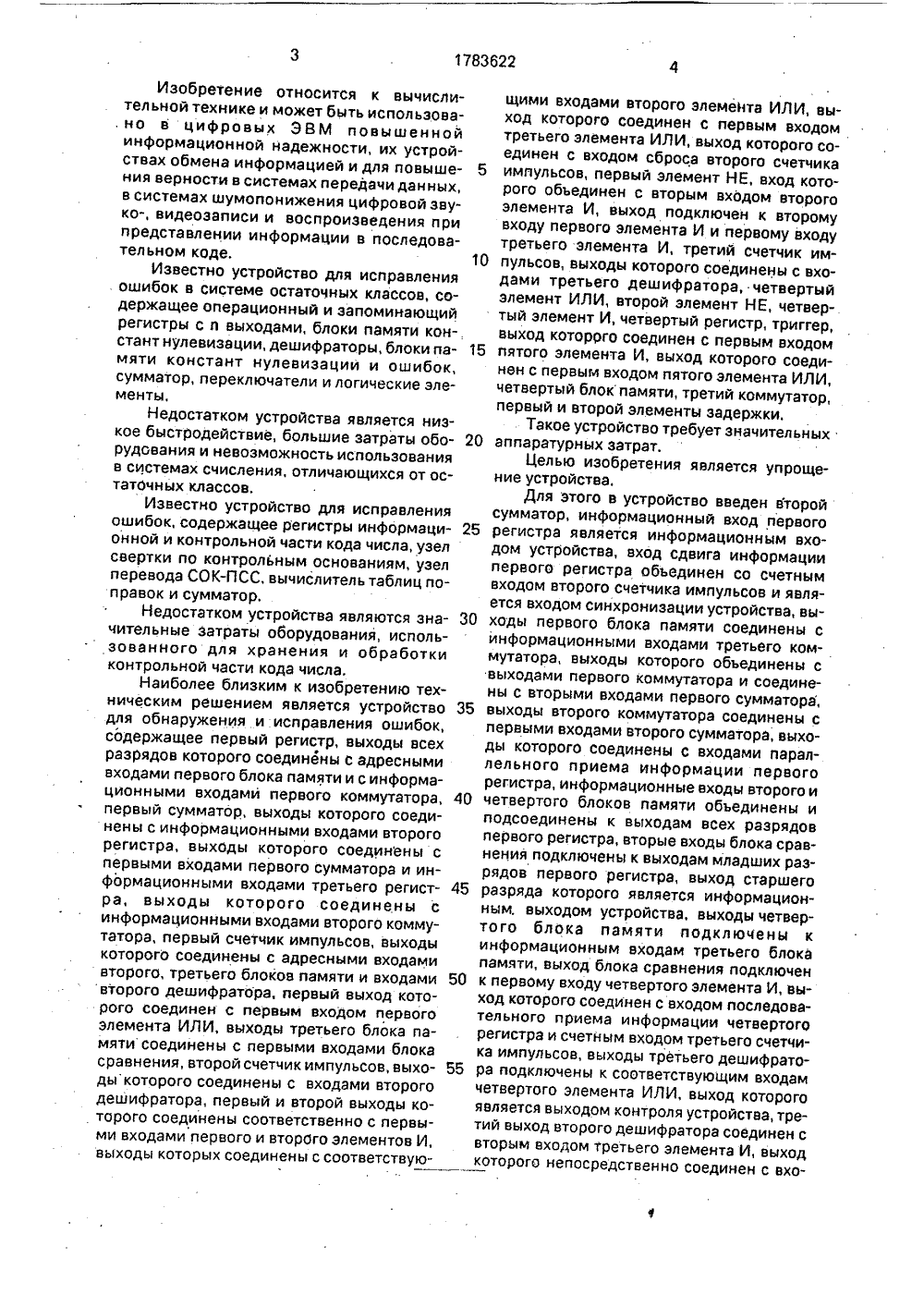

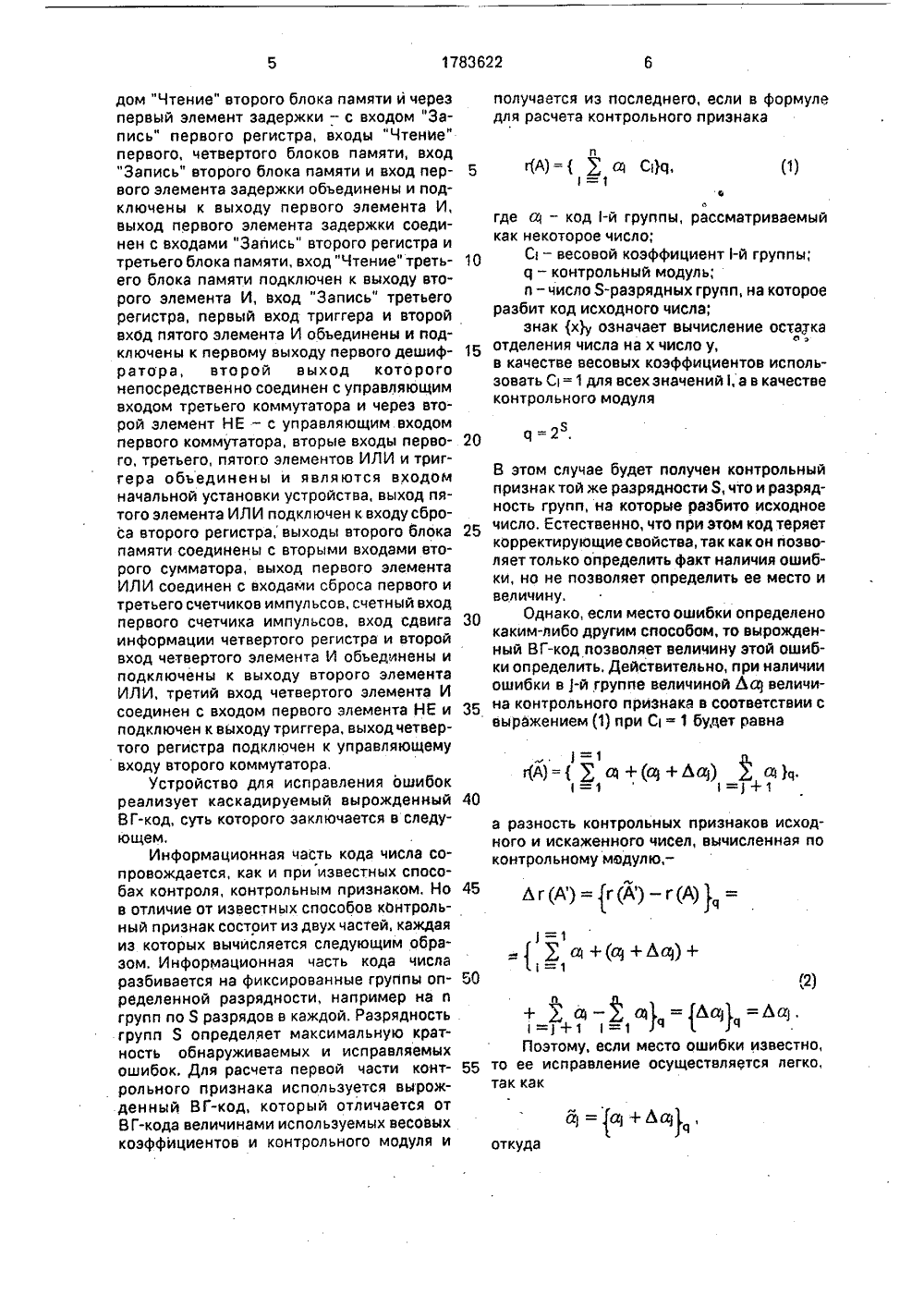

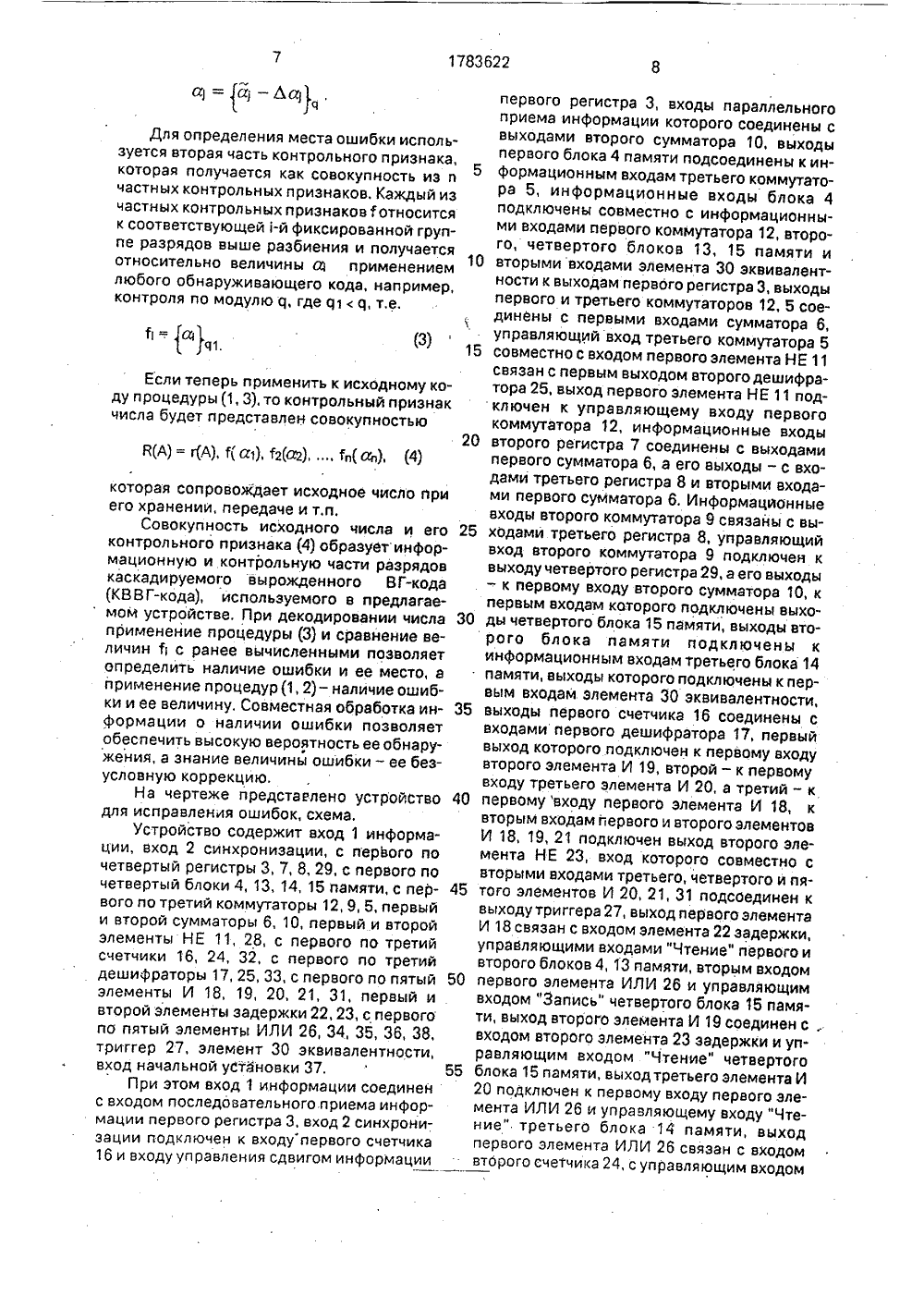

: р ф,)ЯВ" Ь:фф"Цй д"фРи 6 -ЯДа%сежРЕТ ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(21) 4791290/24 (22) 13.02.90 (46) 23,12.92, Бюл, М 47 (72) В.С.Василенко и В,В.Василенко (56) Авторское свидетельство СССР йг 842820, кл. 6 06 Г 1108, 1981.Авторское свидетельство СССР М 1580568, кл, Н 63 М 13/22, 1989. (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК (57) Изобретение относится к вычислитель- ной технике и может быть использовано в устроиствах памяти и обмена информации в системах шумопонижения цифровой звуко-, видеозаписи и воспроизведения. Целью изобретения является упрощение устройства. Устройство содержит регистры 3, 7, 8, 29, блоки 4, 13, 14, 15 памяти, коммутаторы 12, 9, 5, сумматоры 6, 10, элементы НЕ 11, 28, счетчики импульсов 16, 24, 32, дешифраторы 17, 25, ЗЗ, элементы ИЛИ 26, 34, 35, 36, 38, триггер 27, элемент 30 эквивалентности, .1 ил,Рюю 7ны с информационными входами второго регистра, выходы которого соединены с первыми входами первого сумматора и информационными входами третьего регистра, выходы которого соединены с информационными входами второго коммутатора, первый счетчик импульсов, выходы которого соединены с адреснычи входами второго, третьего блоков памяти и входами первого дешифратора, первый выход которого соединен с первым входом первого элемента ИЛИ, выходы третьего блока памяти соединены с первыми входами блока сравнения, второй счетчик импульсов, выходы которого соединены с входами второго дешифратора, первый и второй выходы которого соединены соответственно с первыми входами первого и второго элементов И, выходы которых соединены с соответствующими входами второго элемента ИЛИ, выход которого соединен с первым входом третьего элемента ИЛИ, выход.кдтброго соединен с первым входом третьего элемента ИЛИ, выход которого соединен с входом сброса второго счетчика импульсов, первый элемент НЕ, вход которого объединен с вторым входом второго элемента И, выход подключен к второму входу первого элемента И и первому входу третьего элемента И, тре тий счетчик импульсов, выходы которого соединен с входами третьего дешифратора, выходы которого соединены с входами третьего дешифратора, четвертый элемент ИЛИ, второй элемент НЕ, четвертый элемент И, четвертый регистр, триггер, выход которого соединен с первым входом пятого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, четвертый блок памяти, третий коммутатор, первый и второй элементы задержки, о т л ич а ю щ е е с я тем, что, с целью упрощения устройства, в него введен второй сумматор, информационный вход первого регистра является информационным входом устройства, вход сдвига информации первого регистра объединен со счетным входом второго счетчика импульсов и является входом синхронизации устройства, выходы первого блока памяти соединены с информационными входами третьего коммутатора, входы которого объединены с выходами первого коммутатора и соединены с вторыми входами первого сумматора, выходы второго коммутатора соединены с входами параллельного приема информации первого регистра, информационные входы второго и четвертого блоковпамяти объединены и подсоединены к выходам всех разрядов первого регистра, вторые входы блока сравнения подключены к выходам младших разрядов первого регистра, выход старшего разряда является информационным выходом устройства, выходы четвертого блока памяти подключены к информационным входам третьего блока памяти, выход блока сравнения подключен к первому входу четвертого элемента И, выход которого соединен с входом последовательного приема информации четвертого регистра и со счетным входом третьего счетчика импульсов, выходы третьего,дешифратора подключены к соответствующим входам четвертого элемента ИЛИ, выход которого является выходом контроля устройства, третий выход второго дешифратора соединен с вторым входом третьего элемента И, выход которого непосредственно соединен с входом "Чтение" второго блока памяти и через первый элемент задержки с входом "Запись" первого регистра, входы "Чтение" первого, четвертого блоков памяти, вход "Запись" второго блока памяти и вход первого элемента задержки объединены и йодключены к выходу первогоэлемента И, выход первого элемента задержки соединен с входами "Запись" второго регистра и третьего блока памяти, вход "Чтение"третьего блока памяти подключен к выходувторого элемента И, вход "Запись" третьего регистра, первый вход триггера и второйвход пятого элемента И объединены и подключены к первому выходу первого дешифратора, второй выход которого непосредственно соединен с управляющим входом третьего коммутатора и через второй элемент НЕ с управляющим входом первого коммутатора, вторые входы первого,третьего, пятого элементов ИЛИ и триггера объединены и являются входом начальной установки устройства, выход пятого элемента ИЛИ подключен к входу сброса второго регистра, выходы второго блока памяти соединены с вторыми входами второго сумматора, выход первого элемента ИЛИ соединен с входами сброса первого и третьего счетчиков импульсов, счетный вход первого счетчика импульсов, вход сдвига информации четвертого регистра и второй вход четвертого элемента И объединены и подключены к выходу второго элемента ИЛИ, третий вход четвертого элемента И соединен с входом первого элемента НЕ и подключен к выходу триггера, выход четвертого регистра подключен к управляющему входу второго коммутатора,Изобретение относится к выся к вычисли- щими входами второго элемента ИЛИ, вытельной технике и может быть испол ьзова- ход которого соединен с первым входомв цифровых ЭВМ повышенной третьего элемента ИЛИинфо ма ионнф р ц ой надежности, их устрой- единен с входом сб снта, выход которого соствах обмена инфо ма им с роса второго счетчикаформациеи и для повыше импульсов, первый элемент НЕ, вхо котния верности в системах передачи данных бх, рого о ъединен с вторым входом вто огов системах шумопонижения цифровой зву- эле Имента , выход подключен к второмго элемента и первому входко-, видеозаписи и воспроизведения лри входу перво Ипредставлении информации в последова- третьего элемента Ительном коде,лемента, третий счетчик имИзв1 л0 пульсов, выходы которого соединены с вхоошибок в и тзвестно устройство для исправления дами третьего фг дешифратора, четвертыйеок в системе остаточных классов, со- элемент ИЛИ втород ржащее операционный и запоминающий тый эле е И, второи элемент НЕ, четвеэлемент, четвертый регистр, триггер,стантн лрегистры с л выходами, блоки памяти кон- выход которрго соеулевизации,дешифраторы, блоки па пятого элемента И, выхо кото динен с первым входоммяти констант н левиза ии, выход которого саедиу ации и ошибок, нвн с первым входом пятого элемента ИЛИ,менты.сумматор, переключатели и логические эле- четвертый блок пак памяти, третий коммутатор,первый и второй элементы задержки.кое быстедостатком устройства является низ- Такое уструстроиство требует значительныхруд ания и невозможность использованияовкое ыстродействие, большие затраты обо апларатурных зат а .атрат.ль изо ретения является упрощев системах счисления, отличающихся от ос- ние устройства.таточных классов, Для этого в устройство введен второйИзвестно устройство для исправления сумматор, информационный вход первогоошибок, содержащее регистры информаци регистра являе тся информационным вхоонной и контрольной части кода числа, узел дом устройс ва,т , вход сдвига информациипе ево аС Ксвертки по контрольным основаниям, узел первого регистра обт а о ъединен со счетнымперевода 0 -ПСС, вычислитель таблиц по- входом второго счетчика имп льсправок и сумматор.ч тчика импульсов и является входом синхронизации устройства, вылока памяти соединены сНедостатком устройства являются зна ходы первого бло аи входами третьего комчительные затраты оборудования, исполь- информационными вхо азованного для хранения и обработки мутатора, выходы которого объединены сНконтрольной части кода числа, выходами первого ком мутатора и соединеаиболее близким к изобретению тех- ны с вторыми входами пе вническим решением является устройство 35 выходы второго коммутатора соединены св рого сумматора, выходля обнаружения и исправления ошибок, первыми входами второгсодержащее первый регистр, выходы всех ды которого соединены с входами паралразрядов которого соединены с адресными лельного приема и фвходами первого блока памяти и с информа- регистра, информационные входы второго иционными входами первого коммутатора, 40 четвертого блоков памяти объединены им всех разрядовпервый сумматор, выходы которого соеди- подсоединены к выходам в хнены с информационными входами второго первого регистра, вторые входы блока сраврегистра, выходы которого соединены с нения подключены к выходам младших разпервыми входами первого сумматора и ин- рядов первого регистра, выход старшегоформационными входами третьего регист разряда которого является инфо мационра, выходы которого соединены с ным. выходом устройства, выходы четверамяти подключены кинформационными входами второго комму- того блока памяти итатора, первый счетчик импульсов, выходы информационным входам третьего блокал ка сравнения подключенкоторого соединены с адресными входами памяти, выход блока сравненвторого, третьего блоков памяти и входами 50 к первому входу четвертого элемента И, вьюгвторого дешифратора, первый выход кото- ход которого соединен с входом лоследор о соединен с первым входом первого тельного приема инфорледовам ин ормации четвертогОым входом третьего счетчиэлемента ИЛИ, выходы третьего блока ла- регистра и счетным входом тмяти соединены с первыми входами блока ка импульсов, выходы третьего дешифратосравнения, второй счетчик импульсов, выхо ра подключены к соотве соответствующим входамдыкоторого соединены с входами второго четвертого элемента ИЛИнта , выход которогороля устроиства, тредешифратора, первый и второй выходы ко- является выходом контролядешифратора соединен сторого соединены соответственно с первы- тий выход второго дешифратоми входами первого и вторОго элементов И, вторым входом третьего м И,етьего элемента , выходвыходы которых соединены с соответствую- которого нелосредственндственно соединен с входом "Чтение" второго блока памяти и через первый элемент задержки - с входом "Запись" первого регистра, входы "Чтение" первого, четвертого блоков памяти, вход "Запись" второго блока памяти и вход первого элемента задержки объединены и подключены к выходу первого элемента И, выход первого элемента задержки соединен с входами "Запись" второго регистра и третьего блока памяти, вход "Чтение" третьего блока памяти подключен к выходу второго элемента И, вход "Запись" третьего регистра, первый вход триггера и второй вход пятого элемента И объединены и подключены к первому выходу первого дешифратора, второй выход которого непосредственно соединен с управляющим входом третьего коммутатора и через второй элемент НЕ - с управляющим входом первого коммутатора, вторые входы первого, третьего, пятого элементов ИЛИ и триггера объединены и являются входом начальной установки устройства, выход пятого элемента ИЛИ подключен к входусброса второго регистра, выходы второго блока памяти соединены с вторыми входами второго сумматора, выход первого элемента ИЛИ соединен с входами сброса первого и третьего счетчиков импульсов, счетный вход первого счетчика импульсов, вход сдвига информации четвертого регистра и второй вход четвертого элемента И объединены и подключены к выходу второго элемента ИЛИ, третий вход четвертого элемента И соединен с входом первого элемента НЕ и подключен к выходу триггера, выход четвертого регистра подключен к управляющему входу второго коммутатора,Устройство для исправления ошибок реализует каскадируемый вырожденный ВГ-код, суть которого заключается в следующем,Информационная часть кода числа сопровождается, как и при известных способах контроля, контрольным признаком, Но в отличие от известных способов контрольный признак состоит из двух частей, каждая из которых вычйсляется следующим образом. Информационная часть кода числа разбивается на фиксированные группы определенной разрядности, например на и групп по Я разрядов в каждой. Разрядность групп 3 определяет максимальную кратность обнаруживаемых и исправляемых ошибок. Для расчета первой части контрольного признака используется вырожденный ВГ-код, который отличается от В Г-кода величинами используемых весовых коэффициентов и контрольного модуля иполучается из последнего, если в формуледля расчета контрольного признака где а - код 1-й группы, рассматриваемый как некоторое число;С - весовой коэффициент 1-й группы; о - контрольный модуль;и - число 3-разрядных групп, на котороеразбит код исходного числа;знак (х)у означает вычисление остатка 15 отделения числа на х число у,в качестве весовых коэффициентов использовать С =1 для всех значений 1, а в качестве контрольного модуля 20 ч=2=+ а разность контрольных признаков исходного и искаженного чисел, вычисленная поконтрольному модулю, -1=1/2) Поэтому, если место ошибки известно,55 то ее исправление осуществляется легко, так как а 1 = а+Ьа откуда В этом случае будет получен контрольный признак той же разрядности 8, что и разрядность групп, на которые разбито исходное 25 число Естественно чтоприэтомкодтеряеткорректирующие свойства, так как он позволяет только определить факт наличия ошибки, но не позволяет определить ее место и величину,Однако, если место ошибки определенокаким-либо другим способом, то вырожденный ВГ-код позволяет величину этой ошибки определить. Действительно, при наличии ошибки в 3-й группе величиной Ьа величи на контрольного признака в соответствии свыражением (1) при С = 1 будет равнаа = а; - Ла 1 В(Д) = г(Д), а), 2(а 2), , Ь(а.), (4) первого регистра 3, входы параллельного приема информации которого соединены сдля определения места ошибки исполь- вцходами второго сумматора 10, выходы зуется вторая часть контрольного признака, первого блока 4 памяти подсоединены к инкоторая получается как совокупность из и ф рмационным входам третьего коммутаточастныхконтрольныхпризнаков, Каждыйиз Ра 5, информационные входы блока 4 частных контрольныхпризнаковфотносится подключены совместно с информационнык соответствующей -й фиксированнои груп- ми входами пеРвого коммутатора 12, второпе разрядов выше разбиения и получается "о четвеРтого блоков 13, 15 памяти и относительно величины а применением "0 втоРыми входами элемента 30 эквивалент- любого обнаруживающего кода, например, ности к выходам первого регистра 3, выходы контроля по модулю ц, где о 1и, т.е. первого и третьего коммутаторов 12, 5 соединены с первыми входами сумматора 6,= а управляющий вход третьего коммутатора 515 совместно с входом первого элемента НЕ 11связан с первым выходом второгодешифраЕсли теперь применить к исходному ко- тора 25, выход первого элемента НЕ 11 подду процедуры(1,3),то контрольный признак ключен к управляющему входу первого числа будет представлен совокупностью коммутатора 12, информационные входы20 второго регистра 7 соединены с выходамипервого сумматора 6, а его выходы - с входами третьего регистра 8 и вторыми входакоторая сопровождает исходное число при ми первого сумматора 6, Информацаонные его хранении, передаче и т.п. входы второго коммутатора 9 связаны с выСовокупность исходного числа и его 25 ходами третьего регистра 8, управляющий контрольного признака(4) образуетинфор- вход второго коммутатора 9 подключен к мационную и контрольную части разрядов выходучетвертого регистра 29, а его выходы каскадируемого вырожденного ВГ-кода - к первому входу второго сумматора 10, к (КВ В Г-кода), используемого в предлагае- первым входам которого подключены выхо мом устройстве. При декодировании числа 30 дц четвертого блока 15 памяти, выходы втоприменение процедуры (3) и сравнение ве- рого блока памяти подключены к личин 1 с ранее вычисленными позволяет информационным входам третьего блока 14 определить наличие ошибки и ее место, а памяти, выходы которого подключены к перприменение процедур(1,2)-наличиеошиб- вцм входам Элемента 30 эквивалентности, ки и ее величину. Совместная обработка ин выходы первого счетчика 16 соединены с формации о наличии ошибки позволяет входами первого дешифратора 17, первый обеспечить высокую вероятность ее обнару- выход которого подключен к первому входу жения, а знание величины ошибки - ее без- второго элемента И 19, второй - к первому условную коррекцию, входу третьего элемента И 20, а третий - кНа чертеже предстарлено устройство 40 первомувходу первого элемента И 18, к для исправления ошибок, схема, вторым входам первого и второго элементовУстройство содержит вход 1 информа- И 18, 19, 21 подключен выход второго элеции, вход 2 синхронизации, с перЬого по мента НЕ 23, вход которого совместно с четвертый регистры 3, 7, 8, 29, с первого по вторыми входами третьего, четвертого и пячетвертый блоки 4, 13, 14, 15 памяти, с пер того элементов И 20, 21, 31 подсоединен к вого по третий коммутаторы 12, 9, 5, первый выходу триггера 27, выход первого элемента и второй сумматоры 6, 10, первый и второй И 18 связан с входом элемента 22 задержки, элементы НЕ 11, 28, с первого по третий управляющими входами "Чтение" первогои счетчики 16, 24, 32, с первого по третий второго блоков 4, 13 памяти, вторым входом дешифраторы 17, 25, 33, с первого по пятый 50 первого элемента ИЛИ 26 и управляющим элементы И 18, 19, 20, 21, 31, первый и входом "Запись" четвертого блока 15 памявторой элементы задержки 22,23, с первого ти, выход второго элемента И 19 соединен с .по пятый элементы ИЛИ 26, 34, 35, 36, 38, входом второго элемента 23 задержки и уптриггер 27, элемент 30 эквивалентности, равляющим входом "Чтение" четвертого вход начальной установки 37. 55 блока 15 памяти, выход третьего элемента ИПри этом вход 1 информации соединен 20 подключен к первому входу первого элес входом последовательного приема инфор- мента ИЛИ 26 и управляющему входу "Чтемации первого регистраЗ, вход 2 синхрони- ние" третьего блока 14 памяти, выход зации подключен к входупервого счетчика первого элемента ИЛИ 26 связан с входом 16 и входу управления сдвигом информации втерого счетчика 24, с управляющим входом"Сдвиг" четвертого регистра 29 и первыми входами четвертых элементов ИЛИ 36 и И 31, к третьему входу которого подключен выход элемента 30 эквивалентности, выход второго элемента 22 задержки подключен к управляющим входам "Запись" второго регистра 7 и третьего блока 14 памяти, выход третьего элемента 23 задержки связан с управляющим входом параллельного приема информации "Запись" первого регистра 3, выходы второго счетчика 24 подключены к адресным входам "Адрес" третьего и четвертого блоков 14, 15 памяти и входам второго дешифратора 25, второй выход которого связан с первым входом третьего элемента ИЛИ 35, управляющим входом "Запись" третьего регистра 8, первым входом четвертого элемента И 21 и первым входом триггера 27, выход пятого элемента И 31 подключен к входу последовательного приема информации четвертого регистра 29 и входу третьего счетчика 32, выходы третьего счетчика 32 соединены с входами третьего дешифратора 33, все выходы которого, кроме нулевого и первого, соединены с входами второго элемента ИЛИ 34, выход четвертого элемента И 21 связан с входом установки в нуль второо регистра 7, вход начальной установки 37 подключен к вторым входам триггера 27, третьего, четвертого и пятого элементов,ИЛИ 35, 36, 38, выход третьего элемента ИЛИ 35 связан с входами установки в нуль второго и третьего счетчиков 24, 32, выход четвертого элемента ИЛИ 36 подсоединен к входу установки в нуль первого счетчика 16, выход старшего разряда первого регистра 3 является информационным, а выход второго элемента, ИЛИ - контрольным выходом устройства,Регистр 3 предназначен для приема, хранения и сдвигов Я-разрядных двоичных чисел. Прием осуществляется по Я-разрядным входам параллельного приема информации при наличии разрешающего сигнала на управляющем входе "Запись" или по одноразрядному входу последовательного приема "Инф." при наличии разрешающего сигнала на управляющем входе "Сдвиг", В последнем случае осуществляется сдвиг содержимого регистра на один разряд и запись в его младший разряд информации по входу последовательного приема. Выходная информация снимается со всех разрядов регистра по Я-разрядной шине и, кроме того, с последнего, Я-го разряда, являющегося выходом устройства,Второй и третий регистры 7, 8 предназначены для приема и хранения 5-разрядных двоичных чисел, Прием осуществляется при наличии разрешающего сигнала на управ 5 10 15 20 25 30 35 ляющем входу "Запись", Съем информации в регистре 8 осуществляется с прямых, а в регистре 9 - с инверсных выходов.Четвертый регистр 29 предназначен для приема, хранения и сдвигов одноразрядных двоичных сигналов, поступа.ъщих на вход последовательного приеМа информации, Прием и сдвиг этих сигналов осуществляется при наличии разрешающего сигнала на управляющем входе "Сдвиг", Емкость регистра должна быть рассчитана на (и+1) разрядов, где и - число груйп разбиения исходного контролйруемого числа, Сьем информации осуществляется с последИ,го разряда. После записи всей информации на регистре окажутся записанными в позиционном коде номера групп;где обнаружены искажения, Под позиционным понимается код, в котором единица на некоторой )-й позиции свидетельствует о наличии ошибок в)-й группе, а нуль - об ее отсутствии в этой же группе.Первый и второй блоки 4, 13 памяти предназначены для табличного расчета выходных кодов по входным (перекодировки). В качестве этих блоков памяти могут использоваться, например, постоянные (долговременные) запоминающие устройства на 2 ячеек памяти, где Я - разрядность групп3разбиения исходного контролируемого числа. В каждой ячейке первого блока 4 памяти при этом хранится заранее рассчитанное по модулю а отрицательное 3-разрядное значение кода адреса этой ячейки=а-КА),где а - величина контрольного модуля вырожденного ВГ-кода;г(А) - код адреса ячейки, соответствующий контрольному признаку числа, представленного в вырожденном ВГ-коде.В ячейках второго блока 13 памяти хранятся щ-разрядные, заранее рассчитанные частные контрольные признаки" 1")где а - адрес ячейки, соответствующий коду 1-й фиксированной группы разбиения исходного контролируемого числа.Считывание информации осуществляется по разрешающим сигналам на управляющих входах "Чтение".Третий и четвертый блоки 14, 15 памяти предназначены.для записи, хранения и последующего считывания информации, поступающей на соответствующие входы, В качестве этих блоков памяти могут исг оль1783622зоваться, например, оперативные запоми- Ла 1 - код ошибки в)-й группе, рассчинающие устройства(ОЗУ) на(п+1) ячеек па- танный в накапливаю ем с (мяти. В ячейки т еть гр его блока 14 памяти вый сумматор 6 и второй регистр 7).записываются а-разрядные частные конт- Операцииперации сложения по модулю в суммарольные признаки групп разбиения исход торах 6, 10 реализуются естественным обраного кода, рассчитанные во втором блоке 13 зом, если эти суммато Яячеики четвертого блока 15 па- величина модуля выбрана равноймяти - Я-разрядные группы разбиения исходного кода с выхода первого регистра 3 = 2.при наличии разрешающего сигнала на упЦ=равляющем входе "Запись". Считывание Первые счетчик 16 финформации осуществляется по разреша- обеспечивают подсчет числа синхроимпульющему сигналу на управляющем входе сов, соответствующих фтение, дрес ячейки для записи или разрядам в каждой группе разбиения контсчитывания информации определяется ко ролируемого числа или в их частных контдом, подаваемым на адресные входы рольных признаках, которые принимаютсянАдр,и ОЗУ с выходов второго счетчика 24, в первый регистр 3, и и авлКомм тато ы 5, 9 12 иу ры предназначены емом. При приеме групп разбиения и контдля передачи на свои выходы Я-разрядных рольного признака вырожденного ВГ-кодакодов, поступающих на их информацион необходимо обеспечить счет от нуля до (Яные входы, при наличии разрешающих сиг-1)-Я состояний счетчика, а при приеме часизнаков - от нуля доналов на управляющих входах. В качестве тных контрольных признаяний счетчика, т,е. необходикоммутаторов могут использоваться, напри- (п) - гп состояний счетчик,мер, группы из двухвходовых элементов И, мо изменять модуль счета, Это обеспечивауправляющие входы которых объединены в 25 ется принудительной установкой первогоодин общий управляющий вход. счетчика 16 в нулевое состояние сигналамиСумматоры 6, 10 предназначены для с (Я)-го или (а - 1)-го выходов первого десложения по модулю ц Я-разрядных чисел, шифратора 17 через первый или третий элеП вьпоступающих на их первые и вторые входы. менты И 18, 20, выходные сигналх дные сигналы которыхервый сумматор 6 вместе с вторым регист объединяются первым элементом ИЛИ 26 иром 7 образуют при этом накапливающий через четвертый элемент ИЛИ 36 поступаютсумматор, реализующий функцию расчета навходустановкивнульпервогосчетчика 16.величины ошибки в некоторой, )-й, группе Триггер 27 - триггер со счетным входомобеспечивающий управление третьим элеЛа = (г(А) - г(Ац = 35 ментом И 20 непосредственно и четвертымэлементом И 21 через элемент НЕ 28, изменяя тем самым модуль счета первого счетчика 16, Его начальная установка в нулевоесостояние обеспечивается по второму входу40 В сигналом с входа 37 начальной установкиустройства,где ггА) =га - контропеный признак об- Вторые счетчик 24 и дешифратор 26обеспечивает подсчет числа принимаемыхрабатываемого числа, вновь рассчитанный групп разбиения и их частных контрольныхв данном устройстве; 45 признаков. С этой целью на вход счетчикаг(А) - сопровождающий контролируе- поступают сигналы окончания приема групмое число контрольный признак. пы разбиения или частного контрольногоВо втором сумматоре 10 производится признака с выхода первого элемента ИЛИсложение кода)-й группы со считываемым с 26, Для приема всех групп разбиения, вклютретьего регистра 8 инверсным кодом ошиб чая контрольный признак вырожденногоки в этой группе, что эквивалентно опера- ВГ-кода, или их частных контрольных приции вычитания и образованию знаков необходимо обеспечить счет от нуляисправленного кода )-й группы до и, т.е. (п+1) состояний счетчика. Поэтомупринудительная установка в нуль второгоа; = а, - .Ьа 1 55 счетчика 24 осуществляется сигналом с второго выхода второго дешифратора 25, соответствующего (п + 2)-му, включая нулевое,ваемой из четвертого блока 15 памяти;состоянию вто ого счетчитий элемент ИЛИ 35, Через этот же элементИЛИ 35 производится и начальная установка в нулевое состояние второго и третьегосчетчиков 24, 32. Сигналом с первого, п-го,выхода второго дешифратора 25, соответствующего (и+1)-му состоянию второго счетчика 24, управляются первый коммутатор 5непосредственно и третий коммутатор 12через элемент НЕ 11, Этим обеспечиваетсянепосредственная передача содержимогопервого регистра 3 (и групп разбиения) в 10накапливающий сумматор (первый сумматор 6, второй регистр 7) или через блок 4памяти - отрицательного значения контрольного признака вырожденного ВГ-кода- (и+1)-я группа, 15Первый элемент 21 задержки обеспечивает формирование выходного сигнала дляустановки второго регистра 7 в нулевое состояние, задержанного относительно входного на время, равное времени записи 20информации в третий регистр 8,Второй элемент 22 задержки обеспечивает формирование выходного сигнала, задержанного относительно входного навремя, равное сумме времен выборки информации из первого или второго блоков 4,13 памяти, передачи через первый коммутатор 5 и сложения в первом сумматоре 6.Третий элемент 23 задержки обеспечивает формирование выходного сигнала, задержанного относительно входного навремя, равное сумме времен выборки информации из четвертого блока 15 памяти исложения во втором сумматоре 10,Элемент 30 эквивалентности предназначен для сравнения кодов двух гп-разрядных чисел, подаваемых на его выходы, ивыработки сигнала, соответствующего единичному уровню, при их несравнении,40Третий счетчик 32, третий дешифратор 33 и второй элемент ИЛИ 34 обеспечивают выработку сигнала на контрольном выходе устройства и возможности или невозможности исправления ошибки той кратности,.ко торая обнаружена устройством, Так как в устройстве обнаруженными могут быть ошибки любой кратности, а исправленными - ошибки в пределах одной из групп разбиения, то счетчик 32 должен обеспечить счет 50 от нуля до (и). При любом состоянии счетчика, отличном от нуля и единицы, что свидетельствует о том, что обнаружены ошибки в более чем одной группе разбиения, необходимо вырабатывать сигнал невозможно сти исправления. С этой целью с третьего дешифратора 33 на второй элемент ИЛИ на (и) входов подаются сигналы со всех выходов, кроме нулевого и первого, т,е. с (и - Я, выходов. Устройство работает следующим образом. В исходном состоянии первый, второй и третий счетчики 16, 24, 32, второй регистр 7 и триггер 27 находятся в нулевом состоянии, установка в которое производится в предыдущем такте или по входу 37 начальной установки, В четвертом блоке памяти 15 хранится поступившее в предыдущем такте на контроль слово, записанное в ячейки по Я разрядов в каждой в соответствии с принятым в коде разбиением на группы, а в третьем блоке 14 памяти - его частные контрольные признаки, В третьем регистре 8 хранится рассчитанная в предыдущем такте величина ошибки в )-й группе. В четвертом регистре 29 хранится позиционный код номера искаженной группы ) таким образом, что в старшем (выходном) разряде записан признак наличия или отсутствия ошибок в первой (нулевой) группе разбиения. В установившемся режиме, т.е. при приеме второго и последующих контрольных слов, в момент перевода счетчиков 16, 24, 32 в нулевое состояние сигналом установки в нуль второго счетчика 24 с выхода второго дешифратора 25 устанавливается в нуль триггер 27. При этом на выходе второго элемента НЕ 28 появляется сигнал, разрешающий прохождение сигналов через элементы И 18, 19, 21, в результате чего на выходе второго элемента И 19 появится сигнал единичного уровня, так как и на первый вход этого элемента с нулевого выхода первого дешифратора 17 будет подан разрешающий сигнал. Сигнал с выхода второго элемента И 19 разрешит чтение из четвертого блока 15 памяти информации первой (нулевой) группы разбиения предыдущего слова, в результате того, что на адресные входы этого блока памяти с выхода второго счетчика 24 подан код, соответствующий номеру первой (нулевой) группы, так как этот счетчик установлен в нулевое состояние. Код сосчитанной первой (нулевой) группы подается на второй вход второго сумматора 10, на первый вход которого при наличии единичного сигнала на выходе четвертого регистра 29 поступит код ошибки с третьего регистра 8 через второй коммутатор 9. Если в коде первой (нулевой) группы ошибка не обнаружена, то на выходе четвертого регистра 29 сигнал будет иметь нулевой уровень и код ошибки через второй коммутатор 9 на первый вход второго сумматора 10 передан не будет. Таким образом, на выходе второго сумматора и, следовательно, на входах параллельного приема инфорк;ации первого регистра 3 будет сформирован код скорректированной первой (нулевой) группы, если ошибка в этой группе была обнаружена, иликод этой же неискаженной группы в противном случае. Этот код записывается в первыйрегистр 3 разрешающим сигналом на управляющем входе "Запись", который формируется на выходе второго элемента 23 5задержки по сигналу чтения из четвертогоблока 15 памяти и имеет относительно данного сигнала соответствующую задержку.Таким образом, к моменту поступления первого информационного символа нового 10слова в первый регистр 3 записана скорректированная первая группа предыдущегослова.При поступлении первого информационного символа очередного слова и связанного с ним синхросигнала осуществляетсясдвиг информации первого регистра 3 наодин разряд и запись в него первого информационного символа, При этом из старшегоразрядапервого регистра на информационный выход устройства поступает первыйсимвол предыдущего скорректированногослова, а первый счетчик 16 переводится вочередное состояние,Эти процессы повторяются Я раз, при 25этом на выход устройства выдается перваягруппа предыдущего слова, в первый регистр 3 записывается первая группа новогослова, а первый счетчик 16 переводится вЯ-е состояние, считая нулевое первым, При 30этом на (Я - 1)-м выходе дешифратора 17 появится сигнал, который, проходя через открытый первый элемент И 18, первый ичетвертый элементы ИЛИ 26, 36, установитпервый счетчик 16 в нулевое состояние, 35обеспечит сдвиг содержимого четвертогорегистра 29 на один разряд и как разрешающий сигнал поступит на управляющиевходы "Чтение" первого и второго блоков 4,13 памяти и на управляющий вход "Запись" 40четвертого блока 15 памяти. Кроме того,этот же сигнал после задержки во второмэлементе 22 задержки поступит как разрешающий сигнал на управляющие входы "Запись" второго регистра 7 и третьего блока 4514 памяти, По этим разрешающим сигналампо входной Я-разрядной группе сигналов,снимаемой с выхода первого регистра 3,будет сосчитана и передана на информационныевходы третьего коммутатора 5 величинаиз первого блока 4 памяти, будетсосчитана из второго блока 13 памяти и записана в третий блок 14 памяти величиначастного контрольного признака Г и записана во второй регистр 7 сумма содержимого. 55этого же регистра 7, подаваемого на второйвход первого сумматора 6, и подаваемого напервый вход этого же сумматора кода первой, а затем последующейгруппы разбиения контролируемого слова, передаваемой через первый коммутатор 12, или величины , передаваемой через третий коммутатор 5 после приема всех групп информационной части контролируемого слова. Кроме того, этим же разрешающим сигналом, поступающим на управляющий вход "Запись" четвертого блока 15 памяти, осуществляется прием кода обрабатываемой группы разбиения с выхода первого регистра 3, Одновременно с этим разрешающим сигналом с выхода первого элемента ИЛИ 26 переводится в очередное состояние второй счетчик 24,Описанные процедуры повторяются для каждой последующей группы разбиения данного слова, пока второй счетчик 24 и вместе с ним второй дешифратор 25 не будут переведены в (и+1)-е состояние, За это время из четвертого блока 15 памяти будет считана вся информационная часть предыдущего слова, которая после исправления во втором сумматоре 10 будет передана на первый регистр 3 и с его выходного Я-го разряда - на выход устройства. Кроме того, - в четвертый блок 15 памяти будут записаны все и группы а проверяемого слова, а в третий блок 14 памяти - их частные контрольные признаки й, во втором регистре 7 - сформирован контрольный признак проверяемого слова для вырожденного ВГ-кода г(А), При этом на первом выходе второго дешифратора 25, соответствующего (п+1)- му состоянию второго счетчика 24, появляется сигнал, разрешающий передачу информации с первого блока 4 памяти через первый коммутатор 5 и запирающий через первый элемент НЕ 11 третий коммутатор 12, в результате этого после приема (и+1)-й группы контролируемого слова, т.е. после приема его контрЬльного признака для вы-рожденного БГ-кода г(А), на выходе первого блока 4 памяти формируется величина= ц - г(А), которая передается через коммутатор 5 на сумматор 6, После сложения во второй регистр 7 записывается величина ошибки Ла 1 и второй счетчик 24 переводится в (п+2)-е состояние, что приводит к появлению на втором выходе второго дешифратора 25 сигнала, которым устанавливается в нулевое состояние второй и третий счетчики 2432, переводится в единичное состояние триггер 27 и осуществляется перепись ошибки ЬХ, из второго регистра 7 в третий регистр 8, При переводе в единичное состояние триггера 27 закрываются первый и второй элементы И 18, 19 и открываются третий и четвертый элементы1783622 и второй дешифратор 25 не окажутся в состоянии (и+2), при этом сигналом с второго выхода второго дешифратора 25 через открытый четвертый элемент И 21 и пятый 5 элемент ИЛИ 38 устанавливается в нулевоесостояние второй регистр 7 и через третий элемент ИЛИ 35 обнуляются второй и третий счетчики 24, 32, переводится в нулевое состояние триггер 27. Устройство готово к 10 приему очередного слова, При этом за время приема и обработки контрольных признаков в четвертый регистр 29 будет записан позиционный код места ошибки в принятом на коррекцию слове, в третий ре гистр 8 - величина этой ошибки и с контрольного выхода 2 - выдан сигнал невозможности правильной коррекции, если число ошибок превысит функциональные возможности устройства.20 При включении устройства сигналом начальной установки по входу 37 устанавливаются в нулевое состояние счетчики 16, 24, 32, триггер 27, регистр 7, Состояние регистров 3, 8, 29 безразлично, так как предыду щего такта работы устройства не было и сего выхода 1 в течение приема первого слова может сниматься любая информация, которая потребителем использована не будет,В результате работы устройства с выхо да Я-го разряда первого регистра 3 будетснят последовательный код скорректированного слова, поступившего на информационный вцход 1 устройства в предыдущем такте, а на контрольном выходе 2 устройст ва будет сформирован признак возможности или невозможности коррекции вновь принятого слова. Это позволяет потребителю принять решениео воэможности или невозможности использования информации 40 по выходу 1 устройства, Причем сигнал неправильной коррекции на контрольном выходе 2 формируется только тогда, когда характер искажения исходного слова превышает возможности кода. Прототип таким свой ством не обладает, и поскольку правильная илинеправильная коррекция в нем производится всегда, а информация о ее правильности или неправильности не выдается, то потребитель вынужден всегда использовать скорректи рованное или дополнительное искаженноеслово, что может привести к нежелательным для него последствиям. И 20, 21. Этим блокируются цепи формирования управляющих сигйалов для получения с использованием вырожденного ВГ-кода и обеспечиваются условия для определения мест возникновения и количества ошибок, При этом прием информации в первый регистр 3 продолжается, но первым счетчиком 16 и дешифратором 17 обеспечивается подсчет символов в группе от нуля до (щ). Это достигается тем, что при переходе первого счетчика 16 в состояние (а) на соответствующем выходе первого дешифратора 17 появляется сигнал, который поступает через открытый третий элемент И 20 и первый элемент ИЛИ на вход установки в нуль первого счетчика 16, обеспечивая его принудительный сброс, Этот же сигнал поступает на управляющий вход "Чтение" третьего блока 14, обеспечивая считывание частных контрольных признаков текущего контролируемого слова, рассчитанных на этапе приема информационной части этого слова. Это считывание осуществляется по адресам, формируемым вторым счетчиком 24, изменяющим свое состояние под воздействием сигналов с выхода первого элемента ИЛИ 26. Частные контрольные признаки с выхода третьего блока 14 памяти подаются на первые входы элемента 30 эквивалентности, на вторые входы которого поступают частные контрольные признаки с выхода первых в разрядов первого регистра 3. При их несовпадении на выходе элемента 30 эквивалентности формируется единичный сигнал, поступающий на третий вход пятого элемента И 31. Так как-в этот момент на первом входе этого элемента И 31 имеется разрешающий сигнал с выхода первого элемента ИЛИ 26, а на втором - разрешающий сигнал с выхода триггера 27, то элемент И 31 открывается и сигнал с выхода элемента 30 эквивалентности поступает на вход последовательного приема информации четвертого регйстра 29 и на вход третьего счетчика 32. Поскольку одновре- менно с этим на управляющий вход "Сдвиг" четвертого регистра 29 поступает разрешающий сигнал, то в этот регистр последовательно записываются сигналы обнаружения или необнаружения ошибок в каждой из групп контролируемого слова, а третий счетчик 32 обеспечивает подсчет числа обнаруженных ошибок, Если число ошибок превышает одну, то сигналы со всех выхо дов третьего дешифратора через второй эл5 мент ИЛИ на (и - 2) входов 34 как сигнал невозможности правильной коррекции поступаютна контрольный выход устройства.Описанная процедура выполняется (и+1) раз до тех пор, пока второй счетчик 24 Формула изобретения 5 Устройство для исправления ошибок,содержащее первый регистр, выходы всех разрядов которого соединены с адресными входами первого блока памяти и с информационными входами первого коммутатора, первый сумматор, выходы которого соедине

СмотретьЗаявка

4791290, 13.02.1990

КИЕВСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ РАДИОТЕХНИЧЕСКОЕ УЧИЛИЩЕ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

ВАСИЛЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ВАСИЛЕНКО ВАСИЛИЙ ВЯЧЕСЛАВОВИЧ

МПК / Метки

МПК: H03M 13/00

Метки: исправления, ошибок

Опубликовано: 23.12.1992

Код ссылки

<a href="https://patents.su/10-1783622-ustrojjstvo-dlya-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок</a>

Предыдущий патент: Преобразователь кодов

Следующий патент: Кодер

Случайный патент: Устройство для токовой защиты с отстойкой от броска тока намагничивания