Дельта-кодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

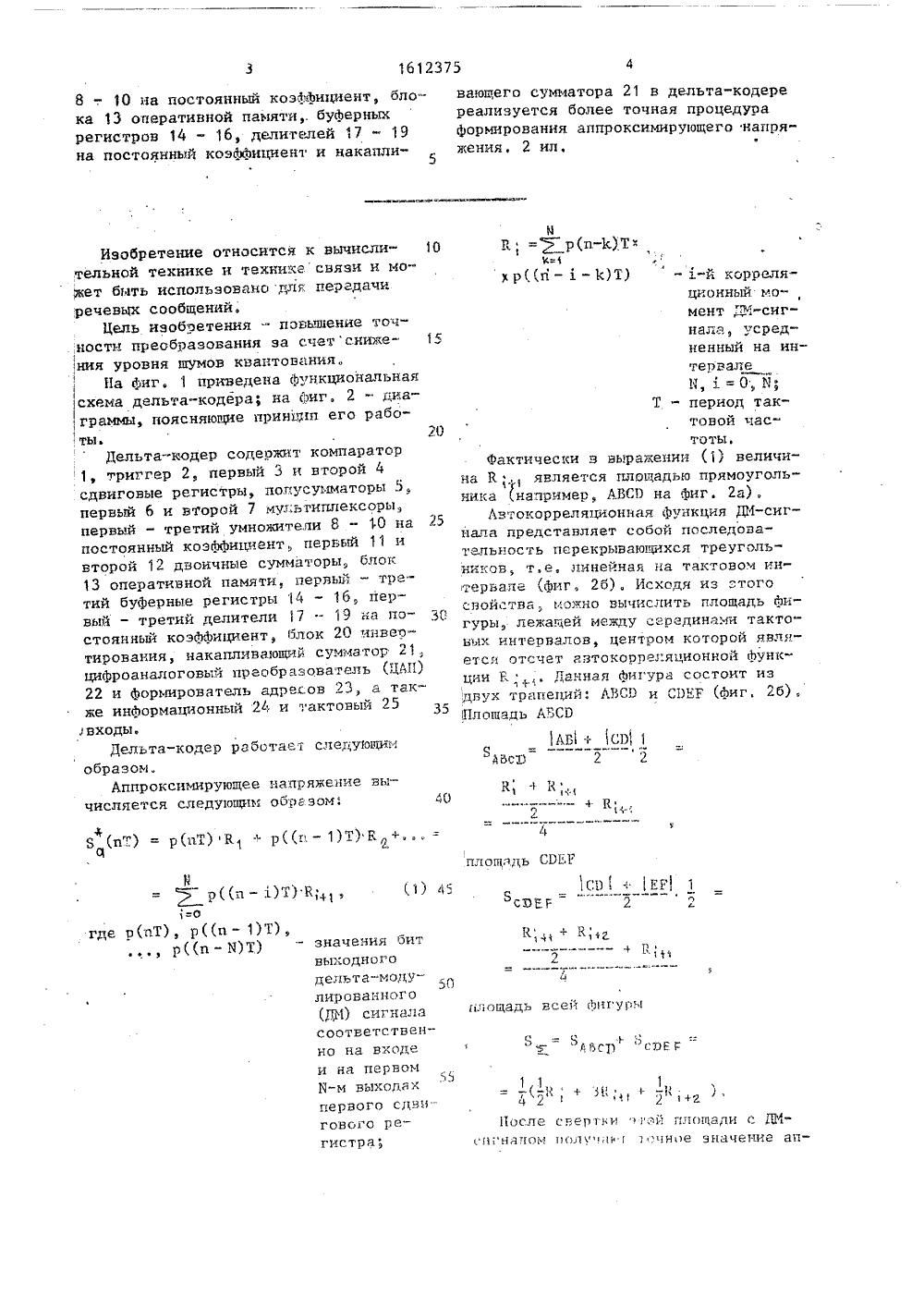

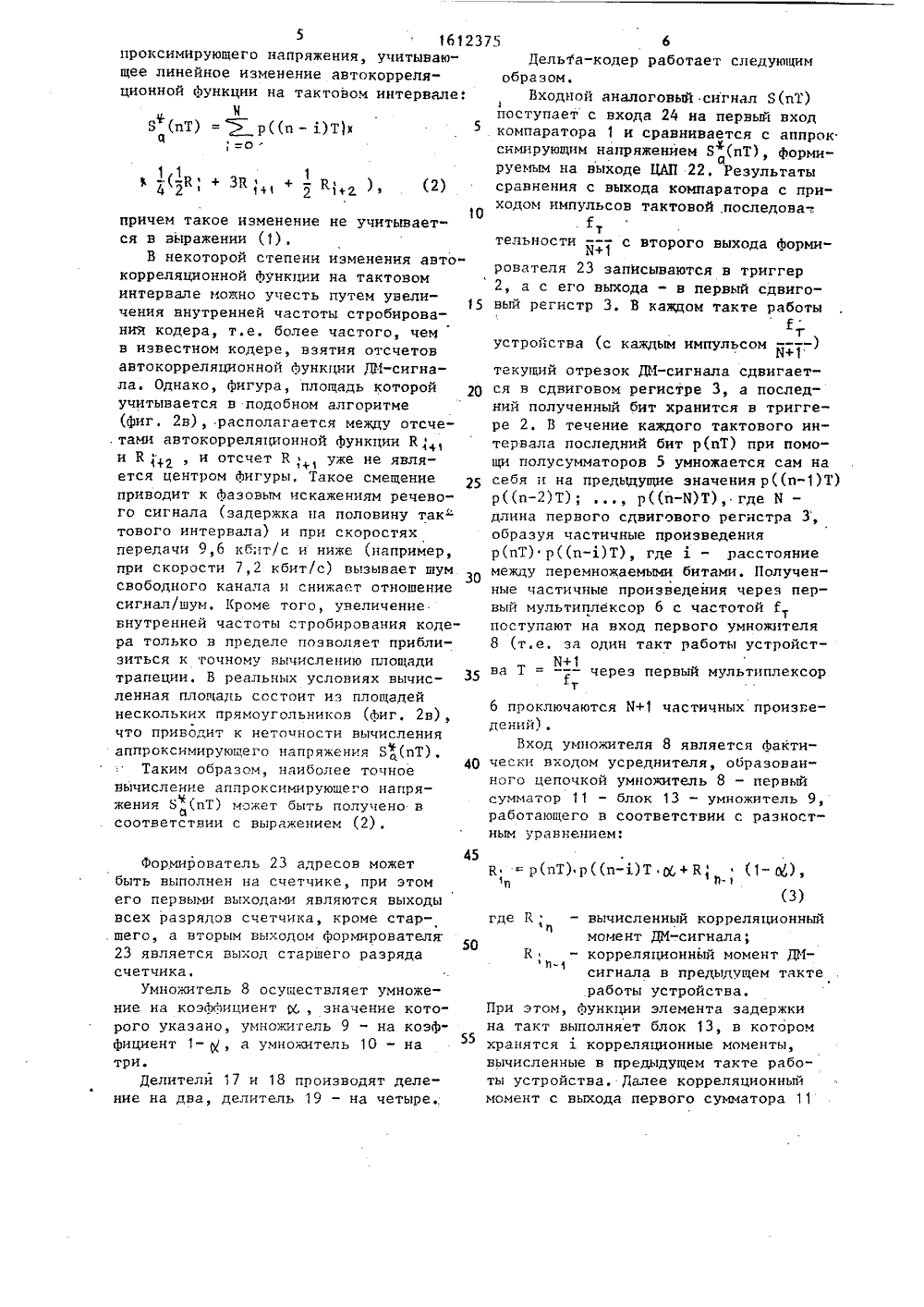

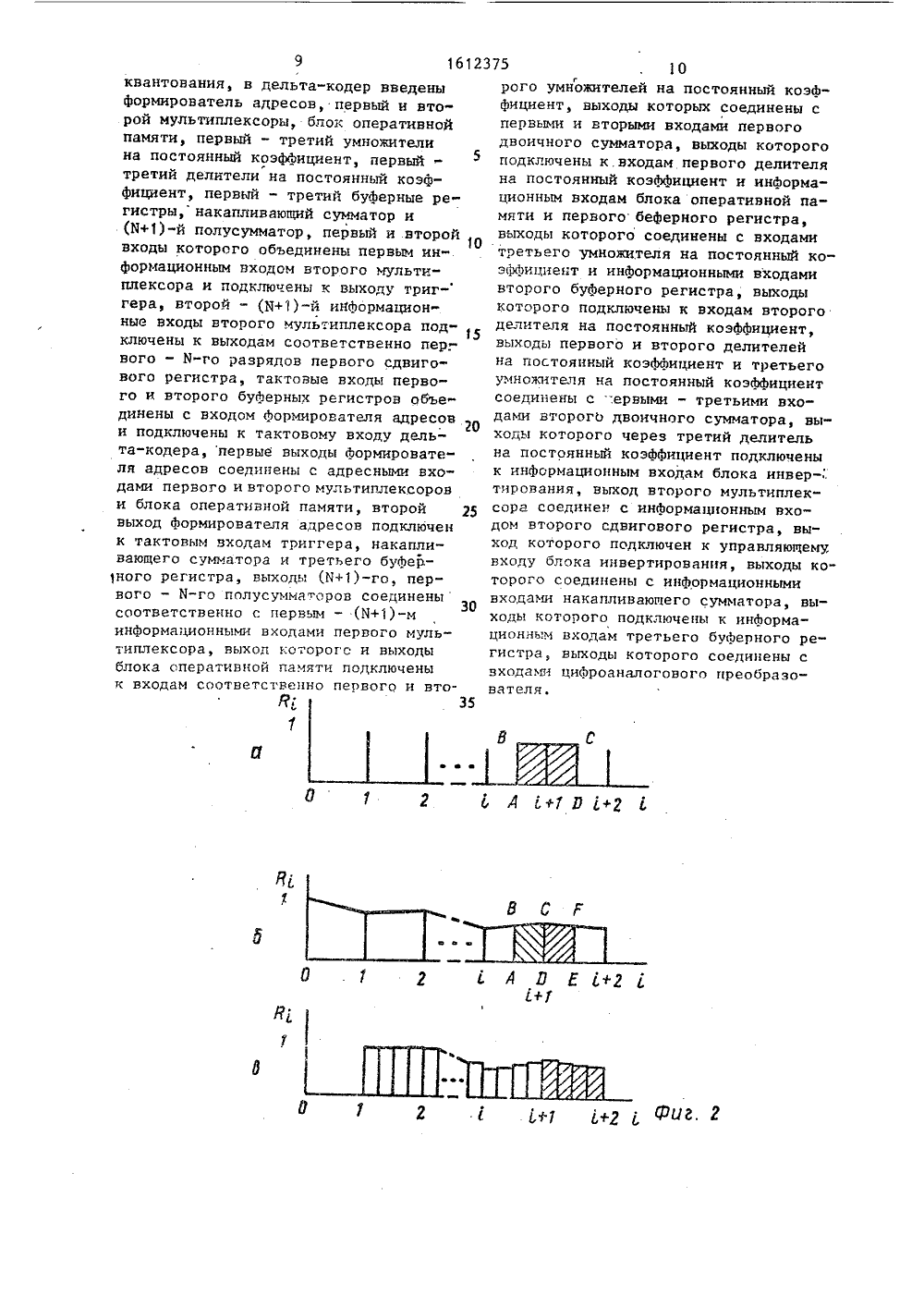

(51)5 Н 03 М О ИЕ ИЗОБРЕТЕНИ АВТОРСН ЕТЕЛЬСТВ(5) ЛЕЛЬТА КО ычислии. Егоевыхочностья уров"одер в е ь иж ьта гер 2,лусуммааторы 11,и цифро 22, Благо 5, (гГ+1),1 гелей т 7 ООУААРстввнньй коцита О ИЗОБРЕТЕНИЯМ И ОЗНРЫТИЯМРи пнт ссо(71) Рижский политехнический институт им. А.Я.Пельше(72) К.С.Комаров, Г.Н.Котович, ИЛ. Малашонок и И.О,Флейшман (53) 621.376,56;681.32 (088,8) (56) Авторское свидетельство СССР. В 1203706, кл, Н 03 М 3/ОО, 1984.Величкин А.И. Гередача аналоговых сообцений по циАровым каналам связи,- М.; Радио и связь, 1983, с, 98Авторское свидетельство СССР гг 1444953, кл . Н 03 г 3/02, 1987.(57) Изобретение относит тельной технике и техник использование для переда сообщений позволяет повы преобразования за счет с ня шумов квантования. Дел содержит компаратор 1, тр сдвиговые регистры 3, 4, торы 5.1-5.гг, двоичные с 12, блок 20 инвертировани аналоговый преобраэовател даря введению полусуммат мультиплексоров 6, 7, умн- ь-Й корреляционный мо" мент "М-сигнала средненный на интервалешБ "=0 Им 9 Т - период тактовой час 1 АБ 1 т 1 ЫЯ4 ьс 2 2 2 К+ Е(1) 45- ;.)Т) ;+1,+г.2 площадь всей фигуры Б.=Б,.ь ъ ср "снеи на первом55Б-м выходахпервого сдвиГОВОГО РЕгис.тра; 1 1, 1,8 в . 10 на постоянный коэфАициент, блока 13 оперативной памяти,. буАерных регистров 14 - 16, делителей 17 - 19 на постоянный коэффициент и накаплиИзобретение относится к вычислительной технике и технике связч и может быть использовано для передачиречевцх сообщений.Цель изобретения - повышение точности преобразования за счетсниже,ния уровня шумов квантования.На фиг. 1 приведена функциональнаясхема дельта-кодера; на фиг, 2 - диаграммы, поясняющие принцип его работы. 20Дельта-кодер содержит компаратор1, триггер 2, первый 3 и второй 4сдвиговые регистры, полусумматоры .),первый 6 и второй 7 му.;ьтиплексорыпервый - третий умножители 8 - 10 на 25постоянный коэАфициент первый 11 ивторой 12 двоичные сумматоры, блок13 оперативной памяти, первый - третий буферные регистры 14 - 16, первый - третий делители 17 - 19 на по(гстоянный коэАфициент, блок 20 инвертирования, накапливающий сумматор 21,цифроаналоговый преобразователь (ЦАП)22 и Аормирователь адрек.ов 23, а также инАормационный 24 и тактовый 25,входы.Дельта-кодер работает следующимобразом,Аппроксимирующее напряжение вычисляется следующим Образом; Ф( ) ( ) р л. рп - 1 Вц 1) Т),(ДИ) сигналасоответственно на входе вающего сумматора 21 в дельта-кодеререализуется более точная процедураформирования аппроксимирующего напряжения, 2 ил,тоты,Фактически в выражении (1) величина В., является площадью прямоугольника ,например, АВСВ на фиг. 2 а).Лэтокорреляционная функция ДМ-сигнала представляет собой последовательность перекрывающихся треуголь"ников, т,е, линейная на тактовом интервале (фиг, 2 б). Исходя из этогосвойства. ыожно вычислить площадь фигуры, лежащей между серединамн тактоьых интервалов центром которой является отсчет автокорреляционной функции Е. , Данная фигура состоит из1+двух трапеций; АНСИ и СБЕГ (Лиг. 2 б),Плошадь АБС 0 СБ 1 + ЕГ 1Бс 2 2 Оспе евер.и ,ой площади с ДМпгналом полу яи 1 .нное эначение ап5 161237 проксимирующего напряжения, учитывающее линейное изменение автокорреляционной функции на тактовом интервале:И8 (пТ) = ;Я рп - з)Т)хЦо р(2) 10 6 проключаются И+1 частичных произгедений) .Вход умножителя 8 является фактически входои усреднителя, образованного цепочкой умножитель 8 - первый сумматор 11 - блок 13 - умножитель 9, работающего в соответствии с разностным уравнением: 1 1, 14 21+ 2 )г причем такое изменение не учитывает"ся в выражении (1),В некоторой степени изменения автокорреляционной функции на тактовоминтервале можно учесть путем увели 15чения внутренней частоты стробирования кодера, т.е. более частого, чемв известном кодере, взятия отсчетовавтокорреляционной функции ДИ-сигнала, Однако, фигура, площадь которой 2 Оучитывается в подобном алгоритме(фиг2 в), располагается между отсче. тами автокорреляционной функции Ки К, и отсчет К; , уже не является центром фигуры. Такое смещениеприводит к фаэовым искажениям речевого сигнала (задержка ца половину так"тового интервала) и при скоростяхпередачи 9,6 кбпт/с и ниже (например,при скорости 7,2 кбит/с) вызывает шумсвободного канала и снижает отношениесигнал/шум. (роме того, увеличениевнутренней частоты стробирования кодера только в пределе позволяет приблизиться к точному вычислению площадитрапеции. В реальных условиях вычисленная площадь состоит из площадейнескольких прямоугольников (фиг. 2 н)что приводит к неточности вычисленияаппроксимирующего напряжения Б (пТ),Таким образом, наиболее точноевычисление аппроксимирующего напряжения Ы (пТ) может быть получено васоответствии с выражением (2). 5 6Дельта-кодер работает следующим образом.Входной аналоговый сигнал Я(пТ) поступает с входа 24 на первый вход компаратора 1 и сравнивается с аппрок сииирующим напряжением Я (пТ), формиФ руеиым на выходе ЦАП 22. Результаты сравнения с выхода компаратора с приходом импульсов тактовой,последова-.ттельностис второго ныхода формиИ+1рователя 23 записываются в триггер 2, а с его выхода - в первый сдвигоный регистр 3. В каждом такте работыг устройства (с кал(дым импульсом ) текущий отрезок ДМ-сигнала сдвигается в сдвигоном регистре 3, а последний полученный бит хранится в триггере 2. В течение каждого тактового интервала последний бит р(пТ) при помощи полусумматоров 5 умножается сам на себя и на предыдущие значения рп)Т) рп)Т); , рп-Я)Т), где И- длина первого сдвигового регистра 3, образуя частичные произведения р(пТ) рп-)Т), где- расстояние между перемножаемыми битами. Полученные частичные произведения через первый мультиплексор 6 с частотой Г, поступают на вход первого умножителя 8 (те. за один такт работы устройстМ+1ва Т = -- через первый мультиплексорт45Формирователь 23 адресов может быть выполнен на счетчике, при этом его первыми выходами являются выходы всех разрядов счетчика, кроме стар.шего, а вторым выходом формирователя 23 является выход старшего разряда счетчика.Умножитель 8 осуществляет умножение на коэффициент (С, значение которого указано, уиножитель 9 - на коэф" фициент 1- , а уиножитель 10 - на55 три.Делителй 17 и 18 производят деление на дна, делитель 19 - на четыре. К р(пТ) рп)Т ф,+ К ф (1- С),иь-(3)где К - вычисленный корреляционныйамомент ДМ-сигнала;К - корреляционный момент ДИсигнала в предыдущем тактеработы устройстна. При этом, функции элемента задержки на такт выполняет блок 13, в котором хранятсякорреляционные моменты, вычисленные в предыдущем такте работы устройства. Далее корреляционный момент с выхода первого сумматора 11поступает на вход первого делителя 17, в это же время на выходах первого 14 и второго 15 буферных регист-. ров присутствуют два предыдущих корреляционных момента, Так, если на выходе первого сумматора 11 присутствует сигнал К ф то на выходе перво.+а го буферного регистра 14 - сигнала на выходе второго буферногорегистра 15 - сигнал К 1.Сигнал с выхода первого буферного регистра 14 черезумножитель 10 поступает на второй вход второго сумматора 12, на первый вход котброго при 15 фтом поступает сигнал с выхода перво"о делителя 17, а на третий вход - игнал с выхода второго буферного реистра 15 (через второй делитель 18), игнал с выхода .второго сумматора 12 .20 после прохождения через делитель 19 1 имеет вид25Эта величина является площадью фигуры, образованчой суммой площадей двух трапеций АВСР и СРЕ 1 (фиг, 2 б), Сигналы рп)Т с входа и выходов первого сдвигового регистра 3 с частотой Г,; проключаются через второй мультиплексор 7 на вход второго сдвигового регистра 4, который осуществляет з адержку сигнала рп-х.)Т на величи 35 ну 2/Г . Таким образом, в тот момент,т когда на входе блока 20 инвертирования присутствует сигнал на его управляющем входе присутствует р п-з.) Т),Для осуществления предсказания в дельта-кодере производится свертка 45 ДИ-сигнала с его автокорреляционной функцией в соответствии с выражением . (2). Поскольку ДИ-сигнап имеет два11 И 1 З Иуровня ( пр едс тавленные как 1 и - 1 " ) то сверткапроизводится путем сумми - 50 р ования накапливающим сумматором 2 1 выборочно пр ои нв ер тир о в ан ных блоком 20 сигналов с выхода делителя 1 9 .П о фр онту частоты стр о бир ов ани я йт -- происходит запись информации, 1 аЙ+1 копленной в накапливак 1 щем сумматоре 21 в третий бу 41 ерный регистр 16, прн этом накапливающий сумматор 21 обнуляется, Вычисленное таким образом значение аппроксимирующего напряжения 511(пТ) восстанавливается при помощи ЦАП 22 и поступает на второй вход компаратора 1,Управление первым 6 и вторым 7 мультиплексорами и блоком 13 оперативной памяти производится с помощью формирователя 23 адресов, работающего в счетном режиме и осуществляющего деление частоты 2 " входа 25 нагЧ+1Коэффициент усреднителя в выраже 1 л нии (3) ) =вгде ь - интерСАл 11 Твал, на котором речевой сигнал можно считать стационарным, т.е. слоговая постоянная времени, выбирается порядка 5 - 10 мс.Таким образом, так как при вычислении аппроксимирующего напряжения Бф(ВТ) учитывается линейное изменениеаавтокорреляцнонной функции на тактовом интервале, при использовании предлагаемого кодера повышается отношениесигнал/шум кодера, а также снижается уровень шумов свободного канала. Кроме того, в предлагаемом кодере отсутствуют аналоговые элементы.Формула изобретенияДельта-кодер, содержапП 1 й компаратор, первый вход которого является информационным Входом дельта-кодера, выход компаратора соединен с информационным входом триггера, выход которого подкпючен к информационному вхо" ду первого сдвигового регистра, первым входам первого - И-го полусумма- торов (11 - число разрядов первого сдвигового регистра) и является выходом дельта-кодера, второй сдвиговый регистр, тактовый вход которого является тактовым входом дельта-кодера, первый и второй двоичные сумматоры, блок инвертирования и цифроаналоговый преобразователь, выход которого соединен с вторым входом компаратора, тактовый вход триггера объединен с тактовым входом первого сдвнгового регистра, Выходь 1 первого - Б-го разрядов которого по 111 ьлючены к вторым входам одноименьп 1 х полусумматоров, о т л и ч а ю ш и й с я тем, что, с целью повышения то 1 п эсти преобразоВания зд счет 1.11 ил(; 1 Ия уровня шумов,+2; (Риг,квантования, в дельта-кодер введены формирователь адресов, первый и второй мультиплексоры, блок оперативной памяти, первый - третий умножители на постоянный коэффициент, первыйР третий делители на постоянный коэФФициент, первый - третий буферные регистры, накапливающий сумматор и (И+1)-й полусумматор, первый и .второй входы которого объединены первым информационным входом второго мультиплексора и подключены к выходу триг- гера, второй - (И+1)-й инАормационные входы второго мультиплексора под" 15 ключены к выходам соответственно пер.- вого - И-го разрядов первого сдвигового регистра, тактовые входы первого и второго буАерных регистров объединены с входом Аормирователя адресов и подключены к тактовому входу дельта-кодера, первые выходы Аормирователя адресов соединены с адресными входами первого и второго мультиплексоров и блока оперативной памяти, второй выход Формирователя адресов подключен к тактовым входам триггера, накапливающего сумматора и третьего буфер 1 ного регистра, выходь, (И+1)-го, первого - М-го полусумматорон соединеныЭО соответственно с первым - (И+1)-м информационны и входами первого мультиплексора, выход ксторогс и выходы блока оперативной памяти подключены к входам соответственно первого и втор г 35 10рого умножителей на постоянный коэффициент, выходы которых соединены спервыми и вторыми входами первогодвоичного сумматора, выходы которогоподключены к.входам первого делителяна постоянный коэффициент и информационным входам блока оперативной памяти и первого беферного регистра,выходы которого соединены с входамитретьего умножителя на постоянный коэффициент и инАормационными входамивторого буАерного регистра, выходыкоторого подключены к входам второгоделителя на постоянный коэффициент,выходы перного и второго делителейна постоянный коэффициент и третьегоумножителя на постоянный коэАФициентсоединены с .-.ервыми - третьими входами второго двоичного сумматора, выходы которого через третий делительна постоянный коэйфициент подключенык информационным входам блока инвер-тирования, выход второго мультиплексора соединен с инАормационным входом второго сдвигового регистра, выход которого подключен к управляющемувходу блока инвертирования, выходы которого соединены с информационнымивходами накапливающего сумматора, выходы которого подключены к информационньм входам третьего буАерного регистра, выходы которого соединены свходая циАроаналогоного преобразователя,

СмотретьЗаявка

4642637, 26.01.1989

РИЖСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. А. Я. ПЕЛЬШЕ

КОМАРОВ КОНСТАНТИН СЕРГЕЕВИЧ, КОТОВИЧ ГЛЕБ НИКОЛАЕВИЧ, МАЛАШОНОК ИГОРЬ МИХАЙЛОВИЧ, ФЛЕЙШМАН ИГОРЬ ОСИПОВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-кодер

Опубликовано: 07.12.1990

Код ссылки

<a href="https://patents.su/5-1612375-delta-koder.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-кодер</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Преобразователь кода

Случайный патент: Гамма-абсорбционный газоанализатор