Система передачи дискретной информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1518886

Авторы: Захарченко, Киреев, Ключинский, Рейнбах

Текст

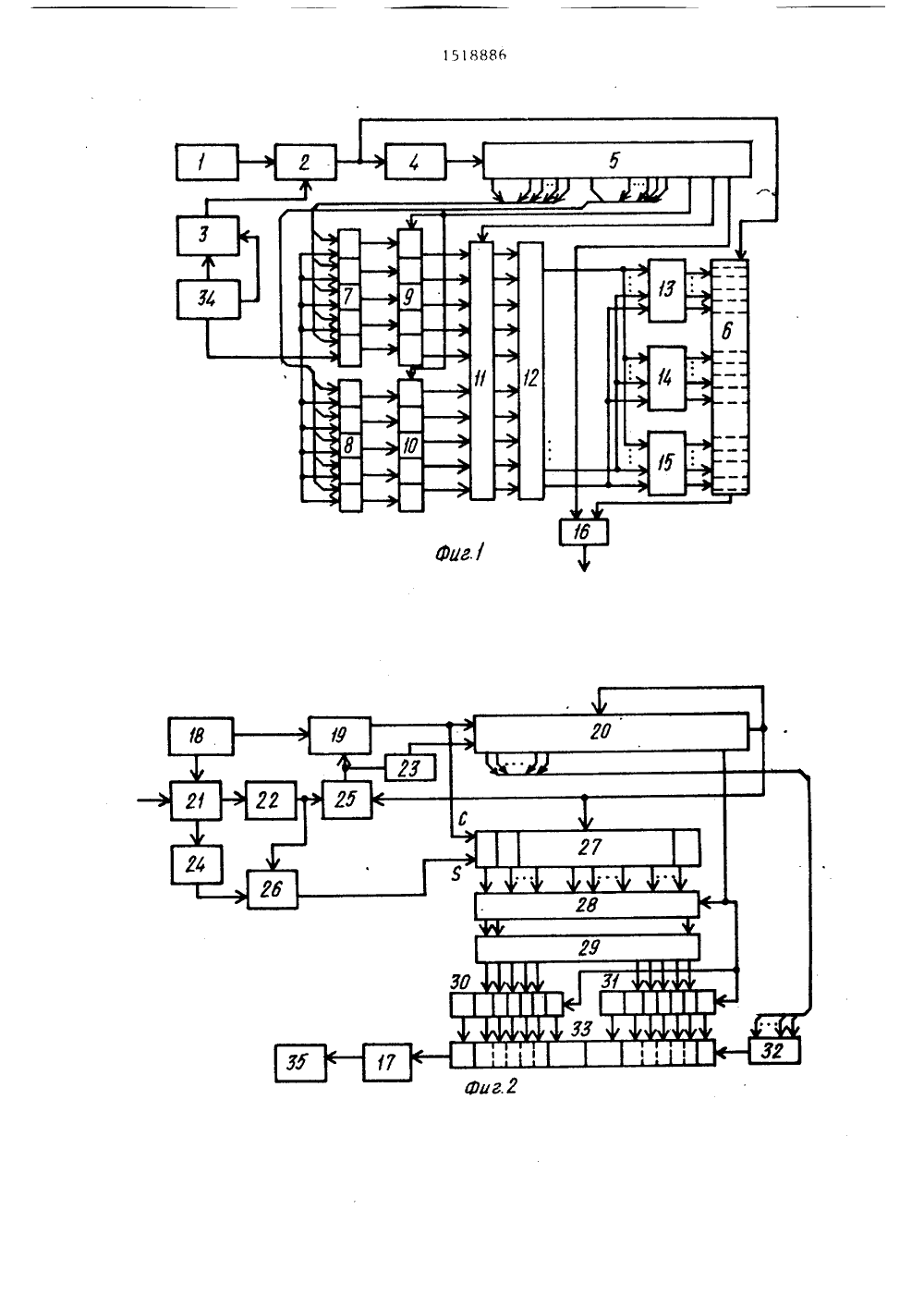

.Киреев,а. -ство ССС 2, 1974. во СССР 12, 1983 СКРЕТНОИ 5 ся к электр повышение ации. Систематороне г-р Изобретение относитс лектро я в систепользов кретной связи же рмаци х передачи связи.бретения является повы э о Цел рати ю и орости передачи и фи 2 представлструктурные эл передающей и приемн нформации.ены соотшение ск ектрическиеой сторон ой информаветствсхемысистем ередачи дискре и,)ации нер -тр ггер 3, делител5 и второй 6 р преобразовател сто ервыи ис г тры сдвига, 7 кода, дополель 8 кода, полнительный рв нительныи -,.реобраэова блок 9 накопителей, д нформац ГОСУДАРСТ 8 ЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР342546/24-0906.10.8730,0.89. Бюл. ф 40Одесский электротехтут связи им. А,С.ПН.В.Захарченко, И,Аючински и П.С.Рей621.394,6(088.8)Авторское свидетель174, кл. Н 04 Е /1 Авторское свидетельстУ 1111258, кл. Н 04 1 1/(54) СИСТЕМА ПЕРЕДАЧИ ДИИНФОРМАЦИИ(57) Изобретение относи)связи. Цель изобретенияскорости передаи информсодержит по передающей с стема передачи дискретнои инфорсодержит на передающей стороне атор 1 импульсов, элемент И 2,импульсов, эл-т И, КБ-триггер, делитель частоты, два регистра сдвига,два преобразователя кода, блок накопителей, блок ключей, два шифратораи счетный триггер, а на приемнойстороне формирователь выходного сигила стартстопных комбинаций, г-р импульсов, эл-т И, три регистра сдвигасчетный триггер, три дифференцирующих блока, КЯ-триггер, два эл-та ИЛИдешифратор и преобразователь кода.Цель достигается введением дополнительно на передающей стороне преобразователя кода, блока накопителейи шифратора, а на приемной сторонедвух блоков накопителей. Даны ил.выполнения передающей и приемной сторон системы. 2 ил блок 1 О накопителей, блок 11 ключей,второй преобразователь 12 кода, первый 3 и второй 14 шифраторы, дополнительный шифратор 15, счетный триггер 6, на приемной стороне - формирователь 17 выходного сигнала стартстоп,ных комбинаций, генератор 18 импульсовэлемент И 19, первый регистр 20 сдвигасчетный триггер 21, первый 22, второй 23 и третий 24 дифференцирующие блоки, ВЯ-триггер 25, первый элемент ИЛИ 26, второй регистр 27 сдвига,дешифратор 28, преобразователь 29кода, первый 30 и второй 31 блокинакопителей, второй элемент ИЛИ 32,третий регистр 33 сдвига,На фиг.и 2также представленыисточник 34 информации и приемник 35Система передачи дискретной информации работает следующим образом,Источник 34 на передающей стороне(фиг.1) определяет начало и конецпередаваемого блока данных. С моментаформирования источником 34 сигналаначало стартстопцой комбинации Формируется сигнал, разрешающий запускВЯ-триггера 3, При этом разрешаетсяпрохождение тактовых импульсов с генераторачерез открытый элемент И 2и делитель 4 на вход первого регистра 5,Частота поступающих импульсов ран1на Г, = , где ь - длительностьТо /2оэлемента простого кода, вырабатываемого источником 34Информация в последовательном виде 20(простой код) вырабатываемая источником 34 с длительностью элементас,о/2, поступает одновременно на первыйпреобразователь 7 и дополнительныйпреобразователь 8. Одновременно с началом работы истцчника 34 первыйрегистр 5 вырабатывает две серииимпульсов, поступающие по тактонымвходам соответственно первого 7 идополнительного 8 преобразователей.Эти импульсы (импульсы регистрации)соответствуют средним частям принимаемых единичных элементов.Цикл работы первого регистра 5соответствует двум стартстопцым цикламвырабатываемым источником 34.С помощью первого 7 и дополнительного 8 преобразователей осуществляется преобразонание элемецтц 1 з пцследцнательцогц простого кода н параллельный, Элементы параллельногц кода соответственно запоминаются н блоке 9накопителей и дополнительном блоке 10накопителей,После приема последнего элемента 45 кода блока информации,соответствующему второму стартстцпцому циклу источника 34, очередным тактовым импульсом первого регистра 5 разрешается работа блока 11 ключей. 1 ри этом информация с блока 9 накопителей и дополнительного блока 1 О накопителей н параллельном виде поступает ца второй преобразователь 12, н котором каждой паре комбинаций прцсгцго пятиэлементцого кода приснагц.антея снцй номер. В результате с помощью второго преобразователя 12 происходит дешифрация накопительных комбин зций н одну нз возможных. С помощью первого 13 и второго 14 шифраторов и дополнительного шифратора 15 производится преобразование номера пары дешифронанных комбинаций кода МТКв одну из комбинаций много- позиционного временного ь, 1, 1 кода (МВК), где , 1, 1 с - переходы, определяющие местоположения значащих моментцн модуляции (ЗК) в формируемом сигнале кодовой комбинации. При этом информация о номере комбинации источника 34, подлежащей передаче, закладывается в сочетании местоположения трех ЗММ сигнала на интервале времени стартстопного цикла. Номера соответствующих смен полярностей (ЗММ)1 с, указь вающиеномера ячеек второго регистра 6, в которые должць. быть записаны единицы, определяются из условияА ь + А 1 + А К = О по шой Ао 1где А , А , А определяются параметрами ошибок в каналесвязи и требуемой верностью передачи.С выхода элемента И 2 тактовые импульсы с частотой следования Г1/а поступают на тактовый вход второго регистра Ь ( Ь - единичный элемент, исцользуемыи при Фцрмирова - ции символов МВК в кодовых словах). Из возможных реализаций выбираются только те, которые удовлетворяют условию (1). При этом информация в виде сочетания переходов последовательно считывается со второго регистра на тактовый вход счетного триггера 16. Началц каждого цикла формируемого сигнала МВК отмечается импульсомпо установочному входу счетного триггера 16, снимаемого с первого регистра 5. В канал связи передаются стартстопцые кодовые комбинации трехэлементцого многопозиционного временного кода с постоянным числом ЗММ 1местоположение которых удовлетворяет условию (1).Информация из канала связи поступает на счетный триггер 21 (фиг,2), в котором осуществляется временная привязка фронтов принимаемых единичных элементов к импульсам генератора 18, работающего с частотой /Ь, С помощью первого 22 и третьего 24 дифференцирующих блоков производится выделение5 15188 фронтон принимаемого сигнала (переходы из 1 н 0 - типа "старт" и переходы из О в . Стартовый переход1 пройдя первый дифференцирующий блок5 22, устанавливает Ю в тригг 25 в единичное состояние, разрешая тем самым прохождение тактоных импульсов с генератора 18 через открытьп элемент .4 19 на гактовый вход первого регист О ра 20. Цикл работы первого регистра 20 выбран р.нным Тп = И Д, где Х количество ячеек первого регистра 20, равное числу возможного местоположения значаыих моментов восстановления 15 (ЗМВ 1 и принимаемой кодовой комбинации МВК, а й - длительность единичного элемента МВК. С помощью второго дифф,.ренцирующего блока 23 ныделяется пе 1.сход (соответствующий старту), записывающий единицу н первую ячейку первого регистра 20.С выхода первого эпемента ИЛИ 26 старговый и 1, 1, 1 с информационные ЭМВ принимаемой кодовой комбинации записываются во втором регистре 27,который вырабатывает зоны регистрации величиной Д с таким расчетом, чтобы принимаемые д, 1, Е переходы находились в средине зоны анализа й , а также осуществ ляет регистрацию каждого д, 1, К ЭМВ кодовой комбинации МВК.Номера этих зон в конце принятой кодовой комбинации МВК н параллельном виде поступают на дешифратор 28, З 5 в котором проверяется условие , Дешифратор 28 преобразует номера1 с ячеек второго регистра 27 в номере групп (пар) кодовых комбинаций простого пятиэлементного кода, 40 На выходе дешифратора 28 появляется сигнал, соответствующий одной иэ возможных (1024) реализаций пар кодовых комбинаций кода МТК, вырабатываемых источником 34. 45Подключение выходов дешифратора 28 к входам преобразователя 29 производится импульсом считывания, снимаемым со второго выхода первого регистра 20 после записи но второй 50 регистр 27 последнего 1-го момента смен полярности (ЭМВ) н принимаемой кодовой комбинации МВК.Ф Выходы преобразонателя 29 подклю 55 чены к соответствующим входампервого 30 и второго 31 блоков накопителей, т.-. произнодится обратное преобразодание (из 1024 в 10). Выходы 86 6первого 30 и второго 3 блоков накопителей подключены к входам ячеектретьего регистра 33, в которьп будетзаписана информационная часть (кодМТК) соответственно для первойи второй стартстопной кодовой комбинации, В ячейках третьего регистра 33записаны зд.ементы и чала ( Сгапт )и конца ( Стоп ) для формированиястартстопных кодовых комбинаций, выдаваемые н последовательном видеПреобразование производится в очередном стартстопном цикле с помощьюуправляющих импульсов, вырабатываемыхпервым регистром 20, которые поступают на третий регистр 33 через нторойэлемент ИЛИ 32. Указанные управляющие импульсы должны соответствоватьзначашим моментам модуляции единичных элементов Т кодовых комбинацийопятиэлементного кода, включая элементы "Старт" и "Стоп",Сигналы комбинаций МТК, записанные н регистре 33, со скоростью модуляции В = /, /2 (соответствующейскорости модуляции на передающей стороне) поступают на вход формирователя 17, с помощью которого формируются параметры выходного сигналастартстопных комбинаций, выдаваемых вприемник 35.В конце стартстопного цикла первыйрегистр 20 вырабатывает импульс,сбрасывающий КБ-триггер 25, первый 20и второй 27 регистры в исходноесостояние.Формула изобретения Система передачи дискретной информации, содержащая на передающей стороне последовательно соединенные КБ-триггер, элемент И, делитель частоты, первый регистр сдвига и счетный триггер, а также генератор импульсов, выход которого подсоединен с второму входу элемента И, первый и второй преобразователи кода, блок накопителей блок ключей, второй регистр сдвига и первый и второй шифраторы, выходы которых подсоединены к соответствующим информационным входам второго регистра сдвига, тактовьп вход и выход которого подключены соответственно к выходу элемента И и тактовому. входу счетного триггера, выходы преобразователя кода через блок накопителей и блок ключей подсоединены к соответствующим входам второго преоб 1518886разонателя кода, причем К-н,сод, 8- вход В 5-триггера, информационныйвход первого преобразователя кода и выход счетного триггера являются соответственно первым и вторым управляющими входами, информационным входом и канальным выходом системы, на приемной стороне - последовательно соединенные счетный триггер, первый дифО ференцируюпгий блок, ВБ-триггер, второй дифференцирующий блок и первый регистрсдвига, последовательно соединенные генератор импульсов и элемент И, выход которого подсоединен к тактовому нходу 5 первого регистра сдвига, последовательно соединенные третий дифференцирующий блок, первый элемент ИЛИ и второй регистр сдвига, тактовый вход которого подключен к выходу элемента И, после довательно соединенные третий регистр сдвига и Формирователь выходного сигнала стгртстопиых комбинаций, а также второй элемент ИЛИ, дешифратор и преобразователь кода, входы которого через25 дешифратор подключены к соотнетству 1 ощим выходам второго регистра сдвига, установочный вход второго регистра сдвига, объединенный с установочным входом первого регистра сдвига и 3 п К-входом В 5-тригг ера, подключен к первому выходу первого регистра сдги га, второй выход которого подсоединен к считывающему,входу дешифрзтора, а инверсный выход сче гиого триггера, выход иерногц дифференцирующегц блок и КБ-триггер иодсцдииены соответственно к входу третьего диффереицирующего блок и вторым входам первого элемента ИЛИ и элемента И, причем 40 Э-вход счетного триггера и выхсд формирователя выходного сигнала стартс тцпных комбинаций лнля 1 отся соответственно канальным входом и выходом системъ 1, о т л и ч а ю щ а я с я тем, что 45 с целью ис.нышеиия с:корцсти передачи информации, на передаюшеи стороне ннедены дополнительные преобразователь кода, блок накопителей и шифратор, при этом иисрормационный вход доицлнительного преобразователя кода подключен к информационному вхцду первого преобразователя кода, тактовые входы первого преобразователя кода и дополнительного преобразователя кода подключены к соответствующим выходам первого регистра сдвига, выходы догнлнительнцго преобразователя кода подсоединены через дополнительный блок накопителей к соответствующим входам блока ключей, дополнительные выходы которого подсо.динены к соцтнетстнующим дополиител нымвходам второго преобразователя коп, выходы которого пцд цединены г соотнетстнующим входам первого, второго и доиопнительиогц шиФраторов, выходы доиолнительис гс 1 шифратора ицдсос.динены к соц гветс н ощим дополнительным входам второго регистра сдвига, а объединенные тактовые входы блока накопителс.й и дополнительного блока накопителей и управляющий вход блока клгочей подключены с.цотнетстненно к первому и второму дополнительным выходам первого р гистра сдвига, на приемной стороне введены первый и второй блоки накопителей, при этом соотдетству ощне выходы преобразователя кода через первый и второй блоки накопителей подсоединены к соответствующим установочным входам третьего регистра сдвига, тактовый вход которого через второй элемент ИЛИ подключен к третьим выходам первого регистра сдвига, тактовые входы первого и второго блоков . накопителей подключены к второму выходу первого регистра сдвига, а дополнительный выход генератора импульсон подсоединен к тактовому входу счетного триггера.

СмотретьЗаявка

4342546, 06.10.1987

ОДЕССКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. А. С. ПОПОВА

ЗАХАРЧЕНКО НИКОЛАЙ ВАСИЛЬЕВИЧ, КИРЕЕВ ИГОРЬ АНАТОЛЬЕВИЧ, КЛЮЧИНСКИЙ ВИКТОР ИППОЛИТОВИЧ, РЕЙНБАХ ПЕТР СЕРГЕЕВИЧ

МПК / Метки

МПК: H03M 13/31

Метки: дискретной, информации, передачи

Опубликовано: 30.10.1989

Код ссылки

<a href="https://patents.su/5-1518886-sistema-peredachi-diskretnojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи дискретной информации</a>

Предыдущий патент: Устройство декодирования псевдослучайных последовательностей

Следующий патент: Способ передачи и приема аналоговых сигналов

Случайный патент: Магнезиально-силикатный огнеупор