Процессор аппроксимационной обработки информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

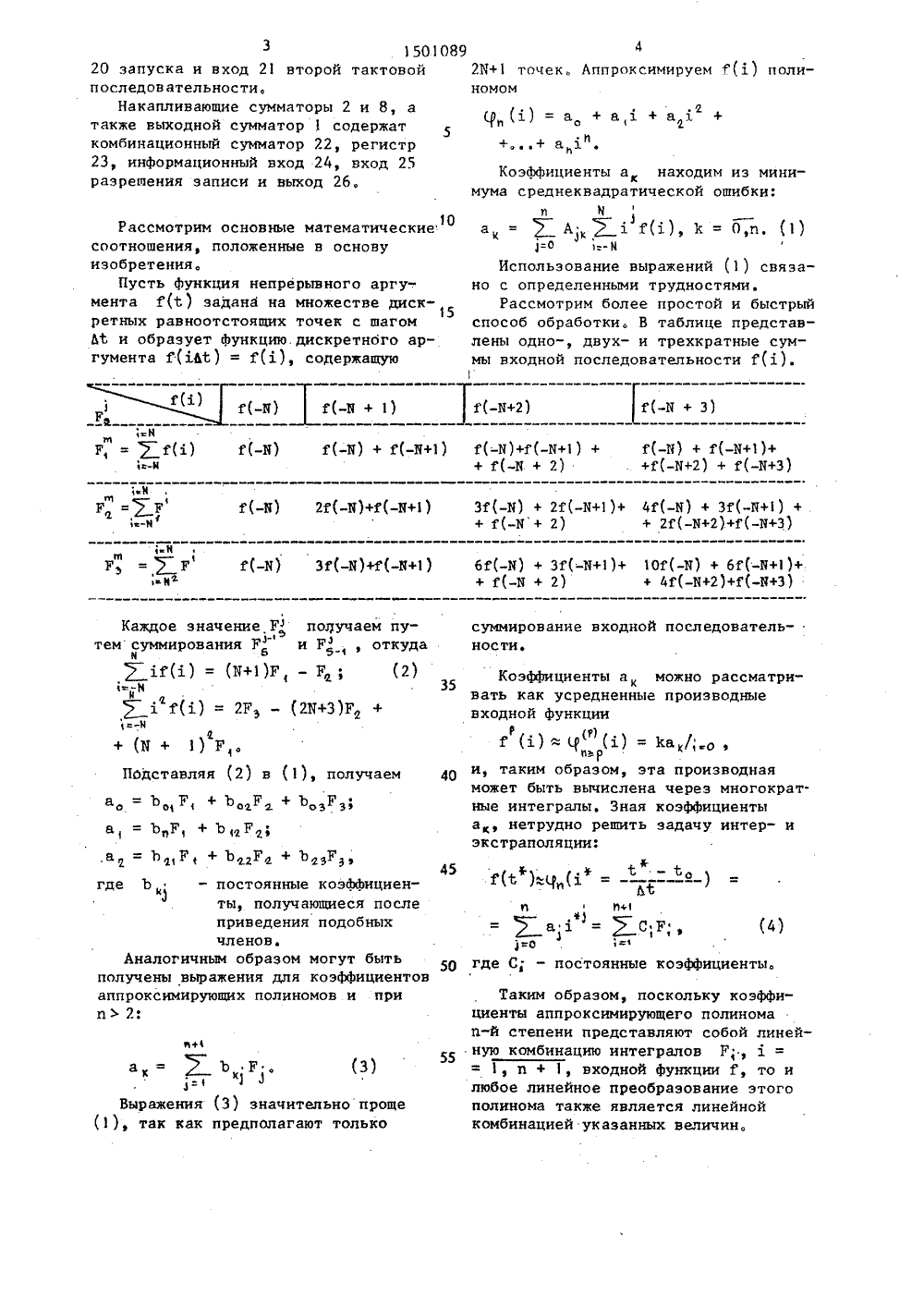

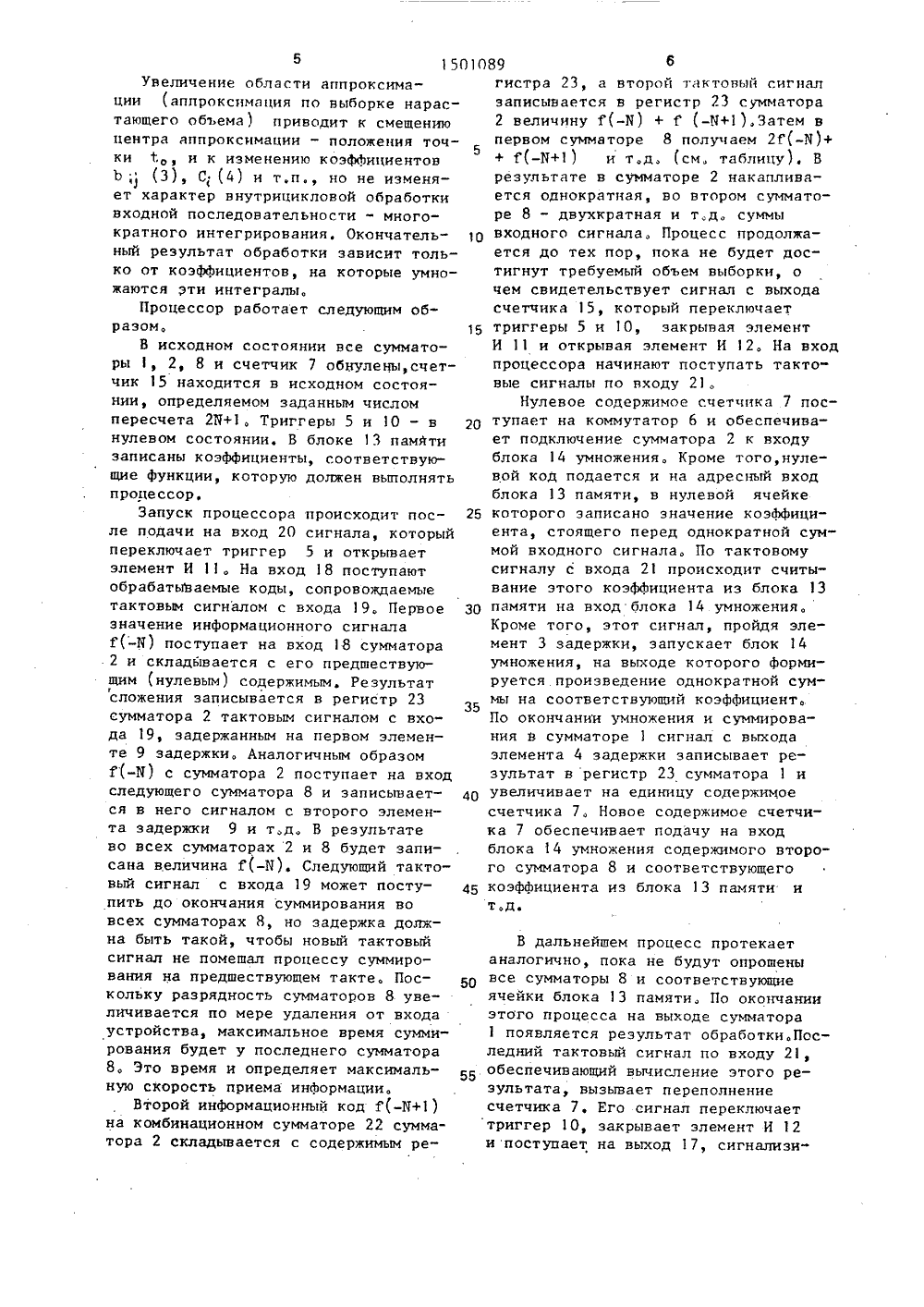

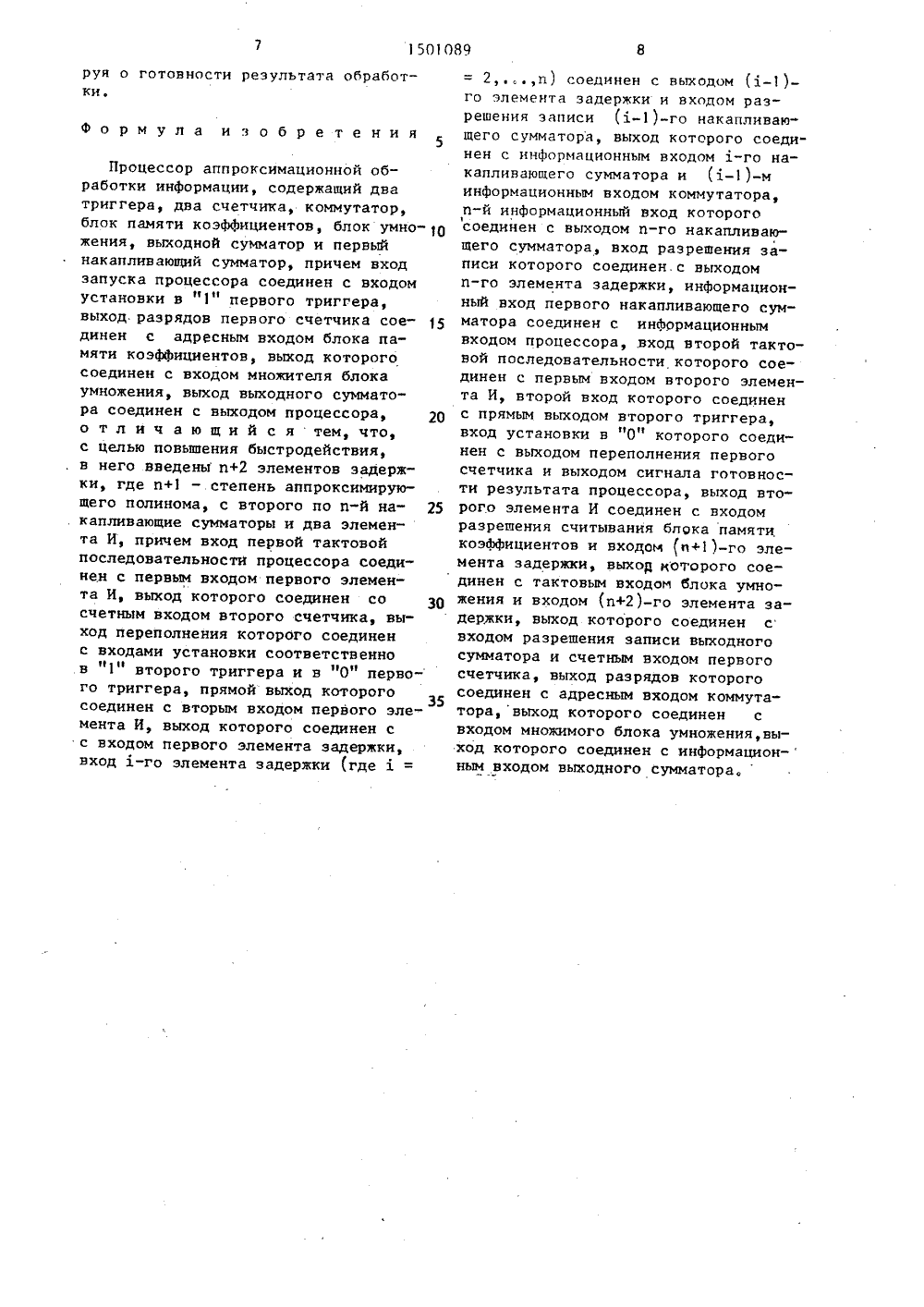

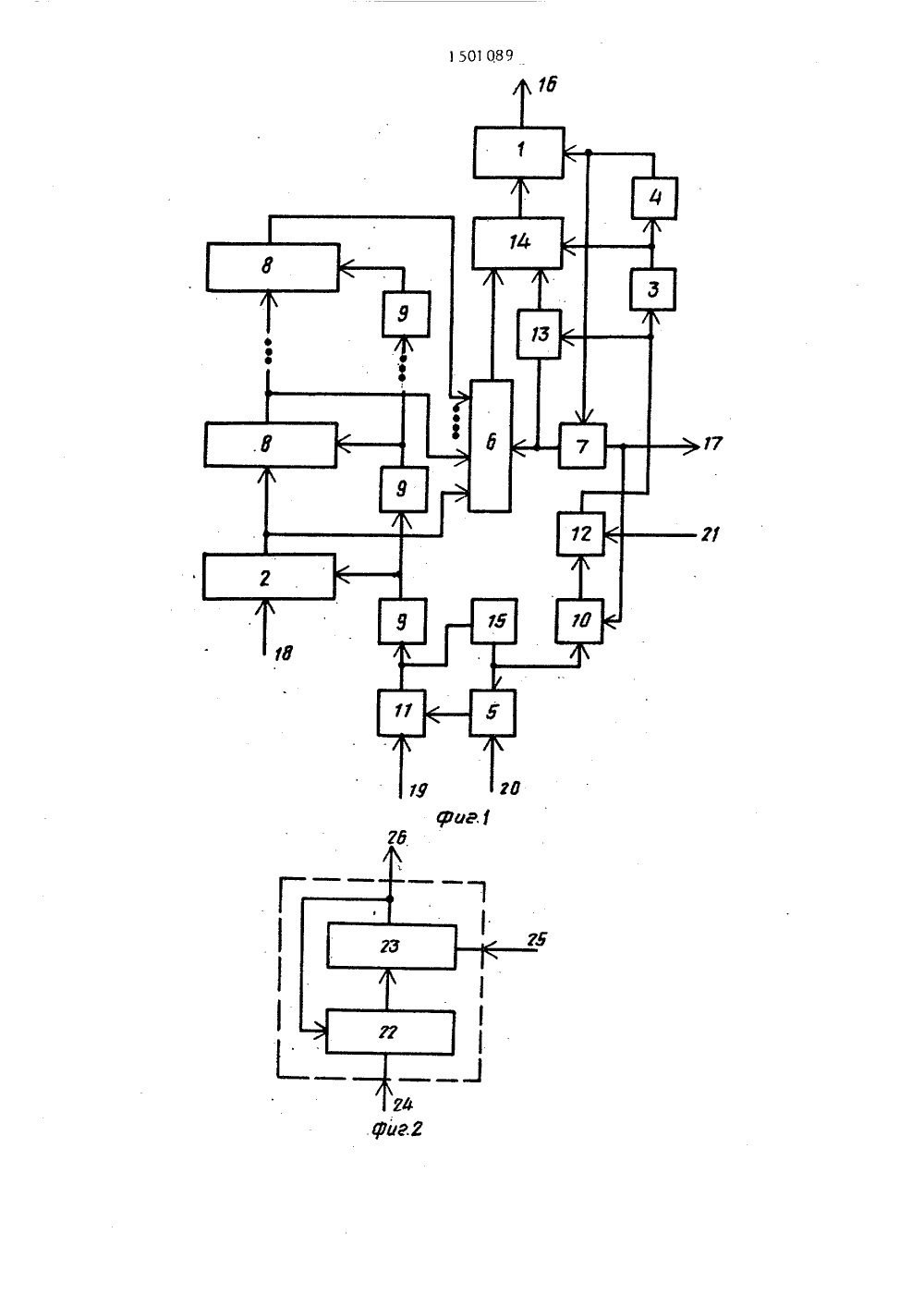

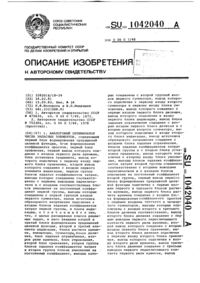

СОЮЗ СОВЕТСКИХСОЦИДЛИСТИЧЕСНИРЕСПУБЛИН 4006 353 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ЗОБРЕТЕНИ ЕЛЬСТВУ(54) ПРОЦЕССОР АППРОКСОБРАБОТКИ ИНФОРМАЦИИ(57) Изобретение относится квой вычислительной технике ибыть использовано для быстрчисления характеристик полинстепени, аппроксимирующих вхсигнал, представленный в виддовательности цифровых кодовизобретения - повьппение быствия. Процессор содержит п+1вающих сумматоров, выходной кий льство СССР15/353, 1985ство СССР15/353, 1984ИМАЦИОННОЙ цифро может омов п-и,однойе послеЦель родеист- накаплиумматор Изобретение относится к вычислительной технике и может быть испольвано для,высокоскоростной обработки входной информации, представленной в цифровом коде.Суть обработки, выполняемой устройством, заключается в аппроксимации входного сигнала, представленного последовательностью цифровых кодов, степенным полиномом, и вычислении коэффициентов этого полинома,усредненных производных интер- иэкстраполяции.Цель изобретения - повьппение быстродействия,эо 8 ТОРСКОМУ СВИ 2блок умножения, блок памяти, два счетчика, коммутатор, элементы задержки и способен принимать входные коды с периодом, равным времени суммирования в накапливающем сумматоре. Принцип работы процессора связан скпереходом от сумм нида , Х Г(х) к суммам вида .ЕГ(х). На первом этапе работы выполняется многократное суммирование входного сигнала. По окончании заданного объема выборки производится расчет конечных результатов обработки путем умножения многократных сумм входных кодов на постоянные коэффициенты. Процессор позволяет определять коэффициенты аппроксимирующего полинома, многократные интегралы и усредненные производные входного сигнала, а также рещать задачи интер- и экстраполяции. 2 ил 1 табл. На фиг.1 представлена блок-схемапроцессора; на фиг.2 - блок-схеманакапливающего сумматора,Процессор содержит выходной сумматор 1, накапливающий сумматор 2,элементы 3 и 4 задержки, триггер 5,коммутатор 6, счетчик 7, накапливающие сумматоры 8, элементы 9 задержки, триггер 1 О, элементы И 11 и12, блок 13 памяти коэффициентов,блок 14 умножениясчетчик 15, инфомационный выход 16 процессора, выхо17 сигнала готовности результата,информационный вход 18, вход 19 первотактовой последовательности, входВ дальнейшем процесс протекаетаналогично, пока не будут опрошенывсе сумматоры 8 и соответствующиеячейки блока 13 памяти, По окончанииэтого процесса на выходе сумматорапоявляется результат обработки.Последний тактовый сигнал по входу 21, 55. обеспечивающий вычисление этого результата, вызывает переполнениесчетчика 7. Его сигнал переключаеттриггер 10, закрывает элемент И 12и поступает на выход 17, сигнализи" 5 15010Увеличение области аппроксимации (аппроксимация по выборке нарастающего объема) приводит к смещению центра аппроксимации - положения точ 5 ки 10, и к изменению коэффициентов Ь, (3), С(4) и т,п но не изменяет характер внутрицикловой обработки входной последовательности - многократного интегрирования. Окончатель ный результат обработки зависит только от коэффициентов, на которые умножаются эти интегралы.Процессор работает следующим образом. 15В исходном состоянии все сумматоры 1, 2, 8 и счетчик 7 обнулены,счетчик 15 находится в исходном состоянии, определяемом заданным числом пересчета 2 Б+1, Триггеры 5 и 10 - в 20 нулевом состоянии. В блоке 13 памяти записаны коэффициенты, соответствующие функции, которую должен выполнять процессор.Запуск процессора происходит пос ле подачи на вход 20 сигнала, который переключает триггер 5 и открывает элемент И 11. На вход 18 поступают обрабатываемые коды, сопровождаемые тактовым сигналом с входа 19. Первое 30 значение информационного сигнала (-Б) поступает на вход 18 сумматора 2 и складывается с его предшествующим (нулевым) содержимым, Результат сложения записывается в регистр 2335 сумматора 2 тактовым сигналом с входа 19, задержанным на первом элементе 9 задержки. Аналогичным образом Г(-И) с сумматора 2 поступает на вход следующего сумматора 8 и записывает ся в него сигналом с второго элемента задержки 9 и т.д. В результате во всех сумматорах 2 и 8 будет записана величина Г(-Б). Следующий тактовый сигнал с входа 19 может посту пить до окончания суммирования во всех сумматорах Я, но задержка должна быть такой, чтобы новый тактовый сигнал не помешал процессу суммирования на предшествующем такте. Поскольку разрядность сумматоров 8 увеличивается по мере удаления от входа устройства, максимальное время суммирования будет у последнего сумматора 8. Это время и определяет максимальную скорость приема информации.Второй информационный код Г(-0+1) на комбинационном сумматоре 22 сумматора 2 складывается с содержимым ре 89 6гистра 23, а второй тактовый сигнал записывается в регистр 23 сумматора 2 величину (-И) + г (-И+1).Затем в первом сумматоре 8 получаем 2 Г(-И)+ + Г(-И+1) и т,д, (см таблицу), В результате в сумматоре 2 накапливается однократная, во втором сумматоре 8 - двухкратная и т,д, суммы входного сигнала. Процесс продолжается до тех пор, пока не будет достигнут требуемый объем выборки, о чем свидетельствует сигнал с выхода счетчика 15, который переключает триггеры 5 и 10, закрывая элемент И 11 и открывая элемент И 12, На вход процессора начинают поступать такто" вые сигналы по входу 21,Нулевое содержимое счетчика 7 поступает на коммутатор 6 и обеспечивает подключение сумматора 2 к входу блока 14 умножения. Кроме того, нулевой код подается и на адресный вход блока 13 памяти, в нулевой ячейке которого записано значение коэффициента, стоящего перед однократной суммой входного сигнала. По тактовому сигналу с входа 21 происходит считывание этого коэффициента из блока 13 памяти на вход блока 14 умножения. Кроме того, этот сигнал, пройдя элемент 3 задержки, запускает блок 14 умножения, на выходе которого формируется произведение однократной суммы на соответствующий коэффициент. По окончании умножения и суммирования в сумматоре 1 сигнал с выхода элемента 4 задержки записывает результат в регистр 23 сумматора 1 и увеличивает на единицу содержимое счетчика 7. Новое содержимое счетчика 7 обеспечивает подачу на вход блока 14 умножения содержимого второго сумматора 8 и соответствующего коэффициента из блока 13 памяти и т,д.руя о готовности результата обработки.Формула изобретенияПроцессор аппроксимационной обработки информации, содержащий два триггера, два счетчика, коммутатор, блок памяти коэффициентов, блок умно О жения, выходной сумматор и первый накапливающий сумматор, причем вход запуска процессора соединен с входом установки в "1" первого триггера, выход разрядов первого счетчика сое динен с адресным входом блока памяти коэффициентов, выход которого соединен с входом множителя блока умножения, выход выходного сумматора соединен с выходом процессора, 2 О о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия, в него введены п+2 элементов задержки, где и+1 - степень аппроксимирующего полинома, с второго по п-й на . капливающие сумматоры и два элемента И, причем вход первой тактовой последовательности процессора соединен с первым входом первого элемента И, выход которого соединен со 30 счетным входом второго счетчика, выход переполнения которого соединен с входами установки соответственно в "1" второго триггера и в "О" первого триггера, прямой выход котоРого соединен с вторым входом первого элемента И, выход которого соединен сс входом первого элемента задержки,вход -го элемента задержки 1 где- 2,и) соединен с выходом (1-1) -го элемента задержки и входом разрешения записи (1-1)-го накапливающего сумматора, выход которого соединен с информационным входом -го накапливающего сумматора и (-1)-минформационным входом коммутатора,и-й информационный вход которого3соединен с выходом л-го накапливающего сумматора, вход разрешения записи которого соединен.с выходомп-го элемента задержки, информационный вход первого накапливающего сумматора соединен с инфОрмационнымвходом процессора, .вход второй тактовой последовательности которого соединен с первым входом второго элемента И, второй вход которого соединенс прямым выходом второго триггера,вход установки в "О" которого соединен с выходом переполнения первогосчетчика и выходом сигнала готовности результата процессора, выход второго элемента И соединен с входомразрешения считывания блрка памятИкоэффициентов и входом оп+1)-го элемента задержки, выход которого соединен с тактовым входом блока умножения и входом (и+2)-го элемента задержки, выход которого соединен свходом разрешения записи выходногосумматора и счетным входом первогосчетчика, выход разрядов которогосоединен с адресным входом коммутатора,выход которого соединен свходом множимого блока умножения,выход которого соединен с информацион-ным входом выходного сумматора, 1 501 089

СмотретьЗаявка

4376894, 09.02.1988

ВОЕННЫЙ ИНЖЕНЕРНЫЙ КРАСНОЗНАМЕННЫЙ ИНСТИТУТ ИМ. А. Ф. МОЖАЙСКОГО

ВЕРЕВКИН АЛЕКСАНДР ЮРЬЕВИЧ, ДОРСКИЙ ЮРИЙ ДМИТРИЕВИЧ

МПК / Метки

МПК: G06F 15/00, G06F 17/17

Метки: аппроксимационной, информации, процессор

Опубликовано: 15.08.1989

Код ссылки

<a href="https://patents.su/5-1501089-processor-approksimacionnojj-obrabotki-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Процессор аппроксимационной обработки информации</a>

Предыдущий патент: Цифровой фильтр

Следующий патент: Устройство для входного контроля

Случайный патент: 453656