Формирователь многочастотного сигнала

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1406708

Авторы: Доворецкий, Карпов

Текст

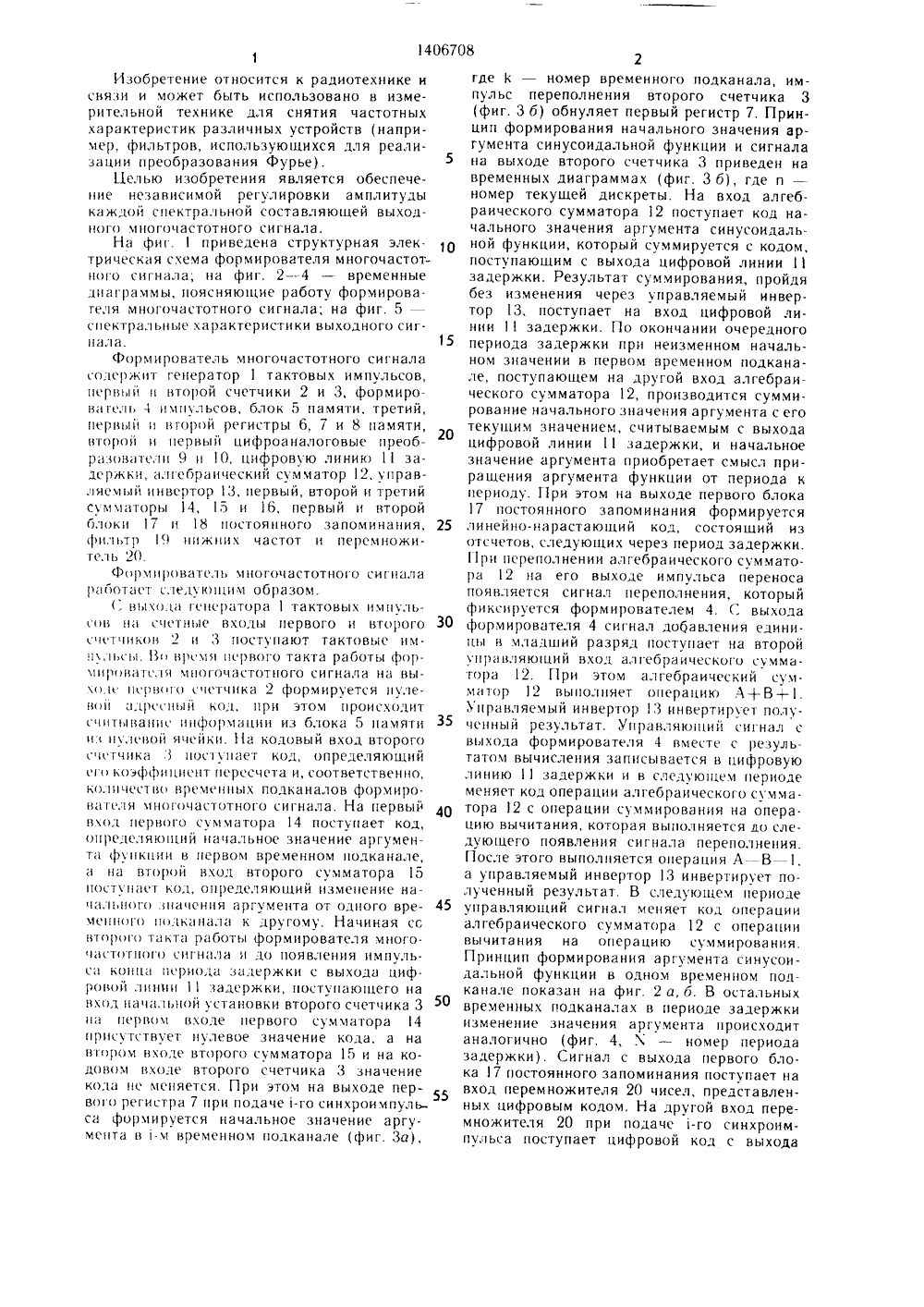

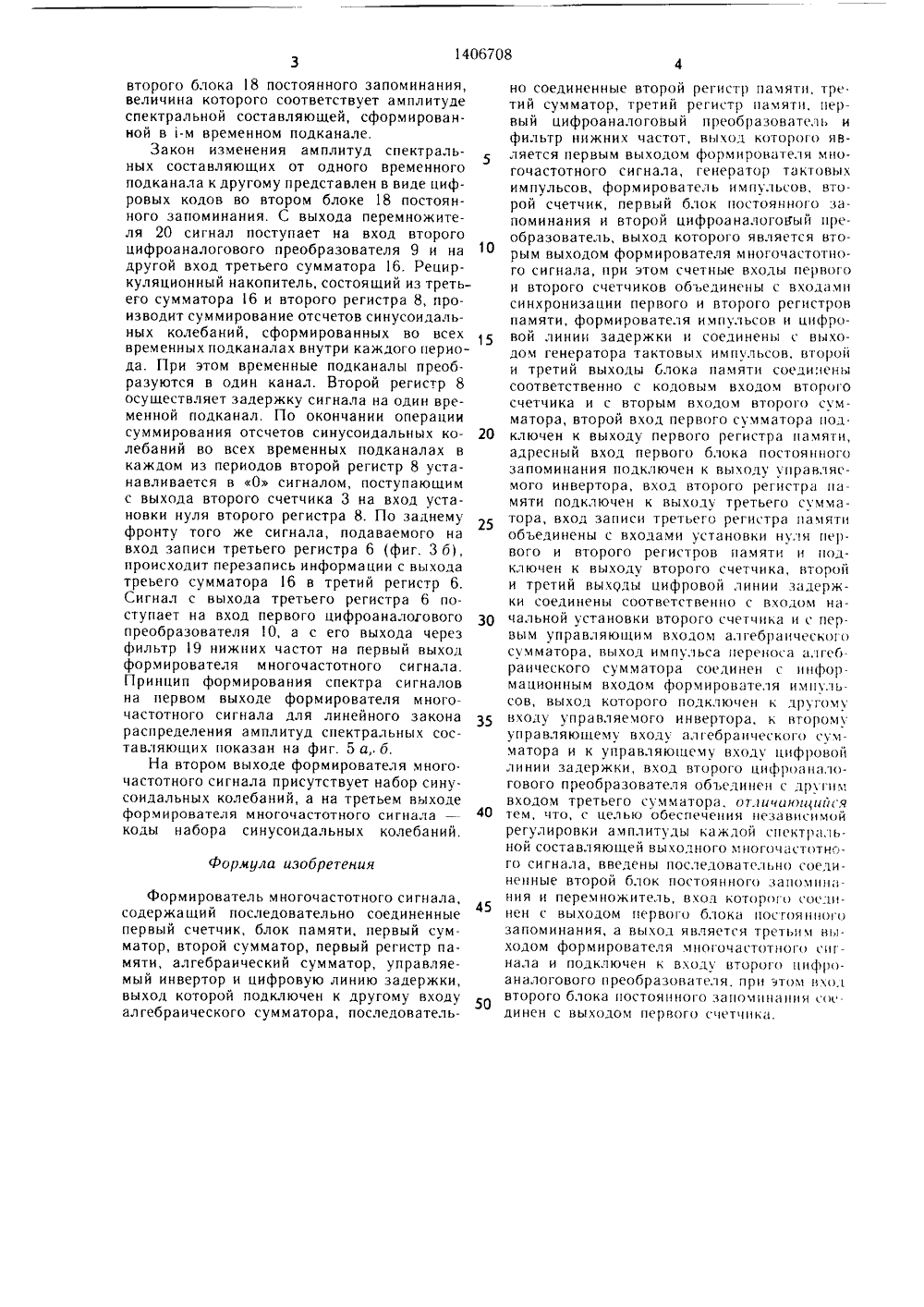

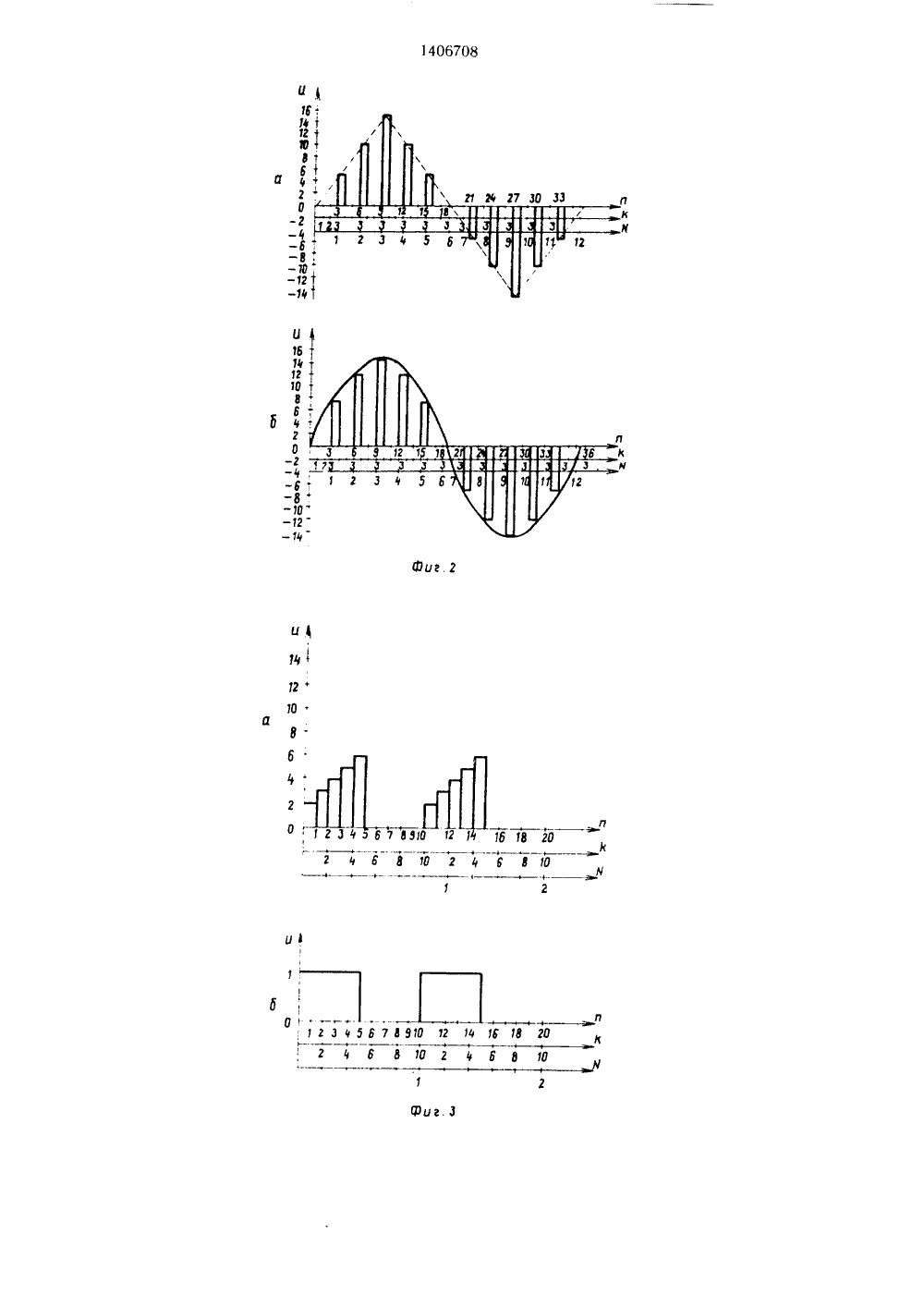

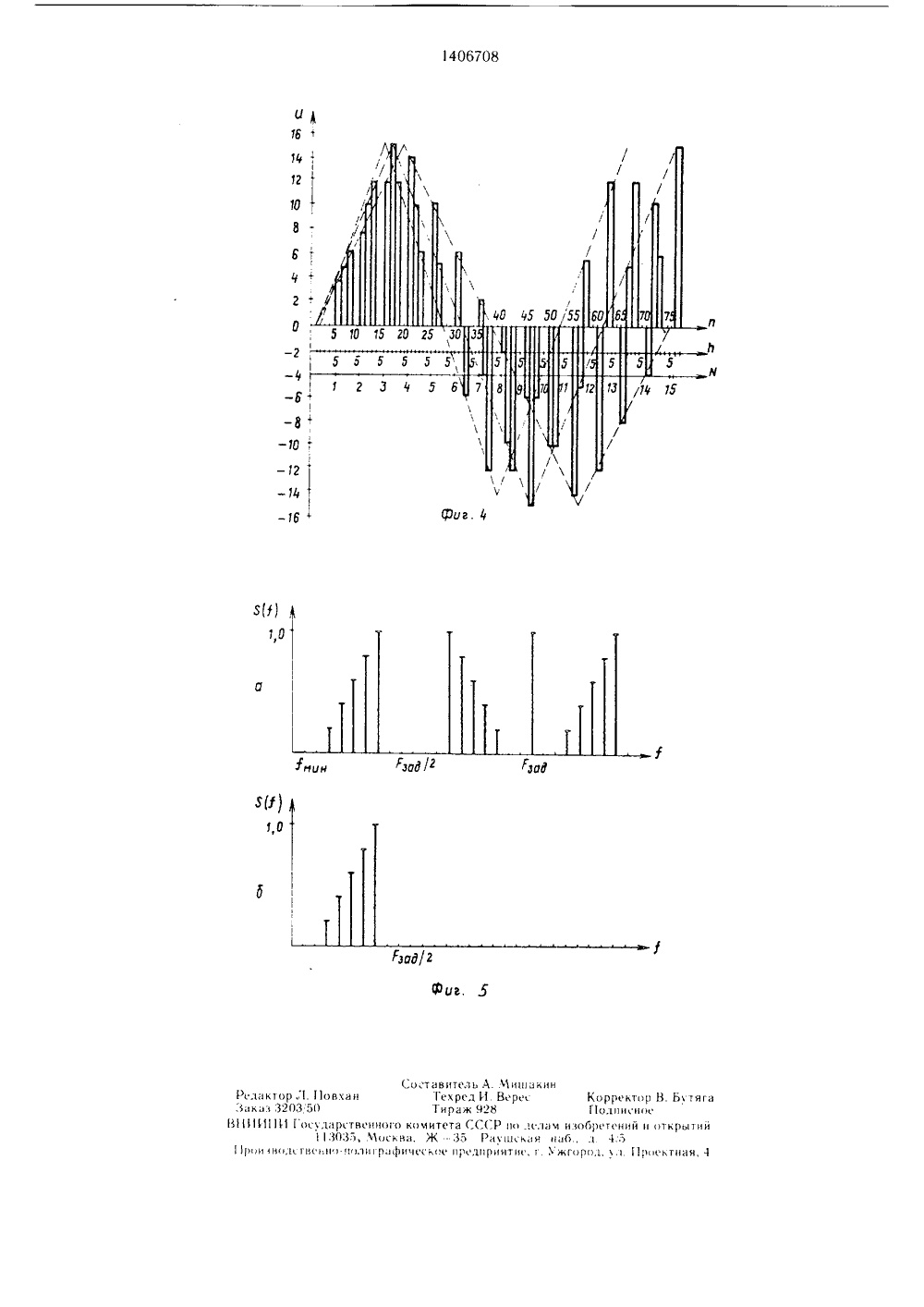

/00, 06.12.85.МНОГОЧАСТО я к ооласти радиочьзовано в измери. частотных х-к разретения - обесперовки а м нл итхды ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ ОПИСАНИЕ ИК АВТОРСКОМУ СВИ(57) Изобретение относитетехники и связи и м,б. испотельной технике для снятияличных устр-в. Цель изобчение независимой регули,ЯО 14067 каждой снектральной состдвляюгцей вь)ход ного многочастотного сигнала (ЧЧС) Формирователь МЧС содержит генератор тактовых импульсов 1, счетчики 2, 3, формирова. тель 4 импхльсов, блок памяти 5, регистры 6, 7, 8 памяти, ЦАГ 9, 10, цифровхю линию .адержки 11, длгебрдический сумматор 12, управляемый инверчор 13, сумматоры 14, 15, 16, блок постоянного здпоминания 17, фильтр нижни частот 19. 1 оставленная цель достигдтся введением в 1 тр-во второго б.чокд постоянного здноминдния 18 и перемножителя 20. Закон изменения дмилитуд спек тральных составляюгцих от одного врсмнного подканалд к дрх гомх представлен в вид гдблицы цифровых кдов в олокс отон- е ш ного заноминдния8. 5 и.ч.Изобретение относится к радиотехнике и связи и может быть использовано в измерительной технике для снятия частотных характеристик различных устройств (например, фильтров, использующихся для реализации преобразования Фурье).Целью изобретения является обеспечение независимой регулировки амплитуды каждой спектральной составляющей выходного многочастотного сигнала.На фиг 1 приведена структурная элек.трическдя схема формирователя многочастотного сигнала; на фиг. 2 - 4 - временные диаграммы, поясняющие работу формирователя многочастотного сигнала; на фиг. 5 спектральные характеристики выходного сигнала.15Формирователь многочастотного сигнала олржит генератор 1 тактовых импульсов, првый н второй счетчики 2 и 3, формировдгль 4 ихильсов, блок 5 памяти, третий, первый и вгорой регистры 6, 7 и 8 памяти, второй и первый цифроаналоговые преобрдзовдтли ) и 10, цифровую линию 11 задржки, алгебраический сумматор 12, управляемый инвертор 13, первый, второй и третий су ммдторь 14, 15 и 16, первый и второй блоки 17 и 18 постоянного запоминания, 25 1 литр 1 нижних частот и перемножи.тель 20.Формирователь многочастотного сигнала рдботгцт следукгцим образом.С выхода гнрдтора 1 тактовых импульн пд счетные входы первого и второго 30 и чиков " и 3 поступают тактовые иму,ьы. В нрмя првого такта работы форм 11 овдля могочдтотного сигнала нд выхо.и првого чтчика 2 формируется пулени дарпый код, при этом проиходгг чтьваниинформации из блока 5 памяти З 5 из пу,ивой ячейки. На кодовый вход второго .гчика 1 олудет код, определявшийо коэффцинт пересчета и, соответственно, количл во временных подканалов формиро.нгля многочастотного сигнала. На первый 40 вход первого сумматора 14 поступает код, определяющий начальное значение аргументд функции в нервом временном подканале, д нд второй вход второго сумматора 15 пступа код, определяющий изменение наядыоо начения аргумента от одного вре чпого лкдндлд к другому. Начиная сс второго такта работы формирователя многочдттпого игндлд и до появления импульд концд приодд задержки с выхода цифровой линии 11 задержки, поступающего на вход ндчдльшй установки второго счетчика 3 пд первом входе первого сумматора 14 ирису ттвует нулевое значение кода, а на втором входе второго сумматора 15 и на кодовом входе второго счетчика 3 значение кола и меняется. При этом на выходе первого регистра 7 при подаче -го синхроимпуль са формируется начальное значение аргумента в -м временном подканале (фиг. За),1406708где К - номер временного подканала, импульс переполнения второго счетчика 3 (фиг. 3 б) обнуляет первый регистр 7, Принцип формирования начального значения аргумента синусоидальной функции и сигнала на выходе второго счетчика 3 приведен на временных диаграммах (фиг. 3 б), где и - номер текущей дискреты. На вход алгебраического сумматора 12 поступает код начального значения аргумента синусоидальной функции, который суммируется с кодом, поступающим с выхода цифровой линии 11 задержки. Результат суммирования, пройдя без изменения через управляемый инвертор 13, поступает на вход цифровой линии 11 задержки. По окончании очередного периода задержки при неизменном начальном значении в первом временном подканале, поступающем на другой вход алгебраического сумматора 12, производится суммирование начального значения аргумента с его текущим значением, считываемым с выхода цифровой линии 11 задержки, и начальное значение аргумента приобретает смысл приращения аргумента функции от периода к периоду. Гри этом на выходе первого блока 17 постоянного запоминания формируется линейно-нарастающий код, состоящий из отсчетов, следующих через период задержки.При переполнении алгебраического сумматора 12 на его выходе импульса переноса появляется сигнал переполнения, который фиксируется формирователем 4, С выхода формирователя 4 сигнал добавления единицы в младший разряд поступает на второй урвляюций вход алгебраического сумматора 12. При этом алгебраический сумматор 12 выполняет операцию А+ В+1, Управляемый инвертор 13 инвертирует полу- ценный результат. Управляюций сигнал с выхода формирователя 4 вместе с результатом вычисления записьвдется в цифровую линию 11 задержки и в следуюп 1 м периоде меняет код операции алгебраического сумматора 12 с операции суммирования на операцию вычитания, которая выполняется до следующего появления сигнала переполнения.После этого выполняется операция Л- - В 1, а управляемый инвертор 13 инвертирует по.лученный результат. В следующем периоде управляющий сигнал меняет код операции алгебраического сумматора 12 с операциивычитания на операцию суммирования.Принцип формирования аргумента синусоидальной функции в одном временном подканале показан на фиг. 2 а, б. В остальных временных подканалах в периоде задержки изменение значения аргумента происходит аналогично (фиг. 4, Х - номер периода задержки). Сигнал с выхода первого блока 17 постоянного запоминания поступает на вход перемножителя 20 чисел, представленных цифровым кодом. На другой вход пере- множителя 20 при подаче 1-го синхроимпульса поступает цифровой код с выходавторого блока 18 постоянного запоминания, величина которого соответствует амплитуде формула изобретеная Формирователь многочастотного сигнала, содержащий последовательно соединенные первый счетчик, блок памяти, первый сумматор, второй сумматор, первый регистр памяти, алгебраический сумматор, управляемый инвертор и цифровую линию задержки, выход которой подключен к другому входу алгебраического сумматора, последователь 45 50 спектральной составляющей, сформированной в 1-м временном подканале.Закон изменения амплитуд спектральных составляющих от одного временного подканала к другому представлен в виде цифровых кодов во втором блоке 18 постоянного запоминания. С выхода перемножителя 20 сигнал поступает на вход второго цифроаналогового преобразователя 9 и на О другой вход третьего сумматора 16. Рециркуляционный накопитель, состоящий из третьего сумматора 6 и второго регистра 8, производит суммирование отсчетов синусоидальных колебаний, сформированных во всех временных подканалах внутри каждого периода. При этом временные подканалы преобразуются в один канал. Второй регистр 8 осуществляет задержку сигнала на один временной подканал. По окончании операции суммирования отсчетов синусоидальных ко лебаний во всех временных подканалах в каждом из периодов второй регистр 8 устанавливается в 0 сигналом, поступающим с выхода второго счетчика 3 на вход установки нуля второго регистра 8. По заднему фронту того же сигнала, подаваемого на вход записи третьего регистра 6 (фиг. 3 б), происходит перезапись информации с выхода треьего сумматора 16 в третий регистр 6. Сигнал с выхода третьего регистра 6 поступает на вход первого цифроаналогового преобразователя 10, а с его выхода через фильтр 19 нижних частот на первый выход формирователя многочастотного сигнала. Принцип формирования спектра сигналов на первом выходе формирователя многочастотного сигнала для линейного закона распределения амплитуд спектральных составляющих показан на фиг. 5 а б.На втором выходе формирователя много.частотного сигнала присутствует набор синусоидальных колебаний, а на третьем выходе формирователя многочастотного сигнала - 40 коды набора синусоидальных колебаний. но соединенные второй регистр памяти, тре. тий сумматор, третий регистр памяти, первый цифроаналоговый преобразователь и фильтр нижних цастот, выход которого является первым выходом формирователя многочастотного сигнала, генератор тактовых импульсов, формирователь импульсов, второй счетчик, первый блок постоянного запоминания и второй цифроаналоговый преобразователь, выход которого является вторым выходом формирователя многоцастотно. го сигнала, при этом счетные входы первого и второго счетчиков объединены с входами синхронизации первого и второго регистров памяти, формирователя импульсов и цифровой линии задержки и соединены с выходом генератора тактовых импульсов, второй и третий выходы блока памяти соединены соответственно с кодовым входом второго счетцика и с вторым входом второго сумматора, второй вход первого сумматора подключен к выходу первого регистра памяти, адресный вход первого блока постоянного запоминания подключен к выходу управляемого инвертора, вход второго регистра памяти подключен к выходу третьего сумматора, вход записи третьего регистра памяти объединены с входами установки нуля первого и второго регистров памяти и подключен к выходу второго счетчика, второй и третий выходы цифровой линии задержки соединены соответственно с входом начальной установки второго счетчика и с пер. вым управляющим входом алгебраического сумматора, выход импульса переноса алгеб. раического сумматора соединен с информационным входом формирователя импульсов, выход которого подключен к другому входу управляемого инвертора, к второму управляющему входу алгебраического сумматора и к управляющему входу цифровой линии задержки, вход второго цифроаналогового преобразователя объединен с другим входом третьего сумматора, от.шчаншшгя тем, что, с целью обеспечения независимой регулировки амплитуды каждой спектральной составляющей выходного многочастотного сигнала, введены последовательно соединенные второй блок постоянного запоминания и перемножитель, вход которого соединен с выходом первого блока постоянноп запоминания, а выход является третьим выходом формирователя многочастотного сигнала и подключен к входу второго цифроаналогового преобразователя, при этом вход второго блока постоянного запоминания со- динен с выходом первого счетчика.)10 а а и 6 х) эа ннакнн Соетавитель А ан Техреду И В Тираж (8 етвенного кчитета Г.О.Р 35, осква, Ж - 35 Рау ноли гра(иче ко прелнри(ри нл гве нктор В. Братягансй и открьтийГ 1 релтнаи, 4 Корре Гоан но .ела ч изоарстен нскдн наа, 1 4 5 тие. г Ужгород, 1,

СмотретьЗаявка

4179561, 12.01.1987

ДАУГАВПИЛССКОЕ ВЫСШЕЕ ВОЕННОЕ АВИАЦИОННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ ИМ. ЯНА ФАБРИЦИУСА

КАРПОВ СЕРГЕЙ ПЕТРОВИЧ, ДОВОРЕЦКИЙ ЮРИЙ БОРИСОВИЧ

МПК / Метки

МПК: H03B 19/00

Метки: многочастотного, сигнала, формирователь

Опубликовано: 30.06.1988

Код ссылки

<a href="https://patents.su/5-1406708-formirovatel-mnogochastotnogo-signala.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь многочастотного сигнала</a>

Предыдущий патент: Формирователь радиоимпульсов

Следующий патент: Утроитель частоты

Случайный патент: Внутренний центратор