Формирователь многочастотного сигнала

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

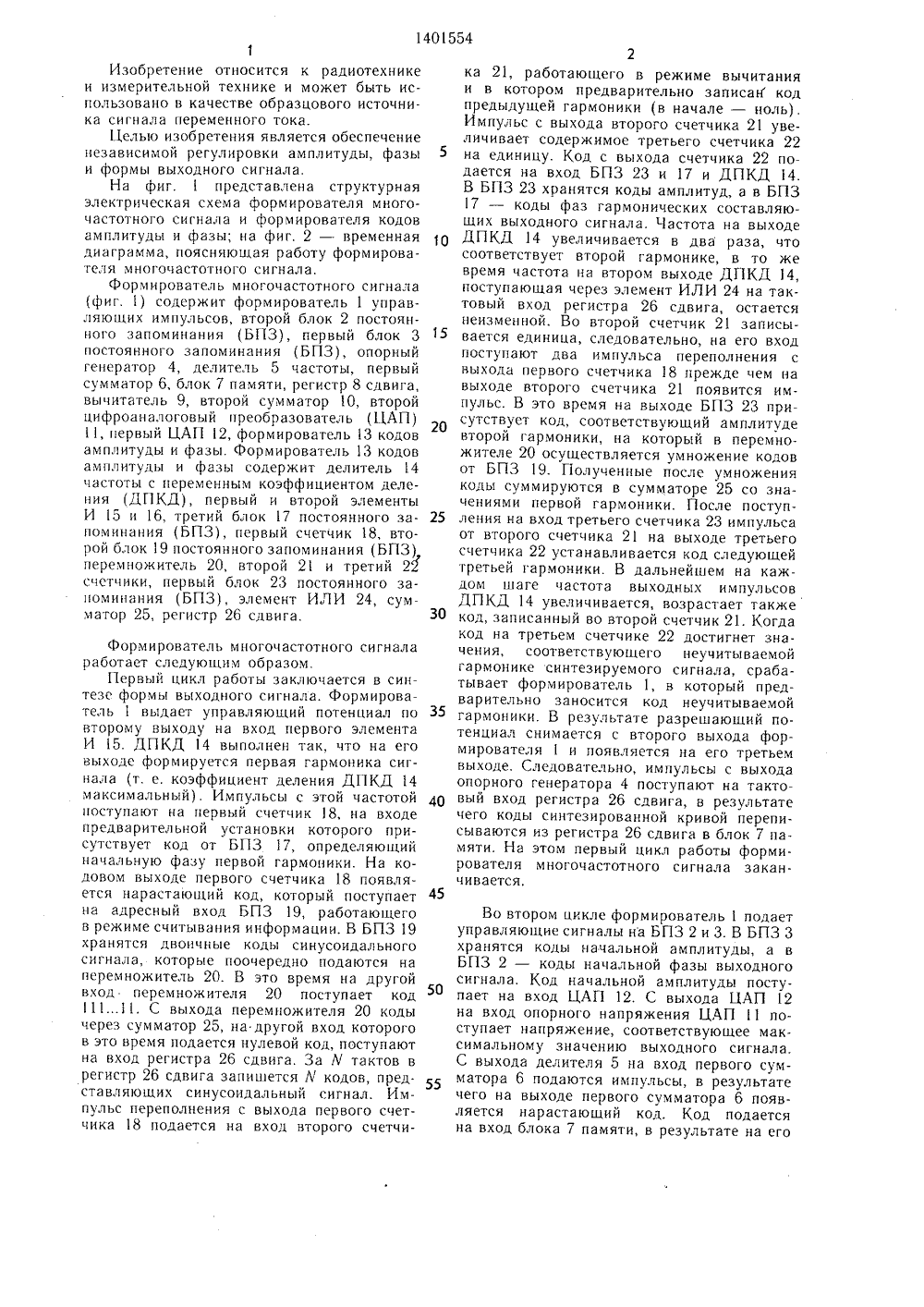

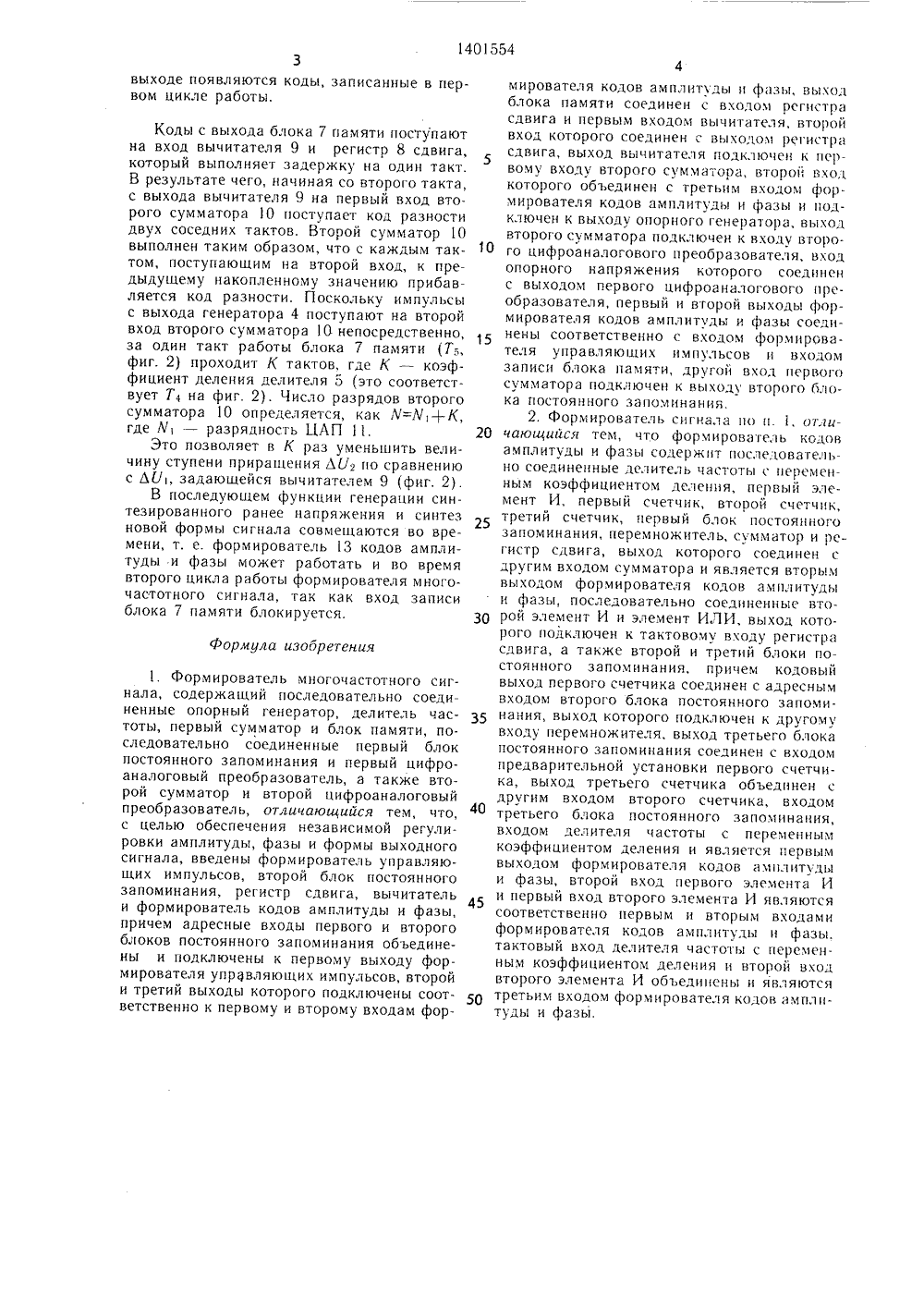

(19) 51) 4 Н 03 В 19/О ИСАНИЕ ИЗОБРЕТЕНИ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Омский институт инженеров железнодорожного транспорта(56) Авторское свидетельство СССР160522, кл. Н 03 В 19/00, 07.03.84.Авторское свидетельство СССР1197043, кл. Н 03 В 19/00, 03.10.84. (54) ФОРМИРОВАТЕЛЬ МНОГОЧАСТОТНОГО СИГНАЛА(57) Изобретение относится к радиотехнике и измерительной технике и м. б. использовано в качестве образцового источника сигнала. Цель изобретения - обеспечение независимой регулировки амплитуды, фазы и формы выходного сигнала. Устройство содержит блок 3 постоянного запоминания (БПЗ), опорный г-р 4, делитель 5 частоты, сумматоры 6 и 1 О, блок 7 памяти, ЦАП 1 и 2. Для достижения цели в устройство введены формирователь 1 управляюгцих импульсов, БПЗ 2, регистр 8 сдвига, вычитатель 9, формирователь 13 кодов амплитуды и фазы. Первый цикл работы заключается в синтезе формы выходного сигнала. Во втором цикле формирователь 1 подает управляюгцие сигналы на БПЗ 2 и 3. В БПЗ 3 хранятся коды начальной амплитуды, а в БПЗ 2 - . коды начальной фазы выходного сигнала.з. и. ф-лы, 2 ил.1401554 35 40 45 50 55 1Изобретение относится к радиотехнике и измерительной технике и может быть использовано в качестве образцового источника сигнала переменного тока.Целью изобретения является обеспечение независимой регулировки амплитуды, фазы и формы выходного сигнала,На фиг.представлена структурная электрическая схема формирователя многочастотного сигнала и формирователя кодов амплитуды и фазы; на фиг, 2 - временная диаграмма, поясняющая работу формирователя многочастотного сигнала.Формирователь многочастотного сигнала (фиг. 1) содержит формирователь 1 управляющих импульсов, второй блок 2 постоянного запоминания (БПЗ), первый блок 3 постоянного запоминания (БПЗ), опорный генератор 4, делитель 5 частоты, первый сумматор 6, блок памяти, регистр 8 сдвига, вычитатель 9, второй сумматор О, второй цифроаналоговый преобразователь (ЦАП)1, первый ЦАП 12, формирователь 13 кодов амплитуды и фазы. Формирователь 13 кодов амплитуды и фазы содержит делитель 14 частоты с переменным коэффициентом деления (ДПКД), первый и второй элементы И 15 и 16, третий блок 17 постоянного запоминания (БПЗ), первый счетчик 18, второй блок 19 постоянного запоминания (БПЗ) перемножитель 20, второй 2 и третий 22 счетчики, первый блок 23 постоянного запоминания (БПЗ), элемент ИЛИ 24, сумматор 25, регистр 26 сдвига. Формирователь многочастотного сигнала работает следующим образом.Первый цикл работы заключается в синтезе формы выходного сигнала. Формирователь 1 выдает управляющий потенциал по второму выходу на вход первого элемента И 15. ДПКД 14 выполнен так, что на его выходе формируется первая гармоника сигнала (т. е. коэффициент деления ДПКД 14 максимальный). Импульсы с этой частотой поступают на первый счетчик 18, на входе предварительной установки которого присутствует код от БПЗ 1, определяющий начальную фазу первой гармоники, На кодовом выходе первого счетчика 18 появляется нарастаюший код, который поступает на адресный вход БПЗ 19, работаюшего в режиме считывания информации. В БПЗ 19 хранятся двоичные коды синусоидального сигнала, которые поочередно подаются на еремножитель 20. В это время на другой вход перемножителя 20 поступает код 11111. С выхода перемножителя 20 коды через сумматор 25, на другой вход которого в это время подается нулевой код, поступают на вход регистра 26 сдвига. За Ф тактов в регистр 26 сдвига запишется М кодов, пред. ставляющих синусоидальный сигнал. Импульс переполнения с выхода первого счетчика 18 подается на вход второго счетчи 5 10 15 20 25 30 2ка 21, работающего в режиме вычитания и в котором предварительно записан код предыдущей гармоники (в начале - ноль). Импульс с выхода второго счетчика 21 увеличивает содержимое третьего счетчика 22 на единицу. Код с выхода счетчика 22 подается на вход БПЗ 23 и 17 и ДПКД 14. В БПЗ 23 хранятся коды амплитуд, а в БПЗ 17 - коды фаз гармонических составляющих выходного сигнала. Частота на выходе ДПКД 14 увеличивается в два раза, что соответствует второй гармонике, в то же время частота на втором выходе ДПКД 14, поступающая через элемент ИЛИ 24 на тактовый вход регистра 26 сдвига, остается неизменной. Во второй счетчик 21 записывается единица, следовательно, на его вход поступают два импульса переполнения с выхода первого счетчика 18 прежде чем на выходе второго счетчика 21 появится импульс. В это время на выходе БПЗ 23 присутствует код, соответствующий амплитуде второй гармоники, на который в перемножителе 20 осуществляется умножение кодов от БПЗ 19. Полученные после умножения коды суммируются в сумматоре 25 со значениями первой гармоники. После поступления на вход третьего счетчика 23 импульса от второго счетчика 21 на выходе третьего счетчика 22 устанавливается код следующей третьей гармоники, В дальнейшем на каждом шаге частота выходных импульсов ДПКД 14 увеличивается, возрастает также код, записанный во второй счетчик 21. Когда код на третьем счетчике 22 достигнет значения, соответствующего неучитываемой гармонике синтезируемого сигнала, срабатывает формирователь 1, в который предварительно заносится код неучитываемой гармоники. В результате разрешающий потенциал снимается с второго выхода формирователя 1 и появляется на его третьем выходе. Следовательно, импульсы с выхода опорного генератора 4 поступают на тактовый вход регистра 26 сдвига, в результате чего коды синтезированной кривой переписываются из регистра 26 сдвига в блок 7 памяти, На этом первый цикл работы формирователя многочастотного сигнала заканчивается. Во втором цикле формирователь 1 подает управляюшие сигналы на БПЗ 2 и 3. В БПЗ 3 хранятся коды начальной амплитуды, а в БПЗ 2 - коды начальной фазы выходного сигнала. Код начальной амплитуды поступает на вход ЦАП 12. С выхода ЦАП 12 на вход опорного напряжения ЦАП1 поступает напряжение, соответствующее максимальному значению выходного сигнала. С выхода делителя 5 на вход первого сумматора 6 подаются импульсы, в результате чего на выходе первого сумматора 6 появляется нарастающий код. Код подается на вход блока 7 памяти, в результате на еговыходе появляются коды, записанные в первом цикле работы. Коды с выхода блока 7 памяти поступают на вход вычитателя 9 и регистр 8 сдвига, который выполняет задержку на один такт. В результате чего, начиная со второго такта, с выхода вычитателя 9 на первый вход второго сумматора 10 поступает код разности двух соседних тактов. Второй сумматор 10 выполнен таким образом, что с каждым тактом, поступающим на второй вход, к предыдущему накопленному значению прибавляется код разности. Поскольку импульсы с выхода генератора 4 поступают на второй вход второго сумматора 10 непосредственно, за один такт работы блока 7 памяти (Т- фиг. 2) проходит К тактов, где К - коэффициент деления делителя 5 (это соответствует Т 4 на фиг. 2). Число разрядов второго сумматора 10 определяется, как %=%+К, где М - разрядность ЦАП 11.Это позволяет в К раз уменьшить величину ступени приращения ЛУ по сравнению с Лсlь задающейся вычитателем 9 (фиг. 2).В последующем функции генерации синтезированного ранее напряжения и синтез новой формы сигнала совмещаются во времени, т. е. формирователь 13 кодов амплитуды и фазы может работать и во время второго цикла работы формирователя многочастотного сигнала, так как вход записи блока 7 памяти блокируется. 5 10 15 20 25 30 35 40 45 50 Формула изобретения 1. Формирователь многочастотного сигнала, содержащий последовательно соединенные опорный генератор, делитель частоты, первый сумматор и блок памяти, последовательно соединенные первый блок постоянного запоминания и первый цифроаналоговый преобразователь, а также второй сумматор и второй цифроаналоговый преобразователь, отличающийся тем, что, с целью обеспечения независимой регулировки амплитуды, фазы и формы выходного сигнала, введены формирователь управляющих импульсов, второй блок постоянного запоминания, регистр сдвига, вычитатель и формирователь кодов амплитуды и фазы, причем адресные входы первого и второго блоков постоянного запоминания объединены и подключены к первому выходу формирователя управляющих импульсов, второй и третий выходы которого подключены соответственно к первому и второму входам формирователя кодов амплитуды и фазы, выход блока памяти соединен с входом регистра сдвига и первым входом вычитателя, второй вход которого соединен с выходом регистра сдвига, выход вычитателя подключен к первому входу второго сумматора, второй ьход которого объединен с третьим входом формирователя кодов амплитуды и фазы и подключен к выходу опорного генератора, выход второго сумматора подключен к входу второго цифроаналогового преобразователя, вход опорного напряжения которого соединен с выходом первого цифроаналогового преобразователя, первый и второй выходы формирователя кодов амплитуды и фазы соединены соответственно с входом формирователя управляющих импульсов и входом записи блока памяти, другой вход первого сумматора подключен к выходу второго блока постоянного запоминания.2. Формирователь сигнала по и. 1, отличающийся тем, что формирователь кодов амплитуды и фазы содержит последовательно соединенные делитель частоты с переменным коэффициентом деления, первый элемент И, первый счетчик, второй счетчик, третий счетчик, первый блок постоянного запоминания, перемножитель, сумматор и регистр сдвига, выход которого соединен с другим входом сумматора и является вторым выходом формирователя кодов амплитуды и фазы, последовательно соединенные второй элемент И и элемент ИЛИ, выход которого подключен к тактовому входу регистра сдвига, а также второй и третий блоки постоянного запоминания, причем кодовый выход первого счетчика соединен с адресным входом второго блока постоянного запоминания, выход которого подключен к другому входу перемножителя, выход третьего блока постоянного запоминания соединен с входом предварительной установки первого счетчика, выход третьего счетчика объединен с другим входом второго счетчика, входом третьего блока постоянного запоминания, входом делителя частоты с переменным коэффициентом деления и является первым выходом формирователя кодов амплитуды и фазы, второй вход первого элемента И и первый вход второго элемента И являются соответственно первым и вторым входами формирователя кодов амплитуды и фазы, тактовый вход делителя частоты с переменным коэффициентом деления и второй вход второго элемента И объединены и являются третьим входом формирователя кодов амплитуды и фазы.авцова Состав Техред И Тираж 92 нного комитета Москва, Ж - 35 графическое прРедактор Г. ВолковаЗаказ 253952В Н И И 11 И Государстве113035,Производственно-пол тель А. Мишакин . Верес Корректо 8 Подписи СССР по делам изобретеРаушская наб., д. 4/ едприятие, г. Ужгород, ул рО. Крое ий и открытий

СмотретьЗаявка

4155544, 03.12.1986

ОМСКИЙ ИНСТИТУТ ИНЖЕНЕРОВ ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА

ЗАХАРЕНКО АЛЕКСАНДР НИКОЛАЕВИЧ, ШАХОВ ВЛАДИМИР ГРИГОРЬЕВИЧ

МПК / Метки

МПК: H03B 19/00

Метки: многочастотного, сигнала, формирователь

Опубликовано: 07.06.1988

Код ссылки

<a href="https://patents.su/4-1401554-formirovatel-mnogochastotnogo-signala.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь многочастотного сигнала</a>

Предыдущий патент: Цифровой управляемый генератор

Следующий патент: Генератор шумовых сигналов

Случайный патент: Способ снижения магнитного поля технического объекта