Система передачи дискретной информации с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1283990

Авторы: Захарченко, Киреев, Мариевич

Текст

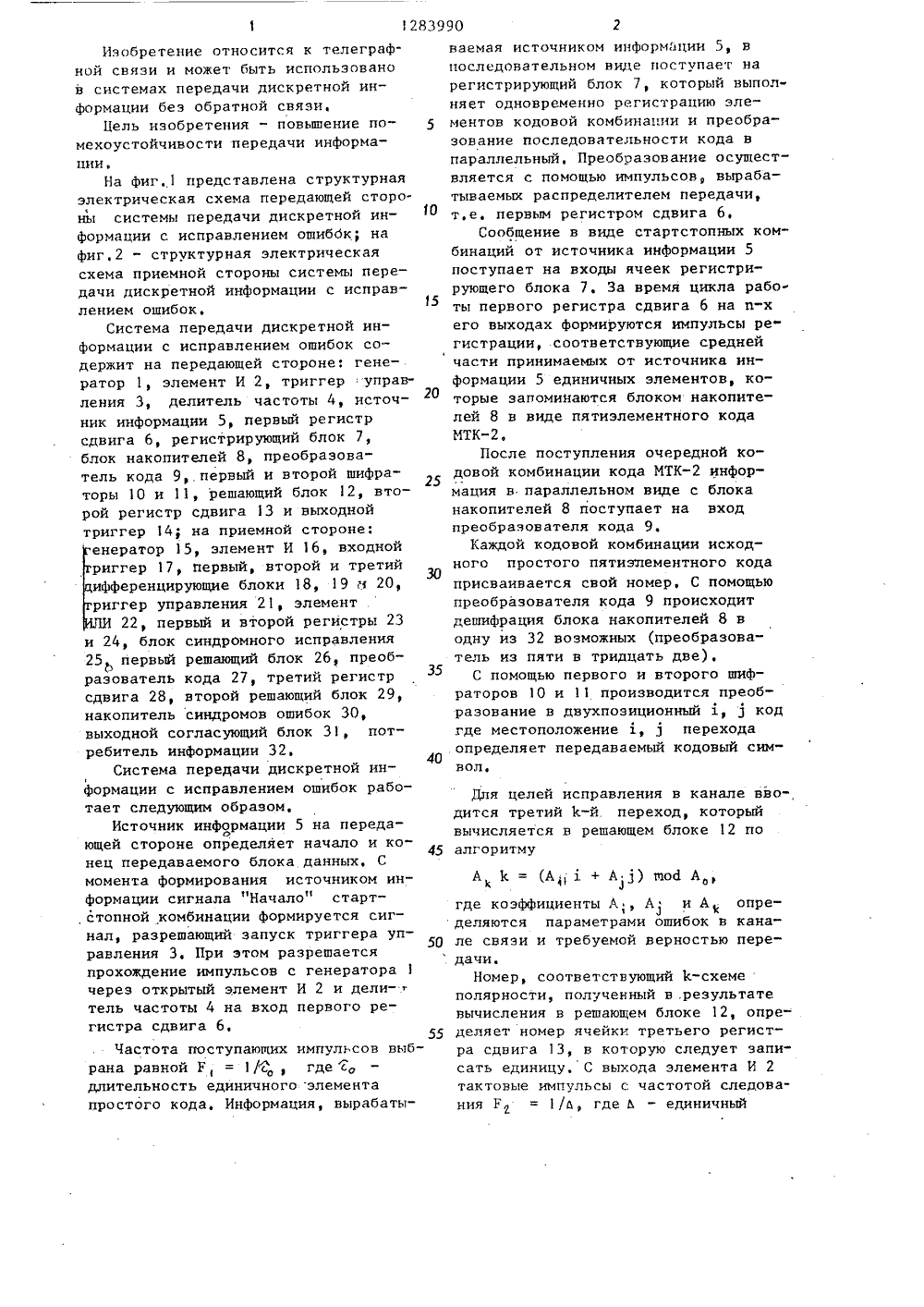

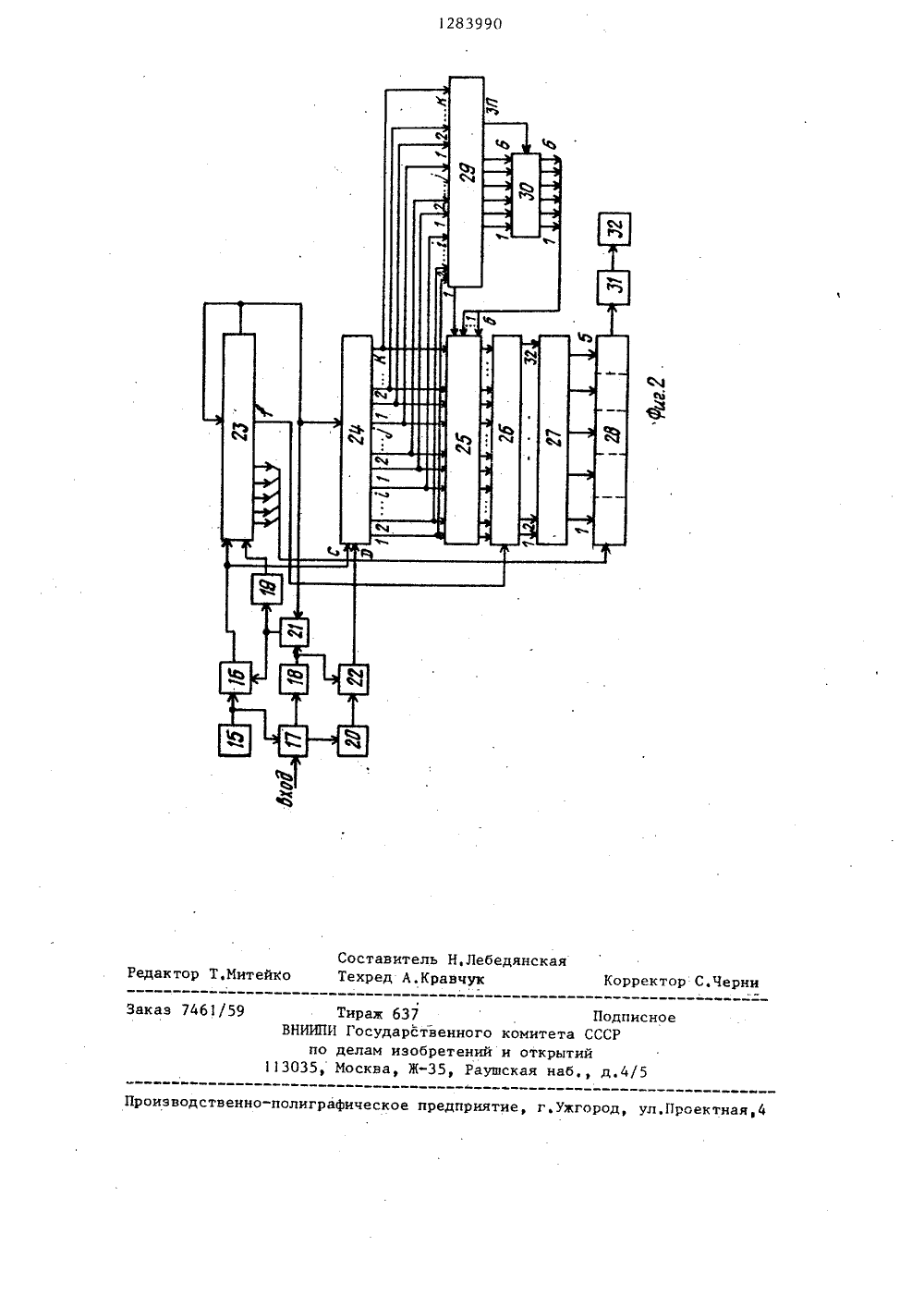

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 119) 111) 4 Н 04 1.111 ТЕНИЯ оли- вы- требиверя-еОСУДАРСТБЕКНЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ ИЭ(71) Одесский электротехническийинститут связи им, А.С.Попова(56) Авторское свидетельство СССРВ 1111258, кл. Н 04 Ь 1/12, 1983.(54) СИСТЕМА ПЕРЕДАЧИ ДИСКРЕТНОЙИНФОРМАЦИИ С ИСПРАВЛЕНИЕМ ОШИБОК(57) Изобретение относится к телеграфной связи, Цель изобретения -повышение прмехоустойчивости пере"дачи информации, Система содержит напередающей стороне: г-р, эл-т И,триггер управления, делитель частоты, источник информации, два регистрасдвига, регистрирующий блок, блок накопителей, преобразователь кода,два шифратора, решающий блок (РБ)и выходной триггер, а на приемнойстороне: г-р 15, эл-т И 16, входнойтриггер 17, три дифференцирующихблока 18, 19 и 20, триггер 21 управления, эл-т ИЛИ 22, три регистрасдвига 23, 24 и 28, блок синдромногоисправления (БСИ) 25, два РБ 26 и29 преобразователь кода 27, нактель синдромов ошибок (НСО)30,ходной согласующий блок 31 и потель 32 информации, В РБ 29 проется условие исправления ошибок иформируется синдром ошибок, по которому в БСИ 25 производится исправление ошибок в принимаемой кодовойкомбинации. В НСО 30 хранится информация об ошибочно принятом знача. щем моменте модуляции в кодовойинформации, Цель достигается введнием БСИ 25, РБ 29 и НСО 30, 2 илЧастота по рана равной длительность простого код ступающих 1"о ) единичног а, Информаимпульсов вы где со элемента вырабатыИзобретение относится к телеграфной связи и может быть использовано в системах передачи дискретной информации без обратной связи,Цель изобретения - повышение помехоустойчивости передачи информации.На фиг,1 представлена структурная электрическая схема передающей стороны системы передачи дискретной информации с исправлением ошиббк; на фиг.2 - структурная электрическая схема приемной стороны системы передачи дискретной информации с исправлением ошибок.Система передачи дискретной информации с исправлением ошибок содержит на передающей стороне: генератор 1, элемент И 2, триггер управ. ления 3, делитель частоты 4, источник информации 5, первый регистр сдвига 6, регистрирующий блок 7, блок накопителей 8, преобразователь кода 9,.первый и второй шифраторы 10 и 11, решающий блок 12, второй регистр сдвига 13 и выходной триггер 14 на приемной стороне: енератор 15, элемент И 16, входной риггер 17, первый, второй и третий ифференцирующие блоки 18, 19 ч 20, риггер управления 21, элементИ 22, первый и второй регистры 23 и 24, блок синдромного исправления 25, первый решающий блок 26, преобразователь кода 27, третий регистр сдвига 28, второй решающий блок 29, накопитель синдромов ошибок 30, выходной согласующий блок 31, потребитель информации 32.Система передачи дискретной информации с исправлением ошибок работает следующим образом, Источник информации 5 на передао ющей стороне определяет начало и конец передаваемого блока данных, С момента формирования источником информации сигнала "Начало" стартстопной комбинации формируется сигнал, разрешающий запуск триггера управления 3. При этом разрешается прохождение импульсов с генератора 1 через открытый элемент И 2 и дели-. тель частоты 4 на вход первого регистра сдвига 6, 5 где коэффделяются ле связи идачи,Номер, соответполярности, пол.вычисления в реш м ствующ чен ный в .результате блоке 12, опреетьего регистую следует запиэлемента И 2ающе ки т деляет номер яч ра сдвига 13, в сать единицу, С тактовые импуль1/,от выхода ы с ча тотои следоваединичный де й 5 10 15 20 25 30 ваемая источником информгции 5, впоследовательном виде поступает нарегистрирующий блок 7, который выполняет одновременно регистрацию элементов кодовой комбинации и преобразование последовательности кода впараллельный, Преобразование осуществляется с помощью импульсов, вырабатываемых распределителем передачи,т.е, первым регистрам сдвига 6,Сообщение в виде стартстопвых комбинаций от источника информации 5поступает на входы ячеек регистрирующего блока 7. За время цикла работы первого регистра сдвига 6 на и-хего выходах формируются импульсы регистрации, соответствующие среднейчасти принимаемых от источника информации 5 единичных элементов, которые запоминаются блоком накопителей 8 в виде пятиэлементного кодаМТК.После поступления очередной кодовой комбинации кода МТКинформация в параллельном виде с блоканакопителей 8 поступает на входпреобразователя кода 9,Каждой кодовой комбинации исходного простого пятижементного кодаприсваивается свой номер. С помощьюпреобразователя кода 9 происходитдешифрация блока накопителей 8 водну из 32 возможных (преобразователь из пяти в тридцать две).С помощью первого и второго шифраторов 10 и 11 производится преобразование в двухпозиционный , 3 кодгде местоположение 1, 3 переходаопределяет передаваемый кодовый символ. Для целей исправления в канале вводится третий 1-й переход, который вычисляется в решающем блоке 12 по алгоритму А 1 с = (А 1,1+ А 1) ш циенты А, Аи Аопрепараметрами ошибок в кана- требуемой верностью пере128309 55 3элемент, используемый при формиронани гигнялон в кодоных словах, , чис. ло возможных кодовых слов при этом составляет 2 Т./д,где Т винтервал времени простого кода, но выбираются только те, которые удовлетворяют алгоритму. С третьего регистра сдвига 13 информация в виде переходов (смен полярностей) последовательно считывается с его выхода на вход выходного триггера 14. С помощью импульса, снимаемого с выхода первогорегистра сдвига 6, соответствующего началу стартстопного цикла, и импуль сов с выхода второго регистра сдвига 3 непрерывно формируются и пере даются в канал трехэлементные ко:довые комбинации,Длительность элемента, соответст" вующего стартстопной комбинации, определяется. расстоянием от сигнала "Конец - начало" стартстопного цикла,до момента появления д-го перехода с выхода регистра сднига 13. Расстояние между 1 и 1, 1 и к переходами, Е-м переходом и сигналом "Конец - начало" цикла выбрано не менее со е Следовательно в канал непрерывнопоступают сформированные кодовые комбинации с постоянным числом переходов значащих моментов модуляции.Из общего числа возможных реализацийотбираются только сигналы, в которыхчисло переходов равно четырем, местоположение переходов удовлетворяетуказанному алгоритму и расстояниемежду 1, ,1, Е переходами не меньше,чем на интервале стартстопного циклаисходного кода,С выхода выходного триггера 4сигнал поступает в канал связи,Информация с канала связи поступает на входной триггер 17, где осуществляется временная привязка фронтов принимаемых единичныхэлементовк генератору 15. С помощью первогои второго дифференцирующих блоков18 и 19 производится выделение фронтов принимаемого сигнала (переходыиз единицы в ноль типа "старт" и переходы иэ ноля в единицу).Стартовый переход, пройдя второйдифференцирующнй блок 19,устанавлинает триггер управления 21 в единичное состояние, разрешая прохождениетактовых импульсов с генератора 15на входы первого регистра сдвига 23,цикл работы которого выбран ТЦ=Нд,где И - количество ячеек первого регистра сдвига 23, равное числу возможного местоположения значащих моментов носстанонления н принимаемойкодовой комбинации, а й - длительность единичного элемента преобразованного кода. С помощью третьегодифференцирующего блока 20 выделяется переход, записывающий единицу,в первую ячейку первого регистрасдвига 23,Под действием управляющих импульсов, поступающих на первый вход первого регистра сдвига 23, на его выходах поочередно появляютсяимпульсы, управляющие приемной сторонойсистемы в целом,2 О Выходы первого и второго дифференцирующнх блОков 18 и 19 объединены вторым элементом ИЛИ 22. Одновремен но с работой первого регистра сдвига 23 начинает работу и второй ре гистр сдвига 24Последний вырабатывает зоны с таким расчетом, чтобы принимаемые Е переходы находились в середине зон Ь анализа, например в которых при- ЗО нимаются ,1,1 с переходы запоминаются в ячейках второго регистра сдвига 24, который является накопителем, ,Параллельно номера этих зон (ячеек) тпоступают на блок синдромного испЗ 5. равления 25 и второй решающий блок29, в котором проверяется указанный алгоритм и формируется синдром ошибок, по которому в блоке синдромного исправления 25 производится исп 40 равление ошибки в принимаемой кодовой комбинации, В накопителе синдрома ошибок 30 хранится информация об ошибочно принятом значащем моменте модуляции в кодовой комбинации.45 С выхода блока синдромного исправления 25 номера соответствующих значащих моментов модуляции поступают на входы первого решающего блока 26. Первый решающий блок 26 преобразует номера , 1, Е ячеек блока синдромного исправления 25 в номер кодовой комбинации простого пятиэлементного кода, На выходе первого решающего блока 26 появляетсясигнал, соответствующий номеру комбинации кода ИТК, вырабатываемой источником информации 5. Проклю.чение входов и выходов первого решающего блока 26 производится импульсом.считывания, снимаемым с первого регистра сдвига 23.Выходы преобразователя кода 27 подключены к входам ячеек третьего регистра сдвига 28, Преобразование производится в очередном стартостопном цикле с помощью пяти управляющих импульсов, вырабатываемых первым регистром сдвига 23 с выходов и, которые соответствуют моментам смен полярности единичных элементов в комбинации пятиэлементного кода, выдаваемого потребителюинформации 32 через выходной согласующий блок 31.С выхода последней ячейки третьего регистра сдвига 28 информации в виде единичных переходов, соответствующих значащим моментам восстановления простого кода МТК, поступает на выход согласующего блока 31, с помощью которого формируется кодовая комбинация, выдаваемая потребителю информации 32.Формула изобретенияСистема передачи дискретной информации с исправлением ошибок содержащая на передающей стороне последовательно соединенные генератор, элемент И, к второму входу которого подключен выход триггера управления делитель частоты, к входу которого подключен первый вход второго регист ра сдвига, и первый регистр сдвига, . источник информации, управляющий и запрещающий выходы которого подключены к первому и второму входам триггера управления, а информационный выход через регистрирующий блок - к входам блока накопителей, преобразователь кода, первый и второй шифраторы, выходы которых подключены к сигнальным входам второго регистра сдвига и ко входам решающего блока, выходы которого подключены к сигнальным входам второго регистра сдвига, а также выходной триггер, к одному входу которого подключеи соответствующий выход первого регистра сдни 1 н, а к другомувходу - выход второго регистра сдвига, а на приемной стороне - генератор, выход которого через элемент Иподключен к первым входам первогои второго регистров сдвига, ко входупервого дифференцирующего блока через входной триггер, выход которогочерез второй дифференцирующий блок, 10 соединенный с первым входом элементаИЛИ, подключен к первому входу триггера управления, выход которого подключен ко второму входу элемента Ии через третий дифференцирующий блок 15 к второму входу первого регистрасдвига, один выход которого соединенсо своим установочным входом, совторым входом триггера управления ис установочным входом второго ре гистра сдвига, ко второму входу которого подключен выход элемента ИЛИ,последовательно соединенные первыйрешающий блок, к одному входу которого подключен соответствующий вы ход первого регистра сдвига, преобразователь кода, третий регистрсдвига и выходной согласующий блоко т л и ч а ю щ а я с я тем, что,с целью повышения помехоустойчивосЗ 0 ти передачи информации, на передающей стороне объединенные выходы и"разрядов первого регистра сдвигаподключены к управляющим входам регистрирующего блока, а выходы блока 35 накопителей через преобразователькода подключены ко входам шифраторовна приемной стороне введены блоксиндромного исправления, выходы которого подключены ко вторым соот ветствующим входам первого решающего блока, а входы - к соответствующим выходам разрядов второго регистра сдвига и через введенные последовательно соединенные второй ре" 45 шающий блок, второй выход которогоподключен ко второму входу блокасиндромного исправления, и накопитель синдромов ошибок - к объединенным третьим входам блока синдромно го исправления.1283990 Составитель Н,Лебедянска Техред А.Кравчук Редактор Т,Мит орректор С.Черни каз 7461/59 637арственного комитетаизобретений и открытий Ж, Раушская наб Тираж НИИПИ Гос

СмотретьЗаявка

3907985, 10.06.1985

ОДЕССКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. А. С. ПОПОВА

ЗАХАРЧЕНКО НИКОЛАЙ ВАСИЛЬЕВИЧ, КИРЕЕВ ИГОРЬ АНАТОЛЬЕВИЧ, МАРИЕВИЧ АЛЕКСАНДР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H04L 1/12

Метки: дискретной, информации, исправлением, ошибок, передачи

Опубликовано: 15.01.1987

Код ссылки

<a href="https://patents.su/5-1283990-sistema-peredachi-diskretnojj-informacii-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи дискретной информации с исправлением ошибок</a>

Предыдущий патент: Устройство согласования скоростей цифровых потоков при передаче сигналов цифрового радиовещания

Следующий патент: Устройство тактовой синхронизации

Случайный патент: Штанговый конвейер для транспортировки сыпучего груза