Микропрограммное устройство управления с контролем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1267413

Авторы: Благодарный, Малахов, Тимонькин, Ткаченко, Харченко

Текст

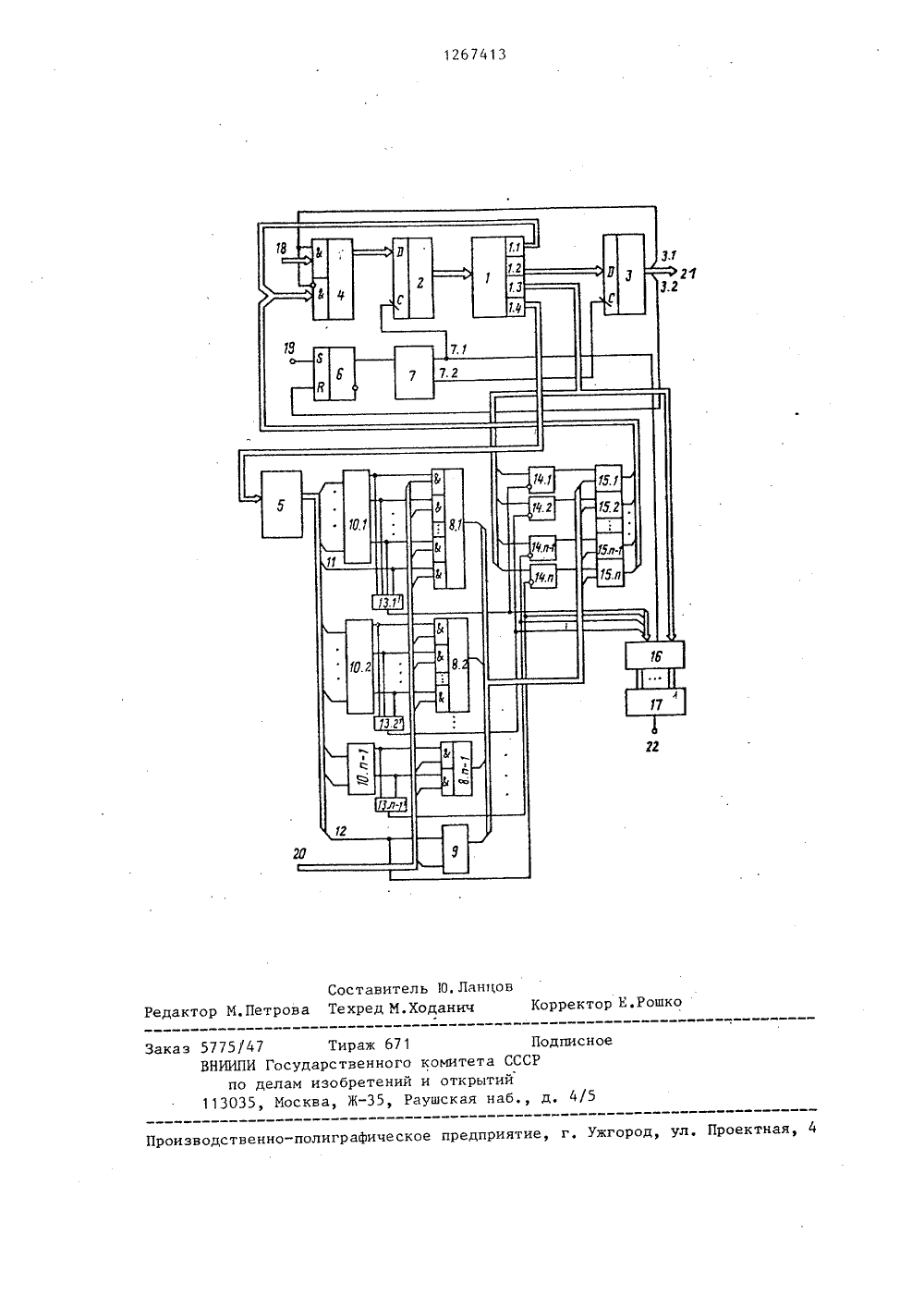

,1267 19) Р 9/22, 11/00 ССРРЫТИЙ ГОСУДАРСТВЕННЫЙ КОМИТ ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОПИСАНИЕ РЕТЕНИЯ ДЕТЕЛЬСТ 884325/24 41,04,85.0.10.86. Бюл. М/22, 1976.ство СССР9/22, 1983,54) МИКРО АВЛЕНИЯ С 57) Изобр втоматики может бы СТРОИСТВО УПСовоку игнуть Ф е- э(56) АвУ 5032АвтР 1091 ПРОГРАММНОЕ УКОНТРОЛЕМтение относится к област и вычислительной техники ь использовано при построении центральных устроиств построения ЭВМ и вычислительных устройствс микропрограммным управлением. Цельизобретения - сокращение оборудования за счет уменьшения объема памятимикрокоманд. Устройство содержит блокпамяти микрокоманд, регистр адреса,регистр микрокоманд, коммутатор адреса, дешифратор логических условий,триггер пуска, генератор тактовыхимпульсов, группу коммутаторов логических условий, элемент И, группу блоков элементов ИЛИ, две группы элементов ИЛИ, группу элементов И, блокэлементов И и элемент ИЛИ. пность блоков позволяет доли изобретения. 1 ил.1267413 этих режимах,ит Изобретение относится х автоматике и вычислительной технике и можетбыть использовано при построениицентральных устройств управления ЭВМи вычислительных устройств с микропрограммным управлением,Цель изобретения -. сокращениеоборудования за счет уменьшения Объема памяти микрокоманд.10На чертеже приведена Функциональная схема микропрограммного, устройства управления с контролем,Микропрограммное устройство управления с контролем содержит блок15памяти микрокоманд с выходами 1 -1.;,регистр 2 адреса, регистр 3 микрокоманд с выходами 3, кснц командыи 3 конца, работы, ксммута 1 ООадреса дешифратор 5 логических ус 2 Оловий, триггер 8 пуска., генератор 7тактовых импульсов с первым 7, ивторым 7, выходами, с .первого 8, по(и)-й блоки эттементов ИЛИ 10, - 10,.,первый выход 11 дешифратора логичес -ких условий, второй выход 12 дешифратора логических условий, вторуюгруппу из элемс."-ттов И 1 И 1., -.1 Зтт,руппу из .леме 11 тсв И 1 тт 1 нву 1 о группу из э 1 емегтгов И;И 15 -15,блок элементов И 16, элеме; т ттЛИ 7вход 18 кода команды, вход 19 пуска,вход 2 0 логических у с 31 с в.-.1 Й выхсгт,21 управления и выход 22 неисправ- З 5 ности.Микропрограммное устэсйство уп раВПЕНИя С КОНТ 1 ОЛЕМ рабОтаЕт СГтЕттуЮщим образом.,В исходном состоянии все элементысхемы находятся ы нулевсм состояниив разряде регистра 3 мч (рокомандсоогветствутощем выходу 3 записанаединица, Цепи приведения элементовустройства в исходное состояние условно не показаны.По сигналу Пуск с входа 19 устройства, посгупающему на вход установки в единицу триггера 6 последний устанавливается в единичное состояние,511 При этом на выходах , тт 7, гецера" тора 7 возбуждаются гтостгедовате 1 ьнссти тактовых импульсови "1 Пс ПЕРВОМУ ТЯКТОВОМУ И 1 Н 1 УттЬСУ1.,ПОСТУ"- пающему на синхровход регистра 2 адреса, поспедний открываегся. При этом код операции являющейся адресом перВсй МИКРОКОМаНДЫ ВЬПСЛНЯЕМОй Мт 1 КРОт, програьгмь 1, через ксммутатог, : посту. пает на информационный вход регистра2 и записывается в нем,По записанному в регистре 2 адресу из блока 1 намяги выбирается соотыетствующтая микрокоманда и поступаетна его выходы 1, - 14. При наличии сиг -нала на синхровходе регистра 3 операционная часть микроксманды с выхода1, блока 1 памяти поступает на информационный вход регистра 3. Сигналымикрооперации с регистра 3 пс"тунают на выход 21 устройства,При формировании адреса очередноймикрокоманды возможны следутощие режимы работы устройства;формирование адреса очередной микрокоманды при выполнении линейныхучастков микропрограмм без проверкилогических условий (первый режим),формирование адреса очередной микрокоманды при реализации условчыхпереходов (втсрой режим).Рассмотрим работу устройства в Первый режим, При считывании микрокоманды из блока 1 памяти адрес очерецной микрокоманды Формируется следующим образом. Чемодифицируемая часть ацреса (старп 1 ие разряды адреса) очередной микрокоманды с выхода 1, блока 1 памяти поступает на соответствующие разряды информационного ВХОДа КСММУтатСРа 4, Ктацт 11 ИЕ РаЗРЯ- ды адреса (мсдчфицируемые) с выхода 1, блокапамяти поступают на соответсттзу 1 ощие входы элементов И группы элементов И 14 -14. Так как в полеблока 1 памяти записан нулевой код, то 11 а выходах дещифрагора 5 и на выходах коммутаторов 81 - 8, и элемента И 9 1 трист тствует нулевой потен 1 тиал и элементы И 1 ч 1 т тт открь 1 ты по ссстветстзующим входам, Таким образом младшие раэряд 11 адреса через группу элементов И 141 - 1: и группу элементттсв И 11 И 15-1 т поступатот на соответствующие разряды информационного входа коммутатора 4 адреса. Вниду отсутствия сигнала микрооперации "1(онец команды" адрес очередной микрокоманды через коммутатор 4 поступает на информанионный вход регистра 2 адреса, При поступлении очередного тактового импульса Ч адрес очередной микрокоманды записывается в регистр 2 адреса. Далее устройство работа.ет в этом режиме аналогично описаннс 1 гу алгоритзначение старших (немодифицируемых) разрядов адреса;знак конкантенации;значение модифицируемыхразрядов адреса; 45значение промодифицированного значения младшего разгде А а л а ряда адреса,При проверке (д ( п ) логических,условий на выходе 1 блока 1 памятипоявляется код проверяемых логическихусловий. Зтот код дешифрируется дешифратором 5. Сигнал с выхода дешифратора 5, соответствующий проверяемой комбинации 1 логических условийпроходит через соответствующие элементы ИЛИ первого 10, -(п.)-го 10блоков элементов ИЛИ на управляющие з 12674Второй режим, Работу устройства во втором режиме рассмотрим в следующих случаях 1при проверке одного логического условия, 5при проверке 1 логических условий (.с п с к, где и - максимальноечисло одновременно проверяемых логических условий, к - число модифицируемых разрядов адреса очередной микО рокоманды);при проверке логических условий в случае и = 1 с;при проверке логических условий в случае п ) 15Если при выполнении текущей микро- команды необходимо проверить значение одного логического условия и произвести ветвление микропрограммы, то на выходе 1 блока 1 памяти бу дет код этого логического условия. Значения логических условий с входа 20 поступают на соответствующие входы коммутаторов логических условий и элемента И 9, В данном случае мо дификация адреса осуществляется только по младшему разряду, какое бы условие не проверялось (первого коммутатора 8 логических условий), его значение поступает на элемент ИЛИ 15, 30 группы элементов ИЛИ 15, -15 п и через него на соответствующий разряд информационного входа коммутатора 4 адреса. Таким образом, адрес очередной микрокоманды определяется следующим выражением входы коммутаторов 8, -8;. На выходах этих коммутаторов появляются сигналы проверяемых логических условий, которые и модифицируют 1 младших разрядов адреса аналогично описанному алгоритму.Если при выполнении текущей микро- команды проверяется и логических условий (число проверяемых логических условий равно числу модифицируемых разрядов адреса), то адрес очередной микрокоманды определится выражениемл,л л лА цсп Аст+ апа и Модификация младших разрядов адреса при этом происходит аналогичноописанному алгоритму. Модификацияп-го разряда происходит следующим образом. На втором выходе 12 дешифратора 5 появляется единичный сигнал,который открывает элемент И 9. Приэтом сигнал п-го логического условияс входа 20 устройства поступает через элемент И 9 на второй вход элемента ИЛИ 15 л. Далее формированиеадреса очередной микрокоманды происходит аналогично описанному алгоритму,Формула изобретенияМикропрограммное устройство управления с контролем, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, коммутатор адреса, генератор тактовых импульсов, триггер пуска, группу из и элементов И (и - количество младших разрядов адреса блока памяти микрокоманд) и первую группу из и элементов ИЛИ, причем первая группа информационных входов коммутатора адреса соединена с группой входов кода команды устройства, выход коммутатора адреса соединен с информационным входом ре-, гистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, -й выход поля адреса старших разрядов которого соединен соответственно с -м информационным входом второй группы коммутатора адреса (1 = 1,ш, гп - количество старших разрядов адреса блока памяти микрокоманд), 1-й информационный вход второй группы которого Ц = ш1, гп + и) соединен с выходом к-го элемента ИЛИ первой группы (к = 1,п), 12 б 74первый вход которого соединен с вы ходом и-го элемента И группы, прямой вход которого соединен с к-м выходом поля адреса младших разрядов блока памяти микрокомапд выход поля микро 5 операций которого соединен с информационным входом регистра микрокоманд, выход поля микроопераций которого подключен к выходу управления устройства., выход признака конца команды регистра микрокоманд соединен с управляющим входом коммутатора адреса, выход признака конца работы регистра микрокоманд соецинен с входом установки в "О" триггера пуска, вход установки в "1" которого подключен к входу пуска устройства, выход триггера пуска соединен с входом запуска генератора тактовых импульсов, первый и второй выходы которого соединены соответственно с синхровходами регистра адреса и регистра микрокоманд, о т л и ч а ю щ е е с я тем, что, с целью сокращения оборудования за счет уменьшения обьема па мяти микрокоманд, оно содержит дешифратор логических условий группу из иблоков элементов ИЛИ, вторую группу из иэлементов ИЛИ, группуиз пкоммутаторов логических услоЗО вий, элемент И, блок элементов И и элемент ИЛИ, причем выход поля логических условий блока памяти микрокоманд еоединен с входом декгифратора логических условий, первый выход которого соединен с первым входом пер 35 ваго элемента ИЛИ второй группы н спервым управляющим входом первого коммутатора группы, остальные управляющие входы которого соединены с одно 4 Д именными входами первого элемента ИЛИ 13 бвторой группы и с одноименными выходами первого блока элементов ИЛИ группы, второй выход дешифратора логических условий соединен с первым входомэлемента И, с инверсным входом и-гоэлемента И группы и с первым входомблока элементов И остальные выходыдешифратора логических условий соединены с входами всех блоков элементовИЛИ группы, выходы с второго по (и -1)-й блоков элементов ИЛИ группы соединены с одноименными входами одноименных элементов ИЛИ второй группыи с одноименными управляющими входами одноименных коммутаторов группы,информационные вхсды всех коммутаторов группы и второй вход элемента Иподключены поразрядно к входу логических условий устройства, выходы спервого по и)-й элементов ИЛИ второй группы соединены соответственнос инверсными входами одноименныхэлементов И группы и с второго пои-й входами блока элементов И, выходы с первого по и)-й коммутаторовгруппы соединены с вторыми входамиодноименных элементов ИЛИ первойгруппы, второй вход и-го элементаИЛИ первой группы соединен с выходомэлемента И, с и+1)-го по 2 п-й входыблока элементов И соединены соответственно с первого по и-й выходами по.ля адреса младших разрядов блокапамяти микрокоманд, 2 п+1)-й входблока элементов И соединен с первымвыходом генератора тактовых импульсов, выходы блока элементовИ соединены с входами элемента ИЛИЙ в 1 ход которого подключен к выходу неисправности устройства.12 б 7413 Составитель 1 О, Ланцовтор М.Петрова Техред М.Ходанич Ко ор Е,Рошко Заказ 5775ВНИИП Тираж 671осударственного комилам изобретений и оМосква, Ж, Раушс писное ета СС тии наб., д, 4/ 30 ул. Проектная, 4 Производственно-полиграфическое предприятие, г, Ужг

СмотретьЗаявка

3884325, 11.04.1985

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

БЛАГОДАРНЫЙ НИКОЛАЙ ПЕТРОВИЧ, МАЛАХОВ ВИКТОР АЛЕКСАНДРОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/36

Метки: контролем, микропрограммное

Опубликовано: 30.10.1986

Код ссылки

<a href="https://patents.su/5-1267413-mikroprogrammnoe-ustrojjstvo-upravleniya-s-kontrolem.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления с контролем</a>

Предыдущий патент: Устройство микропрограммного управления

Следующий патент: Микропрограммное устройство управления с контролем

Случайный патент: Способ оределения скоростей распространения упругих волн