Устройство для вычисления систем логических функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

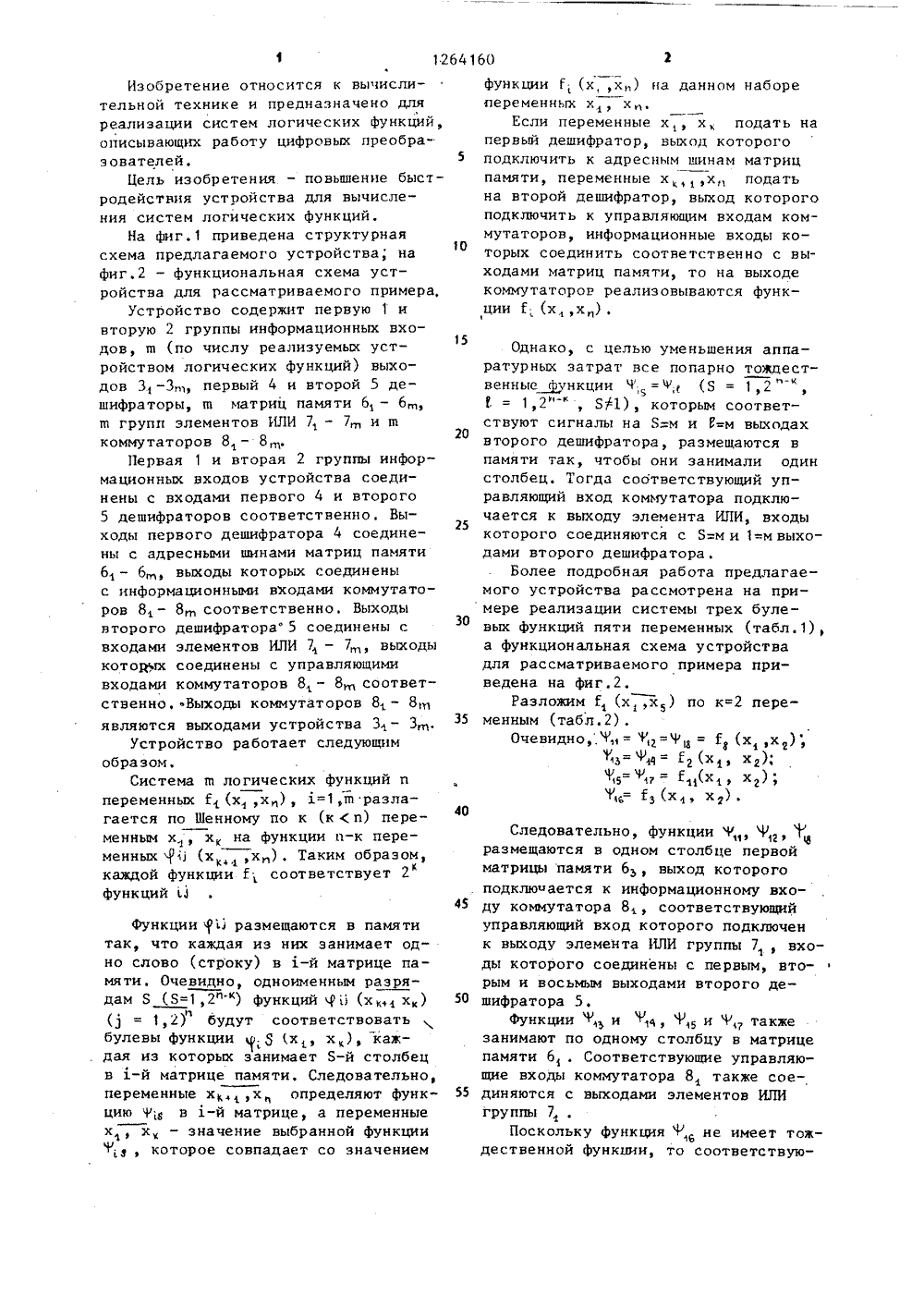

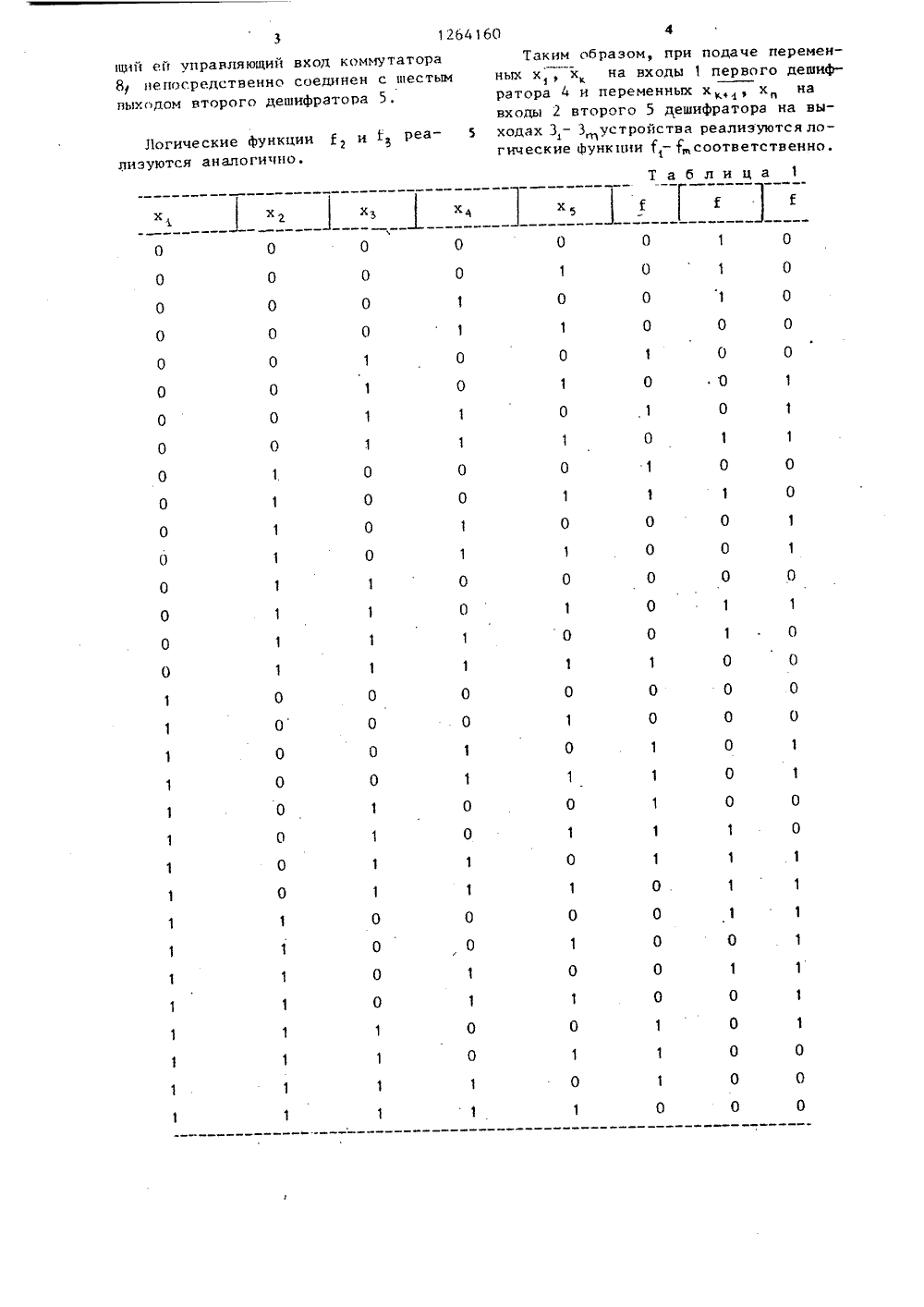

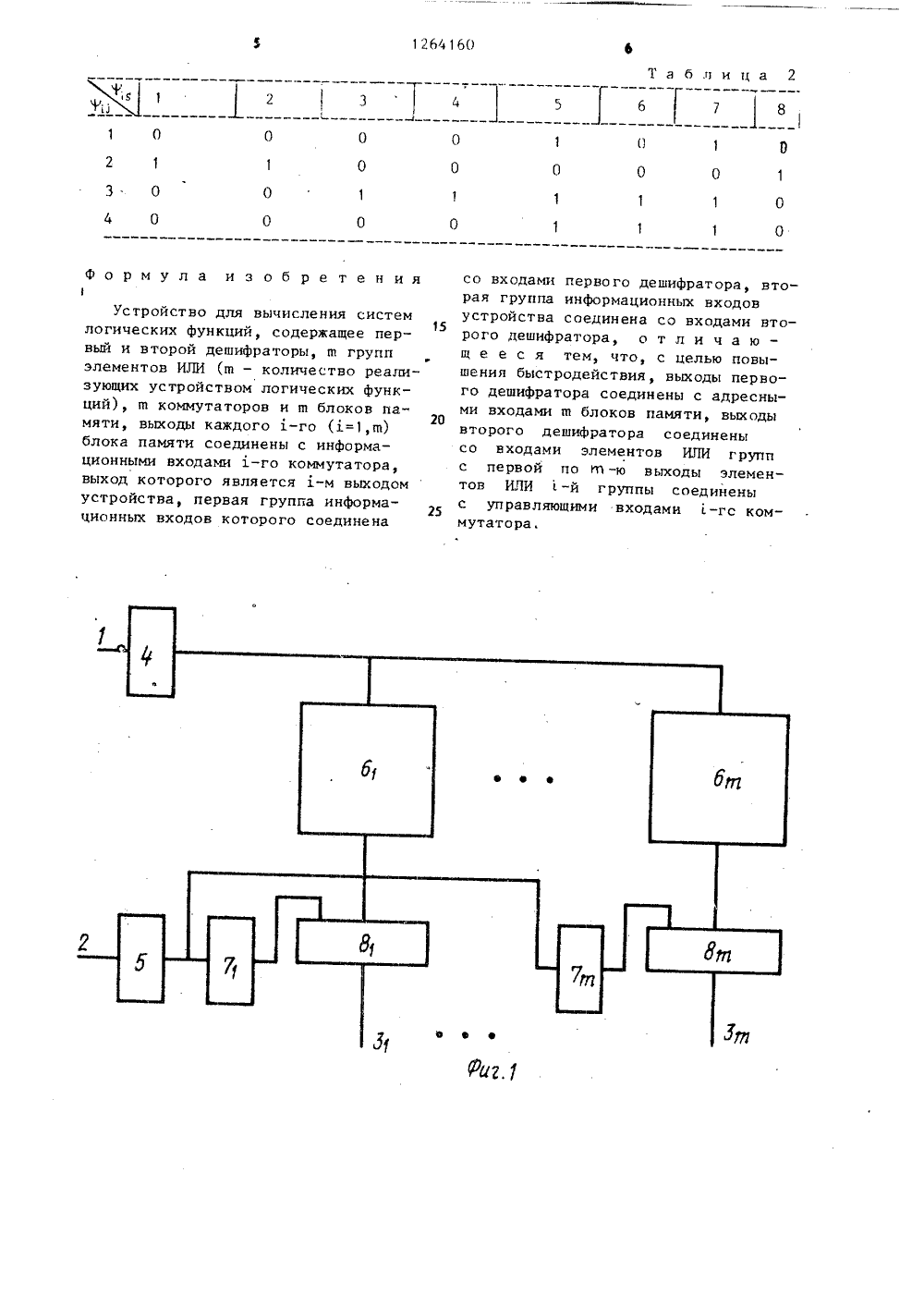

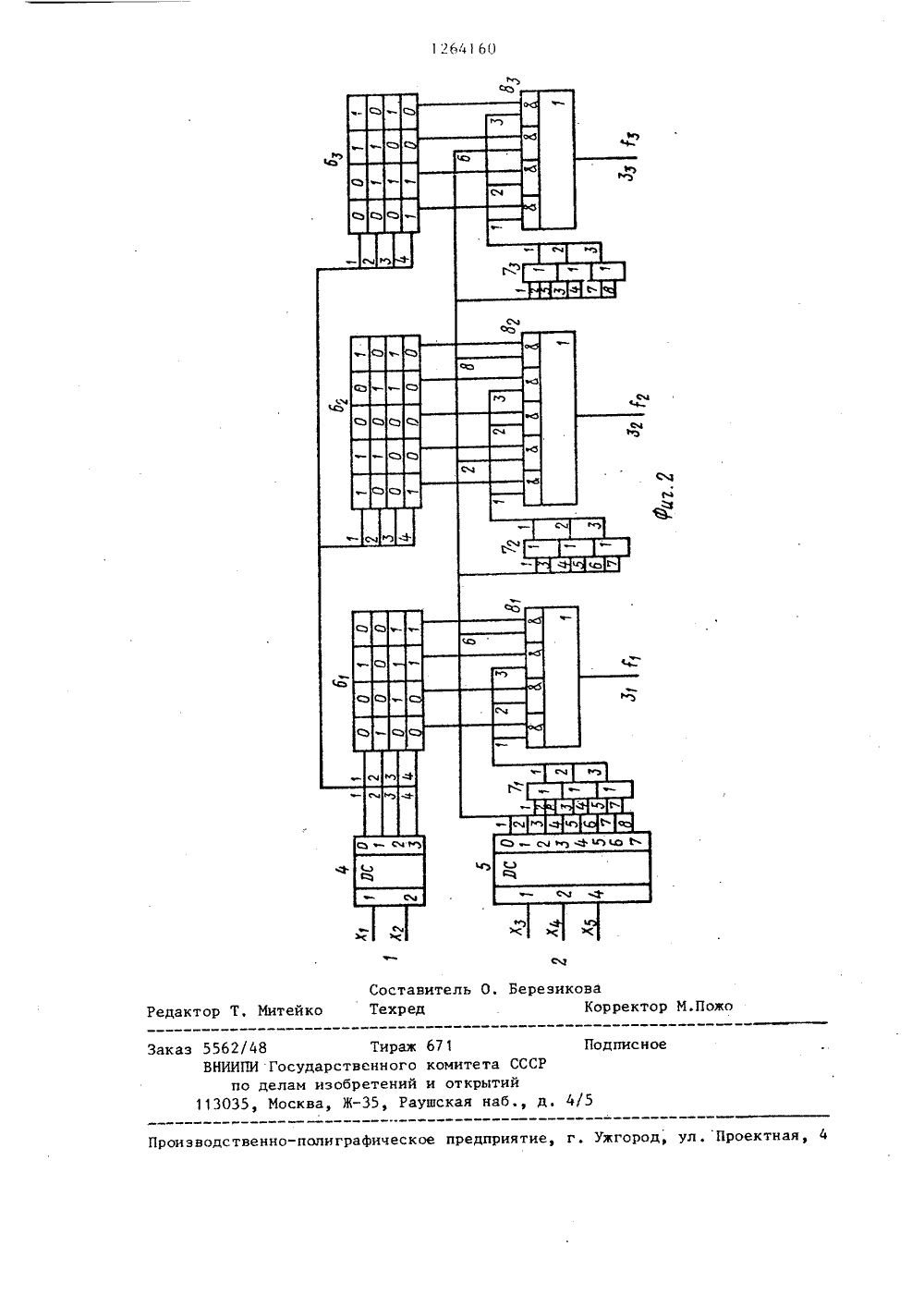

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК1264 84 606 ОПИСАНИЕ ИЗОБРЕТЕНИ е фмр СКОМУ СВИДЕТЕЛЬ У 38.И. Бе Криниц евичкий тельст 7/00, льство Р 7/00 ВЫЧИСЛ ИЙ СССР 1983.ЕНИЯ СИС бла осится едназнак ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ(54) УСТРОЙСТВО ДЛЯТЕМ ЛОГИЧЕСКИХ ФУНКЦ(57) Изобретение отвычислительной техн чено для реализаьгли систем логических функций. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит ш матриц памяти, два дешифратора, ш групп элементов ИЛИ и ш коммутаторов, две группы информационных входов, ш выходов. При подаче переменных х х на первую группу входов и переменных х, , х на вторую группу входов на выходах устройства реализуются логические функции Е, Г, от и переменных, 2 ил.20 25 30 35 40 45 50 55 Изобретение относится к вычислительной технике и предназначено дляреализации систем логических функций,описывающих работу цифровых преобразователей.Цель изобретения - повьппение быст -родействия устройства для вычисления систем логических функций,На Фиг.1 приведена структурнаясхема предлагаемого устройства; нафиг.2 - функциональная схема устройства для рассматриваемого примера,Устройство содержит первую 1 ивторую 2 группы информационньк входов, щ (по числу реализуемых устройством логических функций) выходов 3 -3, первый 4 и второй 5 дешифраторы, щ матриц памяти 6, - 6,щ групп элементов ИЛИ 7, - 7 и щкоммутаторов 8, - 8 и.Первая 1 и вторая 2 группы информационньк входов устройства соединены с входами первого 4 и второго5 дешифраторов соответственно. Выходы первого дешифратора 4 соединены с адресными шинами матриц памяти6 - 6, выходы которых соединеныс информационными входами коммутаторов 8 - 8, соответственно. Выходывторого дешифратора 5 соединены свходами элементов ИЛИ 7 - 7 выходыкоторк соединены с управляющимивходами коммутаторов 8 - 8, соответственно. Выходы коммутаторов 8 - 8являются выходами устройства 3 - 3,Устройство работает следующимобразом,Система щ логических функций ипеременных Г(хх), 1=1,щ разлагается по Шенному по к (к Си) переменным х х на функции и-к переменных ч (х,х,) . Таким образом,иКкаждой функции й, соответствует 2Функций Й функции Й размещаются в памяти так, что каждая из них занимает одно слово (строку) в д - й матрице памяти. Очевидно, одноименным разрядам Б (3=1,2" ") функций 4 П (х , хк) (3 = 1,2) будут соответствоватьбулевы функции .Д х , х ), каждая из которых занимает Б-й столбец в -й матрице памяти. Следовательно, переменные х, ,х определяют Функцию Ф;и в 1-й матрице, а переменные х, х, - значение выбранной функции Ч;р, которое совпадает со значением функции Г;(хх,) на данном наборе переменныхЕсли переменные х х подать на первый дешифратор, выход которого подключить к адресным шинам матриц памяти, переменные х ,х подать на второй дешифратор, выход которого подключить к управляющим входам коммутаторов, информационные входы которых соединить соответственно с выходами матриц памяти, то на выходе коммутаторов реализовываются функции Г,(хх,) . Однако, с целью уменьшения аппа -ратурных затрат все попарно тождественные эункции Ч, = (8 = 1,2" ",1,2" ", БФ 1), которым соответствуют сигналы на 8:м и 1=м вькодахвторого дешифратора, размещаются впамяти так, чтобы они занимали одинстолбец. Тогда соответствующий управляющий вход коммутатора подключается к выходу элемента ИЛИ, входыкоторого соединяются с Б:м и 1=м выходами второго дешифратора.Более подробная работа предлагаемого устройства рассмотрена на примере реализации системы трех булевых функций пяти переменных (табл.1),а функциональная схема устройствадля рассматриваемого примера приведена на Фиг.2,Разложим й (ххп) по к=2 переменным (таб,л,2).Очевидно,.1 м: Ч,=Чщ = Г (х,хп);Чщ Е 2 (хх п)115 17 ф 1(х 1хп) ь116 3 (х 1 хп) ф Следовательно, функции Чф, Ф, 1; размещаются в одном столбце первой матрицы памяти бь, выход которого подключается к информационному входу коммутатора 8, соответствующий управляющий вход которого подключен к выходу элемента ИЛИ группы 7 , входы которого соединены с первым, вторым и восьмым выходами второго дешифратора 5.Функции 1 ь и , Ф,п и Ч, также занимают по одному столбцу в матрице памяти 6, . Соответствующие управляющие входы коммутатора 8 также соединяются с выходами элементов ИЛИ группы 7Поскольку функция Ф, не имеет тождественной Функпии, то соответствую1264160 О О щий ей управляющий вход коммутатора 8 непосредственно соединен с шестым выходом второго дешифратора 5. Логические функции 2 и 15 Реалиэуются аналогично. Таким образом, при подаче переменных х х на входы 1 первого дешифратора 4 и переменных х, , х на входы 2 второго 5 дешифратора на выходах 3, - З,устройства реализуются логические функции- соответственно. Таблица 1х12 Ь 41 ЬО Та блица 2 2 0 1 1 О оо 2 3 О 4 О 20 25 Формула изобретения Устройство для вычисления систем логических функций, содержащее первый и второй дешифраторы, щ групп элементов ИЛИ (щ - количество реализующих устройством логических функций), щ коммутаторов и щ блоков памяти, выходы каждого -го (.=1,щ) блока памяти соединены с информационными входами 1-го коммутатора, выход которого является 1-м выходом устройства, первая группа информационных входов которого соединена со входами первого дешифратора, вторая группа информационных входовустройства соединена со входами второго дешифратора, о т л и ч а ю -щ е е с я тем, что, с целью повышения быстродействия, выходы первого дешифратора соединены с адресными входами щ блоков памяти, выходывторого дешифратора соединенысо входами элементов ИЛИ группс первой по п -ю выходы элементов ИЛИ -й группы соединеныс управляющими входами- гс коммутатора,1264 60 Редактор Т. Митей 671комитета ССС Заказ 5562/48 Тираж ВНИИПИ Государственного по делам изобретений 113035, Москва, Ж, Радписн и открыти шская наб д. 4 Производственно-полиграфичес

СмотретьЗаявка

3875275, 26.03.1985

МИНСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

АВГУЛЬ ЛЕОНИД БОЛЕСЛАВОВИЧ, БЕНКЕВИЧ ВИКТОР ИОСИФОВИЧ, МИЩЕНКО ВАЛЕНТИН АЛЕКСАНДРОВИЧ, КРИНИЦКИЙ АЛЕКСЕЙ ПЕТРОВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: вычисления, логических, систем, функций

Опубликовано: 15.10.1986

Код ссылки

<a href="https://patents.su/5-1264160-ustrojjstvo-dlya-vychisleniya-sistem-logicheskikh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления систем логических функций</a>

Предыдущий патент: Устройство для подготовки данных

Следующий патент: Многофункциональный логический модуль

Случайный патент: Способ выделения нафталина и антрацена из содержащих их фракций каменноугольной смолы