Декодер цепного кода

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

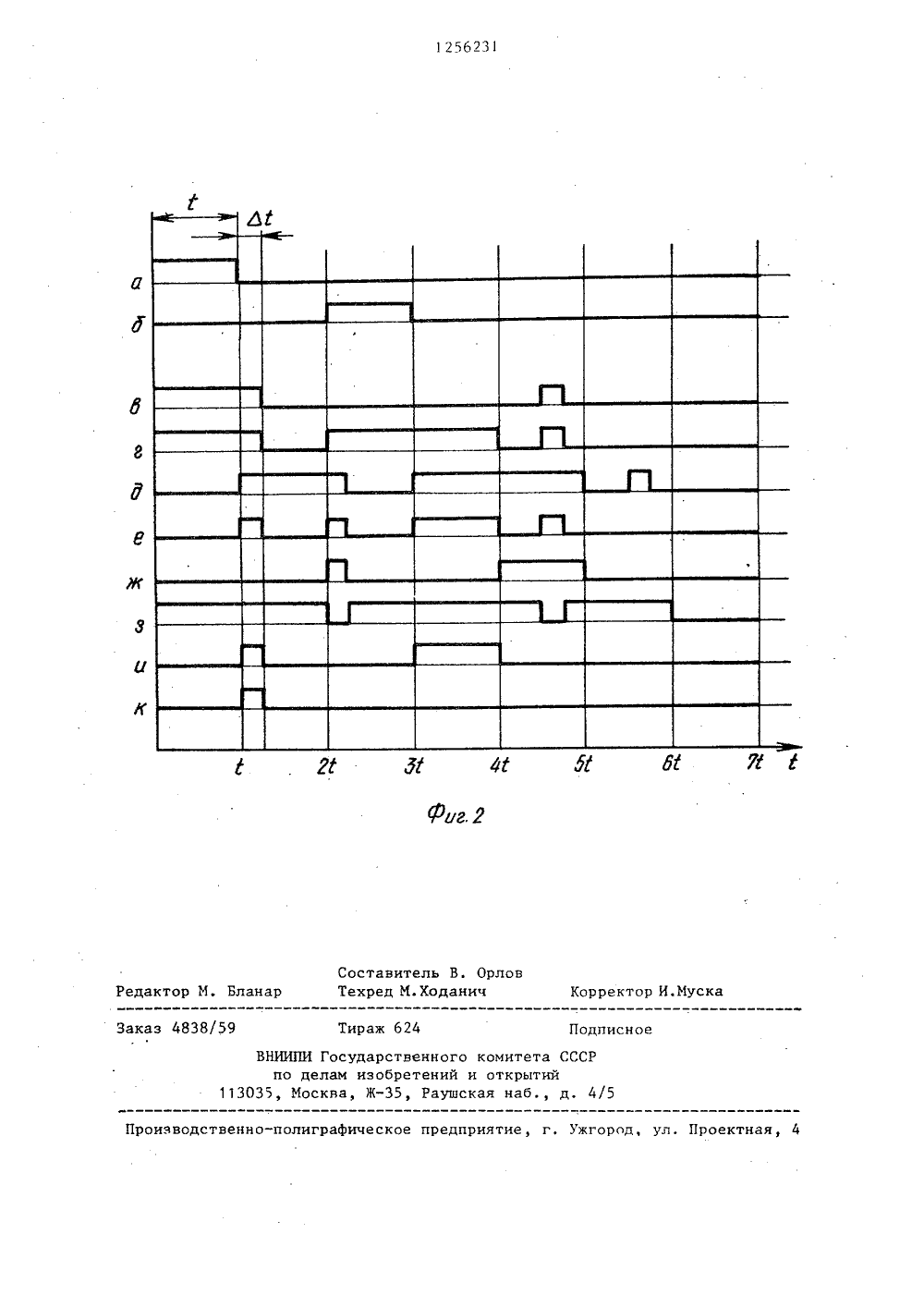

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНРЕСПУБЛИК 19) (И) ИТЕТ СССРЙ И ОТНРЫТИЙ ГОСУДАРСТВЕННЫЙ ПО ДЕЛАН ИЗОБРЕТ ЕНИЯ(21) 3880937 (22) 05.04,8 (46) 07.09.8 (72) И.И.Бул (53) 621.394 (56) Авторск Н 1 5108031 клШпяпоберс передачи дис Связь,. 1973,/г 33) гаков и .14 (088 ое свиде ельство 17/30, Основы ообщени рис. 6. Н 041кий В.И.кретных сс. 372,ехник ,-М,: 8 б. ошиб забл верт ем Р тора ОПИСАНИЕ ИЗОБР К АВТОРСКОМУ СВИДЕТЕЛЬСТ(54) ДЕКОДЕР ЦЕПНОГО КОДА(57) Изобретение относится к электросвязи. Повышается достоверность декодирования. Декодер содержит (31+1)разрядный регистр сдвига (РС) 1, два1-разрядных РС 2 и 3, два сумматорапо модулю два (С) 4 и 5, три элемента И 6, 7 и 8 и инвертор 9. При ошибках в информац. последовательности(511 4 Н 04 1 17/30 Н 03 М 13/О символов срабатывает элемент И 6 и на его выходе появляется сигнал ошибки - логическая н 1", который через открытый элемент И 8 поступает на информац. вход РС 3 и на один вход С 5. Это вызовет инвертирование искаженного информац. символа, поступающего на другой вход С 5 с выхода РС 1. Т. об., происходит исправление ошибок в информац. последовательности символов. При поступлении проверочных символов, содержащих ошибки, сигнал ошибок на выходе элемента И 6 не вызовет инвертирования выходного сигнала С 5 и тем самым не внесеток в информацию, так как будетокирован сигналом с выхода инора 9. Цель достигается введениС 3, элементов И 7 и 8 и инвер 9. 2 ил.12562Изобретение относится к электросвязи и может использоваться в системах передачи данных для повышениядостоверности декодирования,Цель изобретения - повышение достоверности декодирования.На фиг. 1 представлена структурная электрическая схема декодерацепного кода; на Фиг. 2 - временные диаграммы, поясняющие рабату1 Оустройства.Декодер содержит (3 + 1) разрядныйрегистр 1 сдвига, й -разрядный регистр 2 сдвига, дополнительный ь -разрядный регистр 3 сдвига, первый 15и второй сумматоры 4 и 5 .по модулюдва, элемент И 6, первый и второйдополнительные элементы И 1 и 8,инвертор.Декодер цепного кода работает .2 Оследующим образом.Информационные символы поступаютна информационный вход (3+1)-Разрядного регистра 1 и по мере поступле,гния продвигаются по его разрядам.Выходные сигналы (2(+1) и (.Я+1) -разрядов (31+1) -разрядного регистра 1 суммируются в первомсумматоре 4 с проверочными символами, поступающими на третий ЗО.вход первого сумматора 4, Причемсуммирование по модулю два.:выходныхсигналов (21+1) и (31+1) разрядов(31+1) -разрядного регистра 1,цает врезультате вспомогательную последовательность проверочных символов,которая сравнивается с последовательностью проверочных символов, поступающих на проверочный вход декодерацепного кода для определения наличия Ои характера распределения ошибок вовходных сигналах. При отсутствииошибок в информационной и проверочной последовательностях символов,на выходе первого сумматора 4 присутствуют нули на каждом такте срабатывания декодера цепного кода. Еслиже входные сигналы содержат ошибки,то на выходе первого сумматора 4появляются единицы, соответствующепринятым с ошибками информационнымили проверочным символам. При этомсИгналы ошибки (единицы) на выходепервого сумматора ч, соответствующиеошибкам в принятых проверочных символах, появляются одновременно споступлением на проверочный вход декодера цепного кода. каждого принято 31 2го с ошибкой проверочного символаПри искажении информационного символа на выходе первого сумматора 4возникают два сигнала ошибки, причемпервый - с задержкой на 2+1 тактов,а второй - с задержкой на 31+1 тактов относительно момента поступленияна информационный вход декодера цепного кода искаженного информационно-,га символа,Сигналы ошибок, появляющиеся навыходе первого сумматора 4, поступа"ют на первый и второй входы элементаИ 6, причем на второй вход непосредственно, а на первый вход через и -разрядный регистр 2 с задержкой натактов срабатывания декодера цепного кода. Таким образом, при ошибках в информационных символах к моменту появления на выходе первого,сумматора 4 второго сигнала ошибки,а на выходе. (31+1) разряда (31+1) -разрядного регистра 1 искаженного инФормационного символа, на выходе 1 -разрядного регистра 2 появляется зацержанный на 1 тактов первый сигналошибки. При этом срабатывает элементИ 6 и на его выходе появляется сигнал ошибки - логическая "1", которыйчерез открытый второй дополнительныйэлемент И 8 поступает на информационный вход дополнительного 1 -разрядного регистра 3 и на второй вход второго сумматора 5 и вызывает инвертирование (т.е. исправление) искаженного информационного символа, поступающего на первый вход второго сумматора 5 с выхода (31+1) разряда (31++1) -разрядного регистра 1. Так происходит исправление ошибок в информационной последовательности символов.Декодер цепного кода позволяетисправлять пакеты ошибок в информационных символах длиной 1 символовипи лемьше при условии, что междупакетами ошибок расположено не менее ю, правильно принятых символов(с 4 - защитный интервал). При этомзап,"итный интервал для информационныхсимволов составляет к = 2 символов,а для проверочных символов - м = Зс .Следовательно, ошибка, которая неискажает правильно принятую информацию и может быть исправлена, можетпоявляться в соответствующих последовательностях символов только черезопределенный интервал относительно1256 40 последней ошибки в предыдущем пакете ошибок. Если на информационный и проверочный входы декодера цепного кода поступают последовательности информационных и проверочных симво лов, пораженных пакетами ошибок, величины которых не превьппают исправляющую способность декодера, то ошибки в информационных символах исправляются по алгоритму, описанному, а ошибки в проверочных символах не устраняются. При этом все сигналы ошибок, возникающие на выходе первого сумматора 4 и вызванные искаженными проверочными символами, через 21 так тов работы декодера цепного кода поступают в 1 -разрядный регистр 2 и покидают его, не оказывая влияния на выходную информационную последовательность символов.Пусть на декодер цепного кода поступают такие последовательности информационных и проверочных символов, ито информационные символы содержат пакет ошибок длины(фиг. 2 а) 2 а проверочные - содержат пакет ошибок длины 1 + ь (фиг. 2 в). Для упроще-. ния построения временных диаграмм работы декодера цепного кода (фиг. 2) приняты следующие условия: по каналу 30 связи передается длительный "О"; ошибки, возникающие из-за помех в канале связи, приводят к появлению "1"; учитывая, что информационные и проверочные символы, передаваемые по каналу связи, чередуются, величина интервала, занимаемого пакетом ошибок (в канале связи), равна 2+В, где п сТаким образом, пакет ошибок в информационных символах не превьппает исправляющей способности декодера цепного кода и может быть исправлен, а пакет ошибок в проверочных символах превьппает исправляющую способ ность декодера цепного кода на ь 1 символов.Рассматривают работу декодера цепного кода в этом случае. В исходном состоянии, до момента поступления на 50 декодер цепного кода входных сигналов с ошибками (31+1)-разрядный регистр 1, 1-разрядный регистр 2 и дополнительный 1 -разрядный регистр 3 находятся в нулевом состоянии. Сле довательно, на выходах первого 4 и второго 5 сумматоров, а также на выходах элемента И 6, дополнительных 231 4первого 7 и второго 8 элементов И также присутствуют нули.При наличии ошибок во входных последовательностях символов на выходе первого сумматора 4 одновременно с поступлением на проверочный вход декодера цепного кода искаженных проверочных символов (фиг. 2 в) появляются сигналы ошибок (фиг. 2 а) и через 1 тактов работы декодера цепного кода в 1 -разрядном регистре 2 записано 1 сигналов ошибок, а в (31+ +1) -разрядном регистре 1 находятся 1 искаженных информационных символов (фиг. 2 а). Далее на+1 такте работы декодера цепного кода на выходе дополнительного 1 -разрядного регистра 3 появится 1 +1 сигнал ошибки (фиг. 2 г) и одновременно с ним на выходе 1 -разрядного регистра 2 появится первый сигнал ошибки (фиг. 2 д). Одновременное появление двух сигналов приводит к появлению на выходе элемента И 6 сигнала ошибки (фиг. 2 е), который, поступая через открытый второй дополнительный, элемент И 8 на информационный вход 1 -разрядного регистра 3 и на вход второго сумматора 5 (фиг. 2 и), записан в 1 -разрядный регистр 3 и вызывает инвертирование (т,е, вносит ошибку) информационного символа на. выходе второго сумматора 5 (фиг. 2 к).На протяжении ь 1 -1 тактов работы декодера цепного кода также вносятся ошибки в выходную информационную последовательность (фип. 2 к). При последующих 1 -Ь 1 тактах работы декодера цепного кода ошибок в выходной информационной последовательностинет. К этому моменту проходит 21 тактов работы декодера цепного кода и искаженные информационные символы расположены с И+1) по 21 ,разрядах (31+1)-разрядного регистра 1, в 1 -разрядном регистре 2 и в, дополнительном 1 -разрядном регистре3 расположены с И- Й) по 6 -1) разрядах д 1 символов ошибок, вызванных искаженными проверочными символами.Далее на 21 +1 такте работы декодера цепного кода на выходе первого суматора 4 появляется первый сигнал ошибки информационных символов (фиг. 2 д), задержанный на 21+1 тактов (Фиг. 2 б) относительно момента появления на входе декодера цепного3 1256 кода (Фиг. 2 а). Одновременно с этим сигналом появляются сигналы ошибки и на выходах-разрядного 2 и дополнительного 1 - разрядного 3 регистров (фиг. 2 д, ж). Однако при этом срабатывают первый дополнительный элемент И 7 и инвертор 9, который своим выходным сигналом (Фиг. 2 и) закрывает второй дополнительный элемент И .8, исключив тем самым прохождение 1 О сигнала ошибки с выхода элемента И 6 (Фиг. 2 е) на вход второго сумматора 5 и на вход дополнительного- разрядного регистра 3 (Фиг, 2 и). В этом случае инвертирования информационного символа на выхоце сумматора 5 (фиг. 2 к) не происходит, т.е. не внесена ошибка в правильно принятые информационные символы.На протяжении Ь 1 -1 тактов работы декодера цепного кода блокирование сигналов ошибок, появляющихся на выходе элемента И 6, производится аналогично. По прошествии 21+ Й тактов работы декодера цепного кода 25 1 "разрядный регистр 2 находится в нулевом состоянии (Фиг.2 ж), с второго дополнительного элемента И 8 снимается сигнал блокировки (Фиг. 2 з), После 31 такта работы декодера цепного кода в-разрядном регистре 2 записаносигналов ошибок, вызванных искаженными информационными символами. Далее с 31+1 по 4 т такты работы декодера цепного кода производится35 исправление информационных символов, содержащих пакет ошибок длиной 1 символов, аналогично описанному.Пусть в интервале между 41+1 и 5 тактами работы декодера цепного кода поступают проверочные символы, содержащие ошибки (фиг. 2 в). Эти искаженные проверочные символы вызывают появление на выходе первого сумматора 4 сигнала ошибки (Фиг. 2 г). Одновре менно и этим на выходе 1 -разрядного регистра 2 появляются сигналы ошибок информационных символов, задержанные относительно момента появления на 231 Ьвыходе первого сумматора 4 (Фиг, 2 г) на 1 тактов (Фиг. 2 д). Эти два сигнала вызывают появление на выходе элемента И 6 сигнала ошибок (Фиг, 2 е). Однако этот сигнал ошибки не вызывает инвертирование выходного сигнала второго сумматора 5 и тем самым не вносит ошибок в информацию, так как заблокирован сигналом с выхода инвертора 9 (Фиг. 2 з).Ф о р м у л а изобретенияДекодер цепного кода, содержащий последовательно соединенные (31+1) - разрядный регистр сдвига, первый сумматор по модулю два, 1 -разрядный регистр сдвига и элемент И, а также второй сумматор по модулю два, первый вход которого подключен к выходу (31+1)-го разряда, (31+1)-ра.зрядного регистра сдвига, выход (21+1)-го разряда которого подсоединен к второму входу первого сумматора по модулю два, второй вход элемента И подключен к выходу первого сумматора по модулю два, причем информационный .вход (31+1)-разрядного регистра и третий вход первого сумматора по модулю два являются соответственно информационным и проверочным входами декодера, а выход второго сумматора по модулю два является выходом декодера, о т л и ч а ю щ и й с я тем, что, с целью повышения достоверности декодирования, в него введены последовательно соединенные дополнительный А -разрядный регистр сдвига, первый дополнительный элемент И, инвертор и второй доплнительный элемент И, при этом выход второго дополнительного элемента И подсоединен к второму входу второго сумматора по модулю два и информационному входу дополни тельного г -разрядного регистра сдвига, а выход элемента И подсоединен к вторым . входам первого и второго дополнительных элементов И.1256231 Орлович Корректор И.Муск актор М. Бланар Подписно Заказ 4838 5 Тираж б ВНИИПИ Государственного комит по делам изобретений и откр3035, Москва, Ж, Раушская на роизводственно-полиграфическое предприятие ектная, 4 город,Составител Техред М.Х ета СССРтийб д. 4/

СмотретьЗаявка

3880937, 05.04.1985

ПРЕДПРИЯТИЕ ПЯ Р-6886

БУЛГАКОВ ИГОРЬ ИОСИФОВИЧ, ЛАЗИНЦЕВ КОНСТАНТИН ДМИТРИЕВИЧ

МПК / Метки

МПК: H03M 13/51, H04L 17/30

Опубликовано: 07.09.1986

Код ссылки

<a href="https://patents.su/5-1256231-dekoder-cepnogo-koda.html" target="_blank" rel="follow" title="База патентов СССР">Декодер цепного кода</a>

Предыдущий патент: Устройство для приема биимпульсных сигналов

Следующий патент: Приемник рекуррентных последовательностей

Случайный патент: Способ получепия дихлорапгидридов алкилтиовинилфосфоповых кислот