Цифровой интегратор для решения краевых задач

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1211712

Автор: Ледовской

Текст

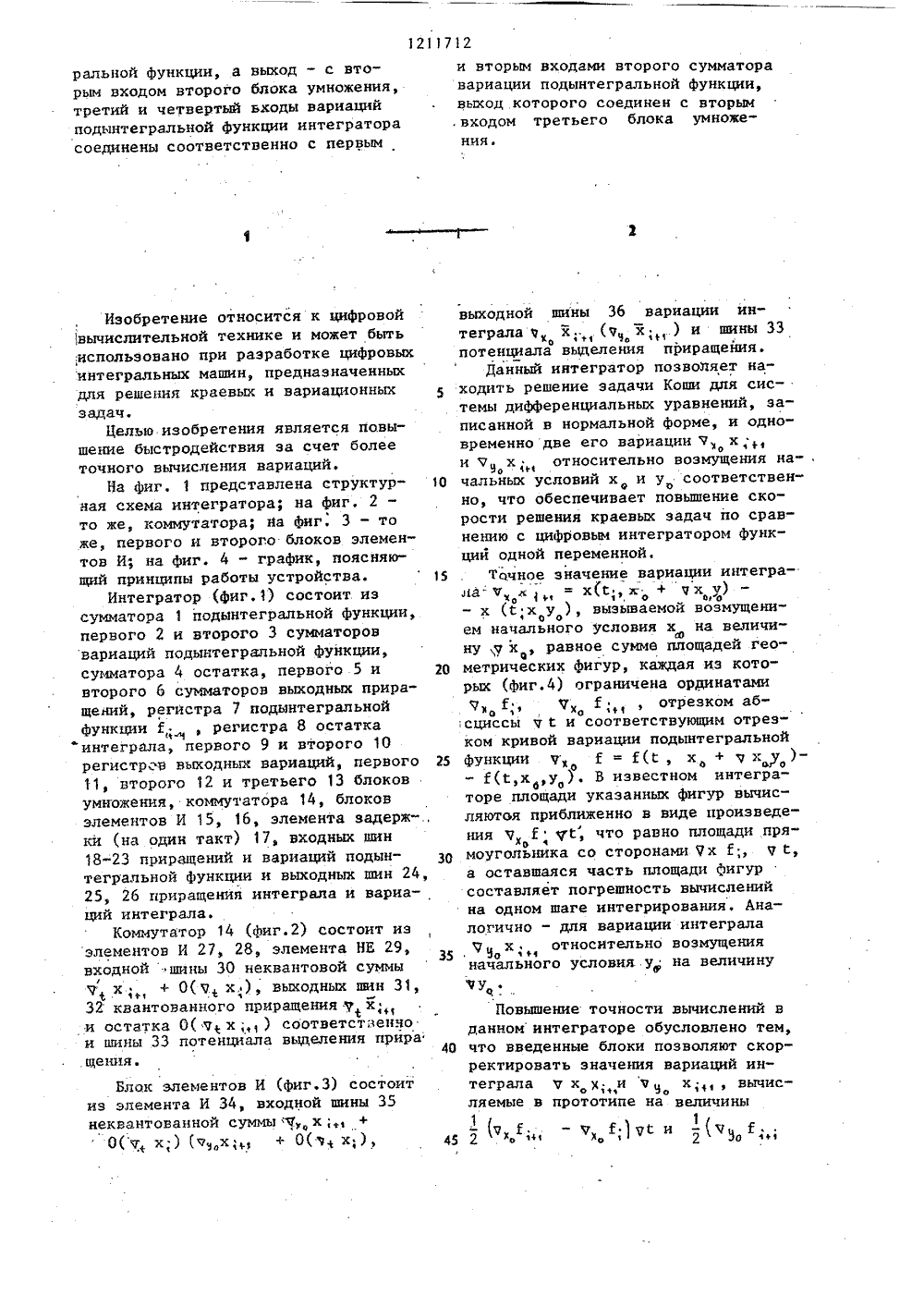

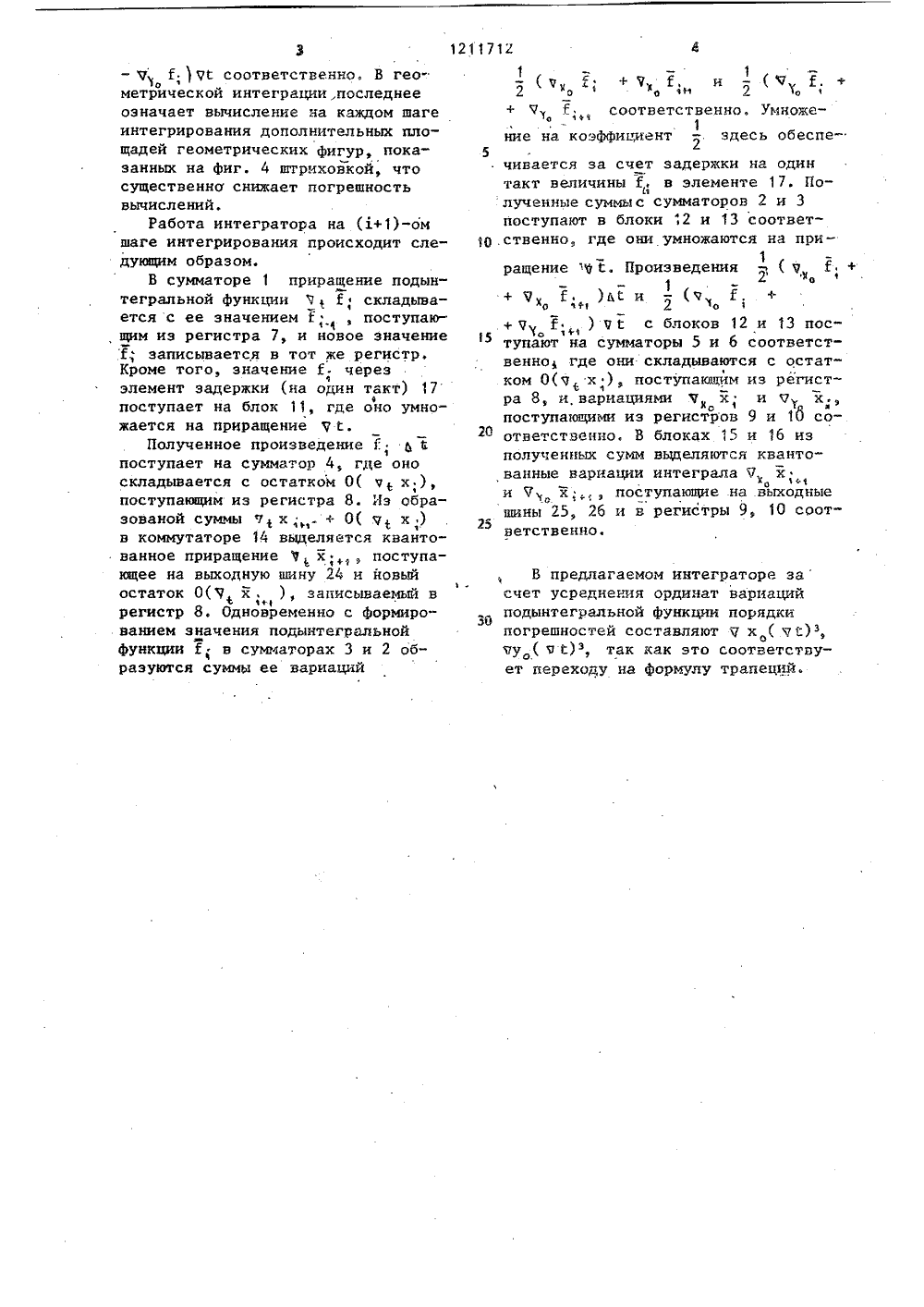

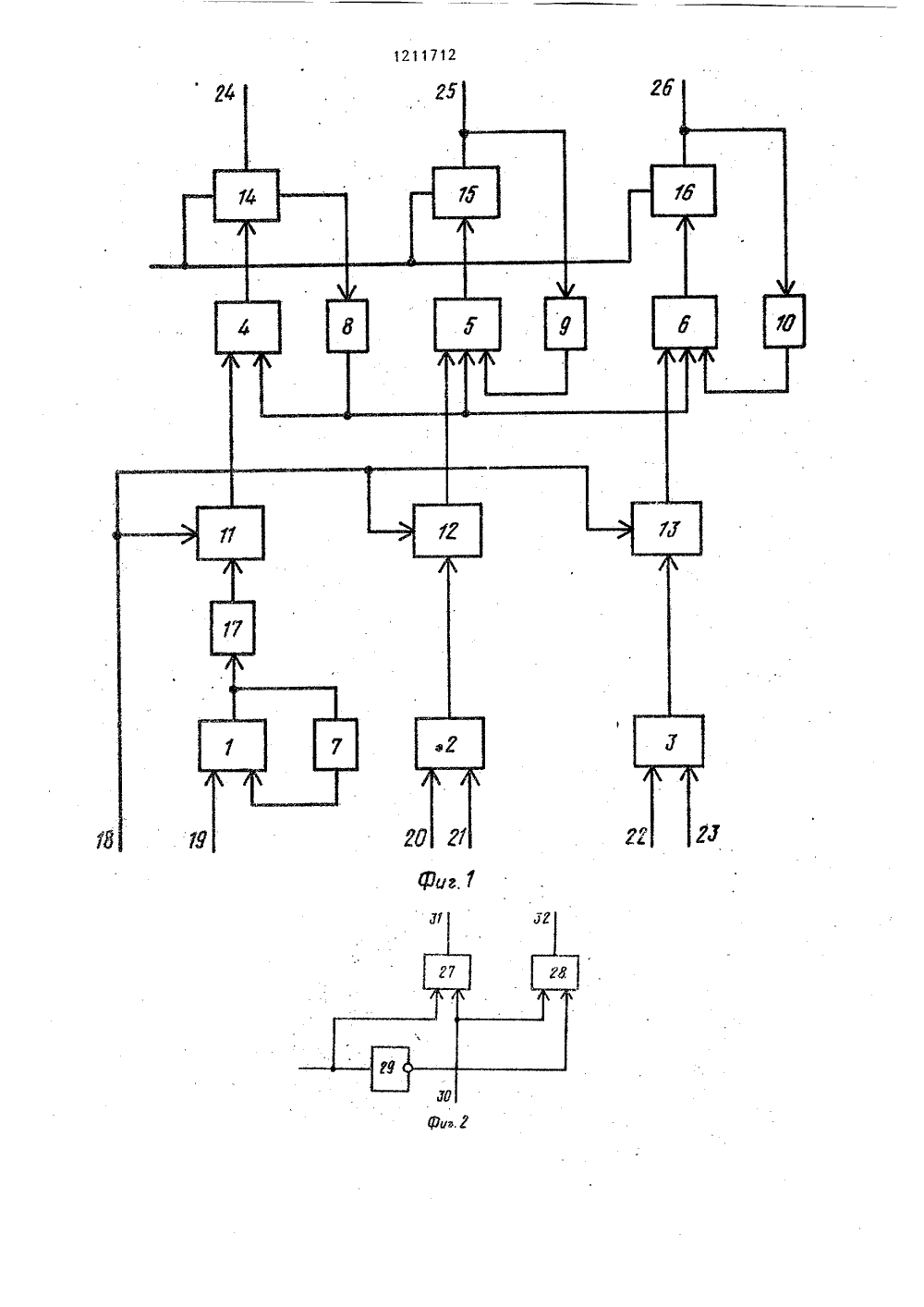

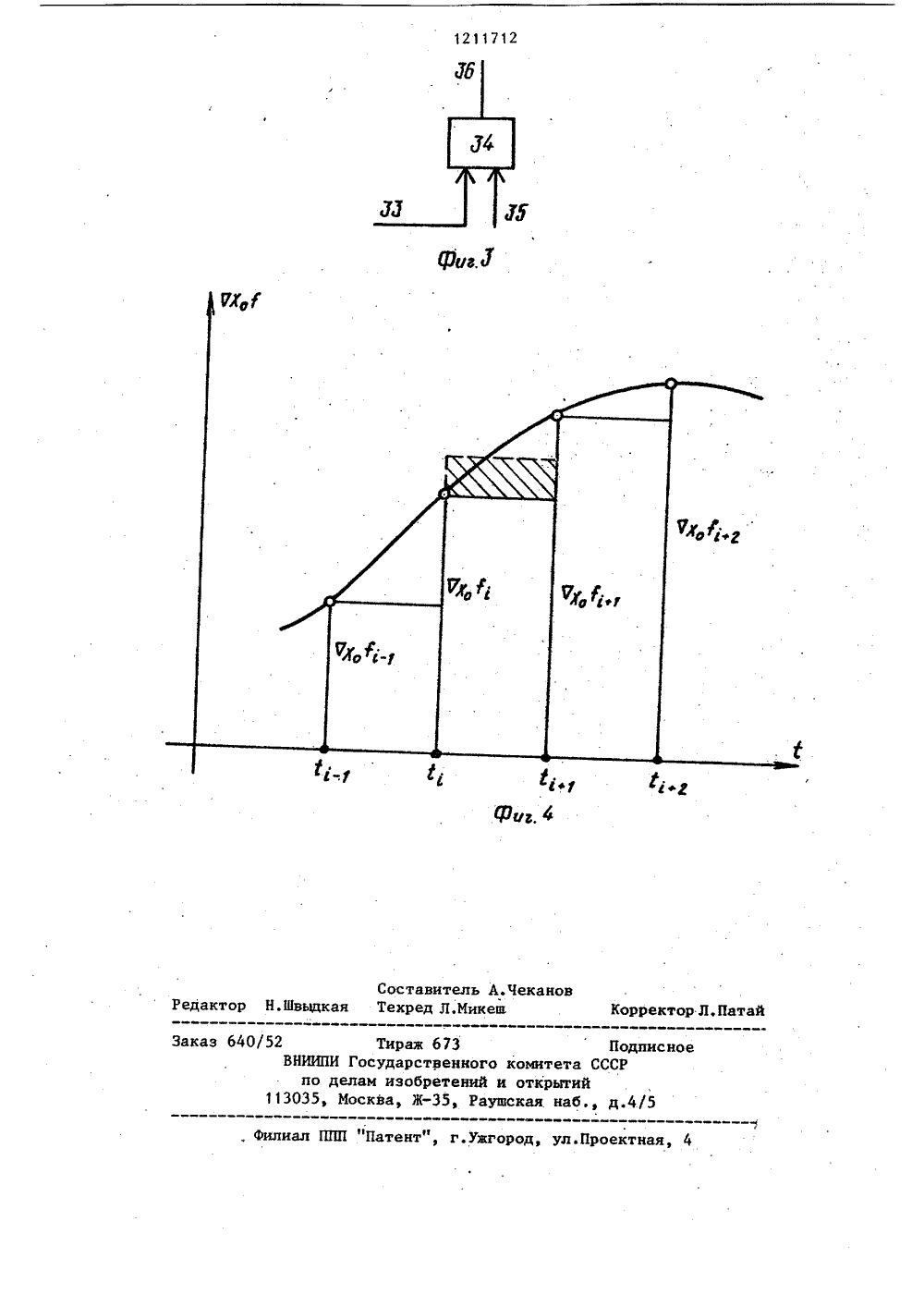

(71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) М.И.Ледовской(56) Авторское свидетельство СССР В 328482, кл. С ОЬ Г 7/64, 1972.Авторское свидетельство СССР У 568060, кл. С 06 Г 7/64, 1977.д(54) (57) ЦИФРОВОЙ ИНТЕГРАТОР ДЛЯ РЕШЕНИЯ КРАЕВЫХ ЗАДАЧ, содержащий сумматор подынтегральной функции, регистр подынтегральной функции, три блока умножения, сумматор остатка интеграла, регистр остатка интеграла, два сумматора выходных приращений, два регистра выходных вариаций, ком.мутатор и два блока элементов И, причем вход приращения подынтегральной Функции интегратора соединен с первым входом сумматора подынтегральной функции, второй вход которого подключен к выходу регистра подынтегральной функции, информационный вход которого соединен с выходом сумматоуа подынтегральной функции, вход приращения времени интегратора подключен к первым входам первого, второго и третьего блоков умножения, выход первого блока умножения соединен с первым входом сумматора остатка интеграла, выход которого соединен .с информационным входом коммутатора, первый выход которого соединен с выходом приращения интеграла интегратора, а второй - с информационным входом регистра остатка интеграла, выход которого соединен с вторым входом сумматора остатка интеграла и первыми входами первого и второго сумматоров выходных приращений, выход второго блока умножения соединен с вторым входом первого сумматора выходных приращений выход которого соединен с первым входом первого блока элементов И, выход которого соединен с выходом первой вариации интеграла интегратора и информационным входом первого регистра выходных вариаций, выход которого соединен с третьим входом первого сумматора выходных приращений, выход третьего блока умножения соединен с вторым входом второго сумматора выходных приращений, выход которого соединен с первым входом второго блока элементов И, выход которого подключен к выходу второй вариации интеграла интегратора и информационному входу второго регистра выходных вариаций, выход которого соединен с третьим входом второго сумматора вы,ходных приращений, вход управления выделением приращений интегратора подключен к управляющему входу коммутатора и. вторым входам первого и второго блоков элементов И, о т л и ч а ю щ и й с я тем; что, с целью повьпаення быстродействия за счет более точного вычисления вариаций, он содержит элемент задержки .и два сумматора вариации подынтегральной функции, выход сумматора подынтегральной функции через элемент задержки соединен с вторым входом первого блока умножения, первый и второй входы первого сумматора вариации подынтегральной функции соединены соответственно с первым и вторым входами вариаций подынтег ральной функции, а выход - с вторым входом второго блока умножения,третий и четвертый входы вариацийподынтегральной функции интеграторасоединены соответственно с первым 1211712и вторым входами второго сумматора вариации подынтегральной функции, выход которого соединен с вторым .входом третьего блока умножения.20 Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке цифровых интегральных машин, предназначенных для решения краевых и вариационных э адачЦелью изобретения является повышение быстродействия за счет более точного вычисления вариаций.На фиг. 1 представлена структур О ная схема интегратора; на Фиг. 2 - то же, коммутатора; на Фиг. 3 - то же, первого и второго блоков элементов И", на Фиг. 4 - график, поясняющий принципы работы устройства.15Интегратор (фиг.1) состоит из сумматора 1 падынтегральной Функции, первого 2 и второго 3 сумматоров вариаций подынтегральной Функции, сумматора 4 остатка, первого 5 и второго 6 сумматоров выходных приращений, регистра 7 подынтегральной функции Е, , регистра 8 остатка интеграла, первого 9 и второго 10 регистр В выходных вариаций, первого 25 11, второго 12 и третьего 13 блоков умножения, коммутатора 14, блоков элементов И 15, 16, элемента задерж-, ки (на один такт) 17, входных шин 18-23 приращений и вариаций подын- ЗО тегральной функции и выходных шин 24, 25, 26 приращения интеграла и вариаций интеграла.Коммутатор 14 (фиг.2) сОстоит из элементов И 27, 28, элемента НЕ 29, входной шины 30 неквантовой суммы Ч х + О( Чь х )ВыхОДных нын 31 р 32 квантованного приращения .Ч х; и остатка О( Чх; ) соответстленчо и шины 33 потенциала выделения прира щенияе Блок элементов И (Фиг,3) состоитиз элемента И 34, входной шины 35неквантованной суммы М,х;+, +О( ч х) (ч х+ + 0(ъ х), 45 выходной шины 36 вариации интеграла ч х (Р х; ) и шивы 33 потенциала выцеления приращения.данный интегратор позволяет находить решение задачи Коши для системы дифференциальных уравнений, записанной в нормальной форме, и одновременно две его вариации ч х;, и Ч х;, относительно возмущения на 9 нчальных условий х и у соответствена ьно, что обеспечивает повышение скорости решения краевых задач по сравнению с цифровым интегратором функции одной переменной.тсчное значение вариации интегралач 1 = х(с,к + чх у)о ф ф, о оо - х (с;х у ), вызываемой возмущением начального условия х на величину ,ч х , равное сумме площадей геоофметрических фигур, каждая из которых (фиг.4) ограничена ординатамифЧф, , отрезком аб;сциссы ч с и соответствующим отрезком кривой вариации подынтегральной функции ч Г = й(с, х, + ч х у )- - Г(с,х,у). В известном интеграторе площади указанных фигур вычисляютья приближенно в виде произведения Ч Г С, что равно площади пряХфмоугольника со сторонами Чх 2;, Ч С, а оставшаяся часть площади фигур составляет погрешность вычислений на одном шаге интегрирования, Аналогично - для вариации интеграла Ч х . относительно возмущенияО фф 1начального условия у на величину ЪУПовышение точности вычислений вданноминтеграторе обусловлено тем,что введенные блоки позволяют скорректировать значения вариаций интеграла ч х,х;,и ч х;, вычисляемые в прототипе на величиныЧй ЧС и -(ЧГ3- 9 Г;)ЧС соответственно. В гео" метрической интеграции, последнее означает вычисление на каждом шаге интегрирования дополнительных площадей геометрических Фигур, показанных на Фиг. 4 штриховкой, что существенно снижает погрешность вычислений.Работа интегратора на (+1)-ом шаге интегрирования происходит следующим образом.В сумматоре 1 приращение подынтегральной ФункцииГф складывается с ее значением й; , поступающим из регистра 7, и новое значение Г.; записывается в тот же регистр, Кроме того, значение й через элемент задержки (на один такт) 17 поступает на блок 11, где оно умножается на приращение Ч й.Полученное произведение 7 ь й1 поступает на сумматор 4, где оно складывается с остатком О( ч ь х),1 поступающим из регистра 8. Яз образованой сукины 7 х ,. + О( у х ) в коммутаторе 14 выделяется квайтованное приращение Ъх; , поступающее на выходную шину 24 и новый остаток О(9 х, ), записываемый вфрегистр 8. Одновременно с Формированием значения подынтегральной Функции Е; в сумматорах 3 и 2 образуются суммы ее вариаций 12117121(ч, + 7 Г, и - (Ч Е +оф и 2 о + Ч Гсоответственно. Умножение на коэФфициент в . здесь обеспе 25. чивается за счет задержки на одинтакт величины Е в элементе 17. Полученные суммыс сумматоров 2 и 3поступают в блоки ",2 и 13 соответ 1 п .ственно, где они умножаются на приЮ1ращение Ф С. Произведения , ( д Г, +Мо+7 Г , ) дс с блоков 12 и 13 пос туи на сумматоры 5 и 6 соответственно где они складываются с остат"ком 0(ч х ), поступающим из регистра 8, и, вариациями 9 х; и 7 хпоступающими из регистров 9 и 10 со 2 б ответственно, В блоках 15 и 16 изполученных сумм выделяются квантованные вариации интеграла Ч хи 7, х; , поступающие на выходныешины 25, 2 б и в регистры 9, 10 соответственно. В предлагаемом интеграторе засчет усреднения ординат вариаций подынтегральной Функции порядки погрешностей составляют Ч х ( 7 С), чу(), так как это соответствует переходу на Формулу трапеций.1211712 орректор Л. Патай 2 Тираж 673 ВНИИПИ Государственного по делам изобретений 13035, Москва, Ж, РаушЗаказ 6 исно По комитета СССР открытий ская наб., д.

СмотретьЗаявка

3764583, 02.07.1984

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ЛЕДОВСКОЙ МИХАИЛ ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/64

Метки: задач, интегратор, краевых, решения, цифровой

Опубликовано: 15.02.1986

Код ссылки

<a href="https://patents.su/5-1211712-cifrovojj-integrator-dlya-resheniya-kraevykh-zadach.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой интегратор для решения краевых задач</a>

Предыдущий патент: Устройство для питания радиоаппаратуры

Следующий патент: Устройство для программного управления

Случайный патент: Пильная цепь для резания древесины