Микропрограммное управляющее устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

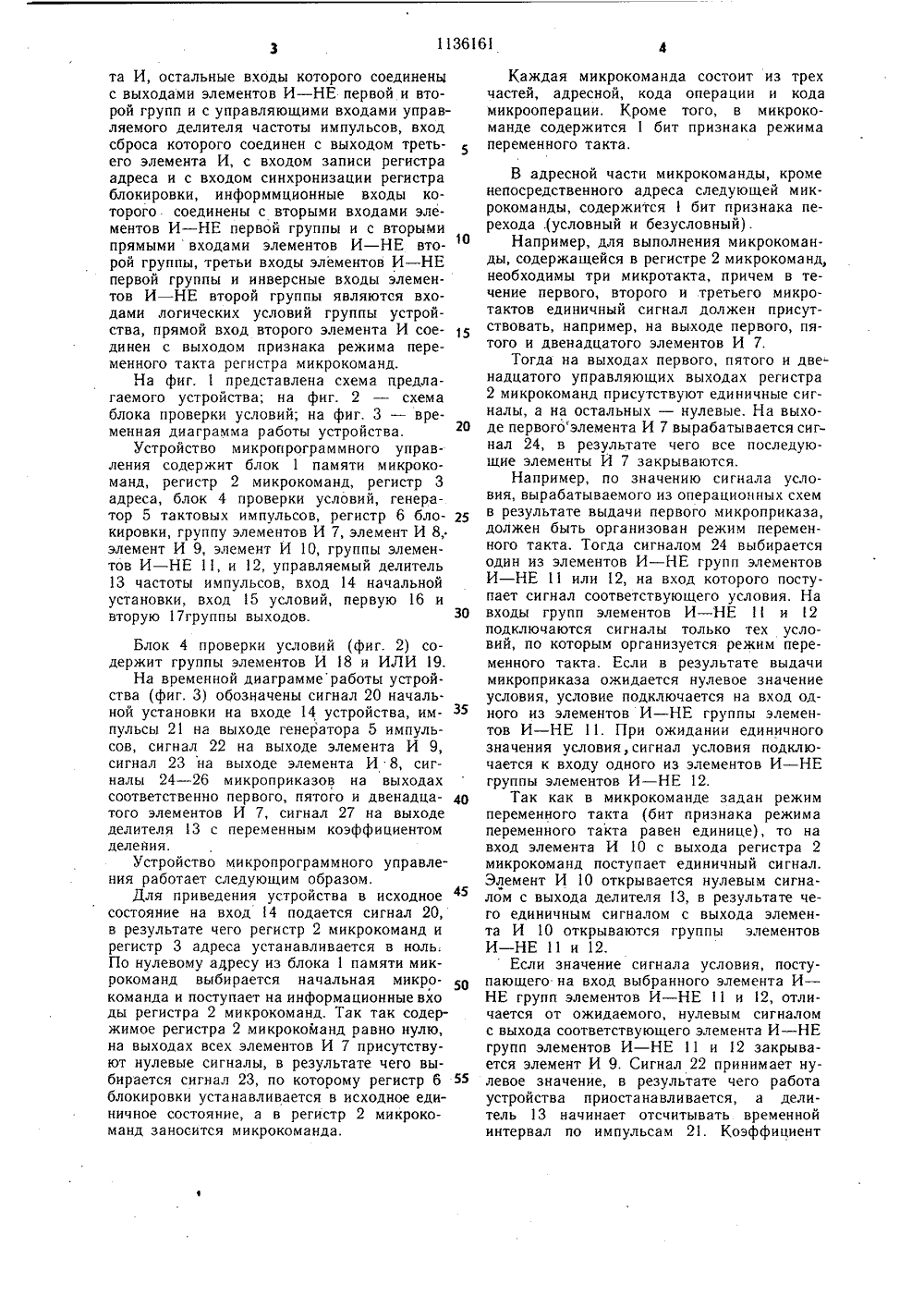

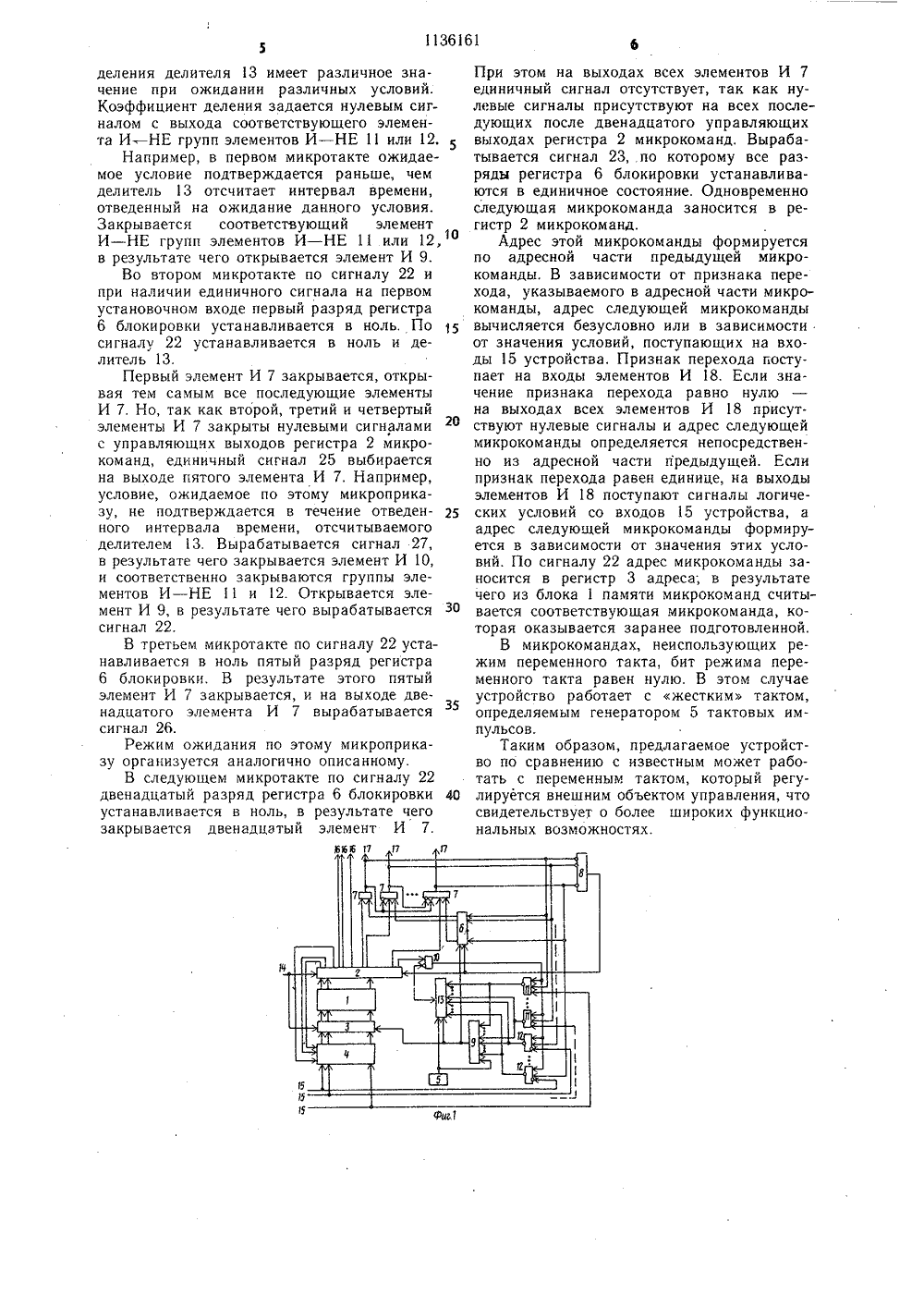

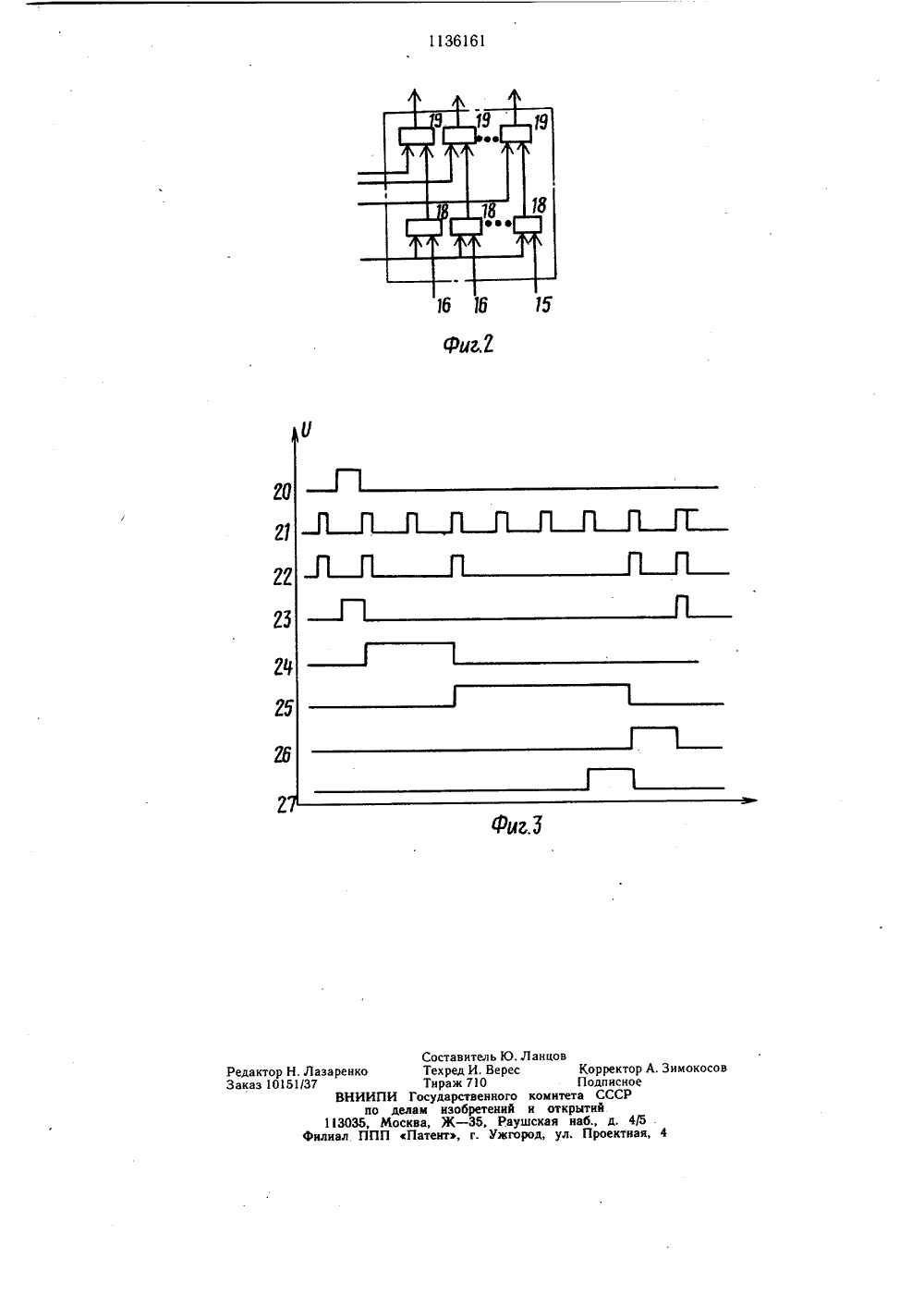

.80 1136161 453) б 06 Р 9/22 ОПИСАНИЕ ИЗОБРЕТЕНИЯ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54) (57) МИКРОПРОГРАММНОЕ УПРАВЛЯЮЩЕЕ УСТРОЙСТВО, содержащее блок памяти микрокоманд, регистр микро- команд, регистр адреса, блок проверки условий, генератор тактовых импульсов, регистр блокировки группу элементов И ,и первый элемент И, выход которого соединен с входом установки в 1 регистра блокировки и с входом записи регистра микро- команд, группа выходов кода операции которого является первой группой управляющих выходов устройства, выходы кода микро- операций регистра микрокоманд соединены с первыми прямыми входами элементов И группы, выход 1-го элемента И группы (1=1,2 (и - 1), где и - разрядность кода микроопераций), соединен с 1-м инверсным входом первого элемента И, с 1-м информационным входом регистра блокировки и с инверсными входами с (1+1)-го по и-й элементов И группы и является 1-м управляющим выходом второй группы устройства, выход п-го элемента И группы соединен с п-м инверсным входом первого элемента И, с и-м,информационным входом регистра блокировки и является и-м управляющим выходом второй группы устройства, 1- й выход (1 = - 1,2, ,и) регистра, блокировки соединен с вторым прямым входом 1-го элемента И группы, группа выходов кода адреса регистра микрокоманд соединена с первой группой входов блока проверки условий, вторая группа входов которого является группой входов логических условий устройства, группа выходов блока проверки условий соединена с группой информационных входов регистра адреса, группа выходов которого соединена с группой адресных входов блока памяти микрокоманд, группа выходов которого соединена с группой информационных входов регистра микро- команд, вход установки в ноль которого соединен с входом установки в О регистра адреса и является входом начальной установки устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем реализации переменного такта работы по логическим условиям, оно содержит второй и третий элементы И, управляемый делитель частоты импульсов и первую и вторую группы элементов И - НЕ, причем первые входы элементов И - НЕ первой группы и первые прямые входы элементов И - НЕ второй группы соединены с выходом второго элемента И, инверсный вход которого соединен с выходом управляемого делителя частоты импульсов, тактовый вход которого соединен с выходом генератора тактовых импульсов и с первым входом третьего элемента И, остальные входы которого соединены с выходами элементов И - НЕ первой и второй групп и с управляющими входами управляемого делителя частоты импульсов, вход сброса которого соединен с выходом третьего элемента И, входом записи регистра адреса и с входом синхронизации регистра блокировки, информационные входы которого соединены с вторыми входами элементов И - НЕ первой группы и вторыми прямыми входамиэлементов И - НЕ второй группы, третьи входы элементов И - НЕ первой группы и инверсные входы элементов И - НЕ второй группы являются входами логических условий группы устройства, прямой вход второго элемента И соединен с выходом признака режима переменного такта регистра микрокоманд.Изобретение относится к автоматике и вычислительной технике, в частности к микропрограммным устройствам управления, и может быть использовано в цифровых вычислительных системах, а также терминальной аппаратуре.Известно микропрограммное управляющее устройство, содержащее блок памяти микрокоманд, регистр адреса, регистр микро- команд, блок проверки условий, генератор импульсов, группу элементов И, регистр блокировки и элемент И 11).Недостатком данного устройства является низкая экономичность, обусловленная тем, что при реализации режимов ожидания в микропрограммной памяти предусматриваются холостйе микрокоманды. 5 10 15 Наиболее близким по технической сущности к предлагаемому является микропрограммное управляющее устройство, содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса, блок проверки условий, генератор тактовых импульсов, регистр блокировки, группу элементов И и первый элемент И, выход которого соединен с входом установки в единицу ре 25 гистра блокировки и с входом записи регистра микрокоманд группа выходов кода операции которого является первой группой управляющих выходов устройства; выходы кода микроолераций регистра микро- команд соединены с первыми прямыми входами элементов И группы, выход 1-го элемента И группы (1= 1,2, , (п - 1), где и - разрядность кода микроопераций) соединен с 1-м инверсным входом первого элемента И, с 1-м информационным входом регистра блокировки и с инверсными входами35 с (1+1)-го ло л-й элементов И группы и является 1-м управляющим выходом второй группы устройства, выход п-го элемента И группы соединен с л-м инверсным входом первого элемента И, с п-м информацион ным входом регистра блокировки и является и-м управляющим выходом второй группы устройства, 1-й выход (1=1, 2 л) регистра блокировки соединен с вторым прямым входом )-го элемента И группы, группа выходов кода адреса регистра микрокоманд соединена с первой группой входов блокапроверки условий, вторая группа входов которого является группой входов логических условий устройства, группа выходов блока проверки условий соединена с груп пой информационных входов регистра адреса, группа выходов которого соединена с группой адресных входов блока памяти микрокоманд, группа выходов которого соединена с группой информационных входов регистра микрокоманд, вход установкив ноль которого соединен с входом установки в ноль регистра адреса .и является входом начальной установки устройства 12. Недостатком известного устройства является невозможность реализации переменного такта работы в зависимости от условий функционирования объекта управления.Целью изобретения является расширение функциональных возможностей устройства путем реализации переменного такта работы по логическим условиям.Указанная цель достигается тем, что в микропрограммное управляющее устройство, содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса, блок проверки условий, генератор тактовых импульсов, регистр блокировки, группы элементов И и первый элемент И, выход которого соединен с входом установки в 1 регистра блокировки и с входом записи регистра микрокоманд, группа выходов кода операции которого является первой группой управляющих выходов устройства, выходы кода микроопераций регистра микро- команд соединены с первыми прямыми входами элементов И группы, выход 1-го элемента И группы (1: 1,2(п - 1), где ив разрядность кода микроопераций) соединен с 1-м инверсным входом первого элемента И, с 1-м информационным входом регистра блокировки и с инверсными входами с (1+1)-го по и-й элементов И группы и является 1-м управляющим выходом второй группы устройства, выход и-го элемента И группы соединен с п-м инверсным входом первого элемента И, с и-м информационным входом регистра блокировки и является и-м управляющим выходом второй группы устройства, 1-й выход= 1,2п) регистра блокировки соединен с вторым прямым входом )-го элемента И группы, группа выходов кода адреса регистра микрокоманд соединена с первой группой входов блока проверки условий, вторая группа входов которого является группой входов логических условий устройства, группа выходов блока проверки условий соединена с группой информационных входов регистра адреса, группа выходов которого .соединена с группой адресных входов блока памяти микрокоманд, группа выходов которого соединена с груп-. пой информационных входов регистра микрокоманд вход установки в ноль которого соединен с входом установки в 0 регистра адреса и является входом начальной установки устройства, введены второй и третий элементы И, управляемый делитель частоты импульсов и первую и вторую группы элементов И - НЕ, причем первые входы элементов И - НЕ первой группы .и первые прямые входы элементов И - НЕ второй группы соединены с выходом второго элемента И, инверсный вход которого соединен с выходом управляемого делителя частоты импульсов, тактовый вход которого соединен с выходом генератора тактовых импульсов и с первым входом третьего элемента И, остальные входы которого соединеныс выходами элементов И - НЕ первой и второй групп и с управляющими входами управляемого делителя частоты импульсов, входсброса которого соединен с выходом третьего элемента И, с входом записи регистра адреса и с входом синхронизации регистра блокировки, информмционные входы которого соединены с вторыми входами элементов И - НЕ первой группы и с вторыми прямымивходами элементов И - НЕ вто 1 О рой группы, третьи входы элементов И - НЕ первой группы и инверсные входы элементов И - НЕ второй группы являются входами логических условий группы устройства, прямой вход второго элемента И соединен с выходом признака режима переменного такта регистра микрокоманд.На фиг. 1 представлена схема предлагаемого устройства; на фиг. 2 - схема блока проверки условий; на фиг. 3 - временная диаграмма работы устройства,Устройство микропрограммного управления содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, регистр 3 адреса, блок 4 проверки условий, генератор 5 тактовых импульсов, регистр 6 бло кировки, группу элементов И 7, элемент И 8, элемент И 9, элемент И 10, группы элементов И - НЕ 11, и 12, управляемый делитель 13 частоты импульсов, вход 14 начальной установки, вход 15 условий, первую 16 и вторую 17 группы выходов.30 Блок 4 проверки условий (фиг. 2) содержит группы элементов И 18 и ИЛИ 19.На временной диаграммеработы устройства (фиг, 3) обозначены сигнал 20 начальной установки на входе 14 устройства, импульсы 21 на выходе генератора 5 импульсов, сигнал 22 на выходе элемента И 9, сигнал 23 на выходе элемента И 8, сигналы 24 - 26 микроприказов на выходах соответственно первого, пятого и двенадцатого элементов И 7, сигнал 27 на выходеделителя 13 с переменным коэффициентом деления.Устройство микропрограммного управления работает следующим образом. Для приведения устройства в исходноесостояние на вход 14 подается сигнал 20,в результате чего регистр 2 микрокоманд и регистр 3 адреса устанавливается в ноль. По нулевому адресу из блока 1 памяти микрокоманд выбирается начальная микро- команда и поступает на информационные входы регистра 2 микрокоманд. Так так содержимое регистра 2 микрокоманд равно нулю, на выходах всех элементов И 7 присутствуют нулевые сигналы, в результате чего выбирается сигнал 23, по которому регистр 6 блокировки устанавливается в исходное единичное состояние, а в регистр 2 микрокоманд заносится микрокоманда. 35 405055 Каждая микрокоманда состоит из трех частей, адресной, кода операции и кода микрооперации. Кроме того, в микрокоманде содержится 1 бит признака режима переменного такта.В адресной части микрокоманды, кроме непосредственного адреса следующей микрокоманды, содержится 1 бит признака перехода .(условный и безусловный) .Например, для выполнения микрокоманды, содержащейся в регистре 2 микрокоманд, необходимы три микротакта, причем в течение первого, второго и третьего микро- тактов единичный сигнал должен присутствовать, например, на выходе первого, пятого и двенадцатого элементов И 7.Тогда на выходах первого, пятого и двенадцатого управляющих выходах регистра 2 микрокоманд присутствуют единичные сигналы, а на остальных - нулевые. На выходе первогоэлемента И 7 вырабатывается сигнал 24, в результате чего все последующие элементы И 7 закрываются.Например, по значению сигнала условия, вырабатываемого из операционных схем в результате выдачи первого микроприказа, должен быть организован режим переменного такта. Тогда сигналом 24 выбирается один из элементов И - НЕ групп элементов И - НЕ 11 или 12, на вход которого поступает сигнал соответствующего условия. На входы групп элементов И - НЕ 1 и 12 подключаются сигналы только тех условий, по которым организуется режим переменного такта. Если в результате выдачи микроприказа ожидается нулевое значение условия, условие подключается на вход одного из элементов И - НЕ группы элементов И - НЕ 11. При ожидании единичного значения условия, сигнал условия подключается к входу одного из элементов И - НЕ группы элементов И - НЕ 12.Так как в микрокоманде задан режим переменного такта (бит признака режима переменного такта равен единице), то на вход элемента И 10 с выхода регистра 2 микрокоманд поступает единичный сигнал. Элемент И 10 открывается нулевым сигналом с выхода делителя 13, в результате чего единичным сигналом с выхода элемента И 10 открываются группы элементов И - НЕ 11 и 12.Если значение сигнала условия, поступающего на вход выбранного элемента И - НЕ групп элементов И - НЕ 11 и 12, отличается от ожидаемого, нулевым сигналом с выхода соответствующего элемента И - НЕ групп элементов И - НЕ 11 и 12 закрывается элемент И 9. Сигнал 22 принимает нулевое значение, в результате чего работа устройства приостанавливается, а делитель 13 начинает отсчитывать временной интервал по импульсам 21. Коэффициентделения делителя 13 имеет различное значение при ожидании различных условий. Коэффициент деления задается нулевым сигналом с выхода соответствующего элемента И - НЕ групп элементов И - НЕ 11 или 12.Например, в первом микротакте ожидаемое условие подтверждается раньше, чем делитель 13 отсчитает интервал времени, отведенный на ожидание данного условия. Закрывается соответствующий элемент И - НЕ групп элементов И - НЕ 11 или 12, в результате чего открывается элемент И 9.Во втором микротакте по сигналу 22 и при наличии единичного сигнала на первом установочном входе первый разряд регистра 6 блокировки устанавливается в ноль. По сигналу 22 устанавливается в ноль и делитель 13.Первый элемент И 7 закрывается, открывая тем самым все последующие элементы И 7. Но, так как второй, третий и четвертый элементы И 7 закрыты нулевыми сигналами с управляющчх выходов регистра 2 микро- команд, единичный сигнал 25 выбирается на выходе пятого элемента И 7. Например, условие, ожидаемое по этому микроприказу, не подтверждается в течение отведен ного интервала времени, отсчитываемого делителем 13. Вырабатывается сигнал 2, в результате чего закрываетсч элемент И 10, и соответственно закрываются группы элементов И - НЕ 11 и 12. Открывается элемент И 9, в результате чего вырабатывается З 0 сигнал 22.В третьем микротакте по сигналу 22 устанавливается в ноль пятый разряд регистра 6 блокировки. В результате этого пятый элемент И 7 закрывается, и на выходе двенадцатого элемента И 7 вырабатывается сигнал 26.Режим ожидания по этому микроприказу организуется аналогично описанному.В следующем микротакте по сигналу 22 двенадцатый разряд регистра 6 блокировки 40 устанавливается в ноль, в результате чего закрывается двенадцатый элемент И 7,При этом на выходах всех элементов И 7 единичный сигнал отсутствует, так как нулевые сигналы присутствуют на всех последующих после двенадцатого управляющих выходах регистра 2 микрокоманд, Вырабатывается сигнал 23, .по которому все разряды регистра 6 блокировки устанавливаются в единичное состояние. Одновременно следующая микрокоманда заносится в регистр 2 микрокоманд.Адрес этой микрокоманды формируется по адресной части предыдущей микро- команды, В зависимости от признака перехода, указываемого в адресной части микро- команды, адрес следующей микрокоманды вычисляется безусловно или в зависимости от значения условий, поступающих на входы 15 устройства. Признак перехода поступает на входы элементов И 18, Если значение признака перехода равно нулю на выходах всех элементов И 18 присутствуют нулевые сигналы и адрес следующей микрокоманды определяется непосредственно из адресной части предыдущей. Если признак перехода равен единице, на выходы элементов И 18 поступают сигналы логических условий со входов 15 устройства, а адрес следующей микрокоманды формируется в зависимости от значения этих условий. По сигналу 22 адрес микрокоманды заносится в регистр 3 адреса; в результате чего из блока 1 памяти микрокоманд считывается соответствующая микрокоманда, которая оказывается заранее подготовленной,В микрокомандах, неиспользующих режим переменного такта, бит режима переменного такта равен нулю. В этом случае устройство работает с жестким тактом, определяемым генератором 5 тактовых импульсов.Таким образом, предлагаемое устройство по сравнению с известным может работать с переменным тактом, который регулируется внешним объектом управления, что свидетельствует о более широких функциональных возможностях.1136161 Фиг.2 20 гЗ Лан мокосо Сост о Техр Тира ВНИИПИ Госуда по делам нз 113035, Москва, Ж лиал ППП Патентедактор Н. Лазаренк аказ 10151/37 авнтель Юед И, Вереж 710рственногообретений- 35, Раг. Ужго Корректор АПодписноекомитета СССРи открытийшская наб д. 4/5род ул Проектная

СмотретьЗаявка

3547552, 09.02.1983

ОСОБОЕ КОНСТРУКТОРСКОЕ БЮРО ЮЖНОГО ГОЛОВНОГО МОНТАЖНОГО УПРАВЛЕНИЯ СРЕДСТВ СВЯЗИ ЦЕНТРАЛЬНОГО НАУЧНО ПРОИЗВОДСТВЕННОГО ОБЪЕДИНЕНИЯ "КАСКАД"

ПУШКАРЕВ ЮРИЙ ЯКОВЛЕВИЧ, ПОЛОНСКИЙ ДМИТРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное, управляющее

Опубликовано: 23.01.1985

Код ссылки

<a href="https://patents.su/5-1136161-mikroprogrammnoe-upravlyayushhee-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное управляющее устройство</a>

Предыдущий патент: Нанопрограммное устройство управления

Следующий патент: Микропрограммное устройство управления с контролем

Случайный патент: Устройство для уборки лука