Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

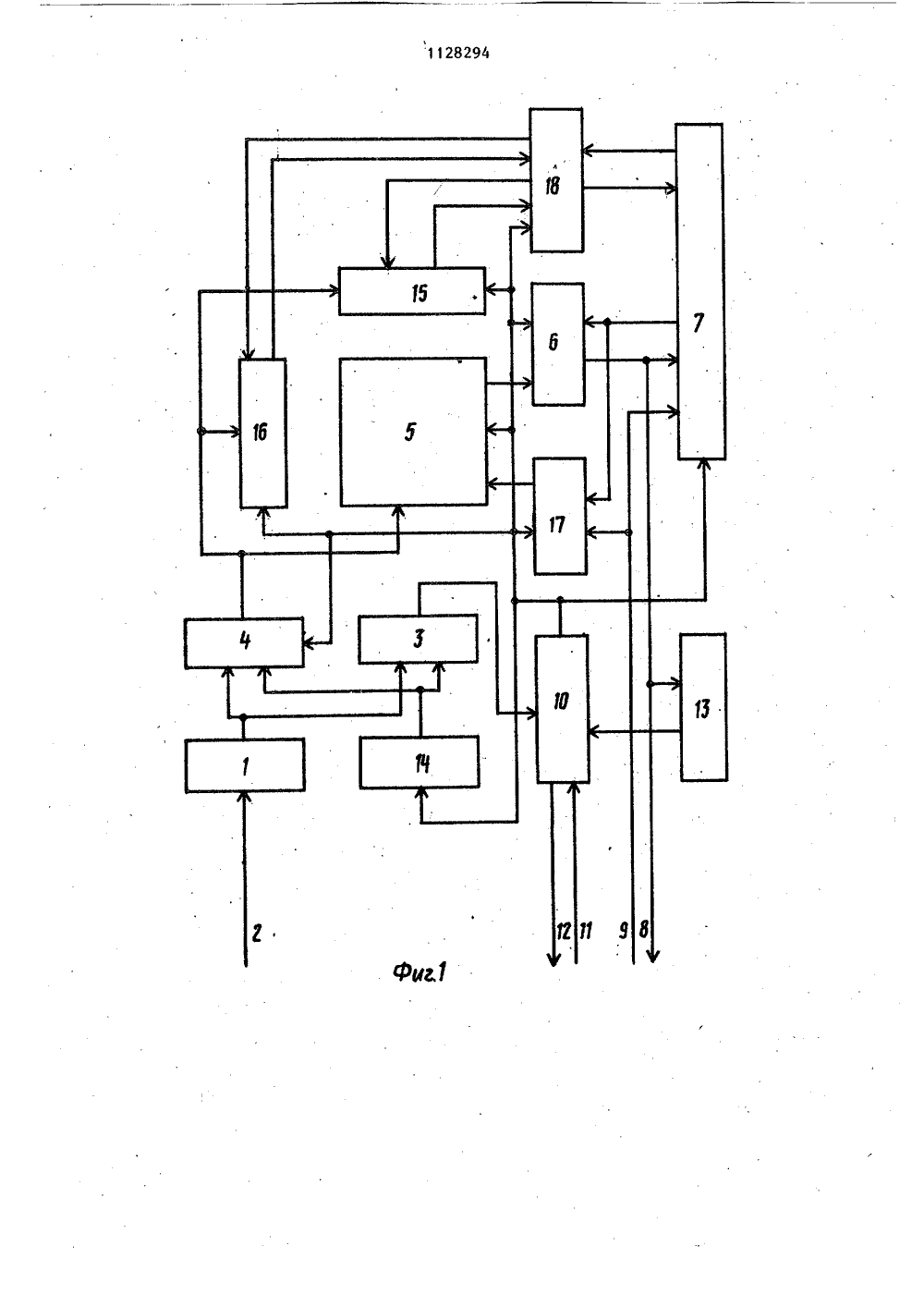

(53) 681,327(088.8) 5Касиян,СУДАРСТВЕННЫЙ НОМИТЕТ СССДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ К АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) 1., Авторское свидетельство СССР В 834771, кл. С 11 С 29/ОО, 19792. Авторское свидетельство СССР У 769641, кл. 6 1 С 29/00, 1979 (прототип).(54)(57) ЗАПОМИНАКЩЕЕ УСТРОЙСТВО СИСПРАВЛЕНИЕМ ОШИБОК, содержащее регистр адреса, мультиплексор, блок сравнения, накопитель, регистр числа логический блок, блок контроляФи блок управления, причем выход ре-гистра адреса подключен к первым входам блока сравнения и мультиплексора, а вход является адресным входом устройства, выход мультиплексора соединен .с первым входом накопителя, первый выход которого подключен к первому входу регистра числа, второй вход которого соединен с первым выходом логического блока, первый вход логического блока, вход блока контроля и выход регистра числа являются информационным выходом устройства, информационным входом которого является второй вход логического блока, первый .выход блока управления подключен к третьим входам регистра числа и логического блока.н второму входу накопителя, второй выход и первыйвход блока управления являются со"ответственно управляющими выходоми входом устройства, второй и третий входы подключены к выходам блока сравнения и блока контроля соответственно, о т л и ч а ю щ е е с ятем, что, с целью повышения надежности устройства, в него введеныдополнительные накопители, регистрконтрольной информации, буферныйрегистр и регистр модифицированногоадреса, вход которого подключен кпервому выходу блока управления, авыход соединен с вторьвии входамиблока сравнения и мультиплексора, выход которого подключен к первым вхо"дам дополнительных накопителей, однииз входов регистра контрольной информации подключены соответственно Фк выходам дополнительных накопителейи второму, выходу логического блока,а выходы - к вторым входам дополнительных накопителей и третьему входулогического блока, первый выход блокауправления подключен к третьим входам дополнительных накопителей имультиплексора, другому входу регистра контрольной информации и одномуиз входов буферного регистра, другие входь 1 которого соединены соответственно с вторым входом. регистрачисла и информационным входом устройства, а выход подключен к третьему входу накопителя.1 О 30 Цель изобретения - повышение надежности устройства.Поставленная цель достигается тем, что в запоминающее устройство с исправлением ошиббк, содержащее регистр адреса, мультиплексор, блок сравнения, накопитель, регистр числа,45 логический блок, блок контроля и блок управления, причем выход регистра адреса подключен к первьм входам блока сравнения и мультиплексора, а вход является адресным входом устройства, выход мультиплексора сое ,динен с первым входом накопителя, ,йервый выход которого подключен к первому входу регистра числа, второй вход которого соединен с пер вым выходом логического блока, первый вход логического блока, вход ,блока контроля и выход регистра чис Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.Известно запоминающее устройствос самоконтролем, содержащее группу 5накопителей, дешифратор, блок контроля и блок управления, причем выходы накопителей подключены к входамблока контроля И ,Недостатками этого устройстваявляются ограниченная возможностьего применения и отсутствие возможности исправления ошибочной информации,.Наиболее близким к изобретению 15является запоминающее устройство,содержащее накопитель, блок управления, арифметический блок, блокобнаружения и коррекции ошибок, пер-вый, второй.и третий регистры, причем вход блока обнаружения и.коррекции ошибок соединен с входом устройства, первый выход - с первым входомтретьего регистра, второй выходс входом блока управления и первым .25входом арифметического блока,. второй вход которого подключен к первому выходу блока управления, третийвход - к выходу третьего регистра,первый выход - к входу первого ре-.гистра, выход которого соедичен спервьы выходом устройства 2 .Недостатком известного устройстваявляется низкая надежность связи с.необходимостью проведения коррекцииодной и той же ошибки при каждом обращении по адресу, содержащему ошиб" .ку,ла являются информационным выходом устройства, информационным входом которого является второй вход логи-. ческого блока, первый выход блока управления подключен к третьим входам регистра числа и логического блока и второму входу накопителя, второй выход и первый вход блока управления являются соответственно управляющими выходом и входом устройства,.второй и третий .входы подключены к выходам блока контроля соответственно, введены дополнительные накопители, регистр контрольной информации, буферный регистр и регистр модифицированного адреса, вход которого подключен к первому выходу блока управления, а выход соединен с вторыми входами блока. сравнения и мультиплексора, выход которого подключен к первым входам дополнительных накопителей, одни из входов регистра контрольной информа ции подключены соответственно к выходам дополнительных накопителей и второму выходу логического блока, а .выходы - к вторым входам дополнительных накопителей и третьему вхо" ду логического блока, первый выход ;блока управления подключен к третьим входам дополнительных накопителей. и мультиплексора, другому входу регистра контрольной информации и одному из входов буферного регистра, другие входы которого соединены со-. ответственно со вторым. входом регист ра числа и информационным входом устРойства, а .выход подключен к третьему входу накопителя.На фиг. 1 изображена структурная схема предложенного,устройствами на,. фиг.2 - временные диаграммы его работы.Запомйнающее устройство с исправлением, ошибок содержит регистр 1 адре-. са, имеющий вход 2, блок 3 сравнения, мультиплексор 4,. накопитель 5, регистр 6 числа,.логический. блок 7, при этом оио имеет информационные выход 8 и вход 9, а.также блок 10. управления, имеющий вход 11 и выход 12, блок 13 контроля, регистр 14 модифицированного адреса, дополнительные накопитепи 15 и 16, служащие соответственно для хранения горизон;тальных и вертикальных контрольных 1 сумм, буферный регистр 17.и регистр 18 контрольной информации.282944 50 55 3 1Блок 10 управления может быть выполнен из последовательно соединенных блока формирования адреса накопителя, микрокоманд, регистра микро- команд и дешифратора. Устройство работает следующим образом.Адрес, поступающий по входу 2 регистра 1, запоминается в нем и далее через мультийлексор 4, управляемый блоком 10 управления, поступает на вход накопителя 5. Одновременно по входу 11 блока 10 сигналы "Запись" или "Чтение" поступают в блок 10 управления, который организовывает работу устройства соответственно в режиме "Запись" или "Чтение" (фиг.2).В режиме "Чтение" накопитель 5 выдает на вход регистра 6 слово, считанное по поступившему адресу. С выхода регистра 6 ийформация поступает на вход блока 13. После 1 ний анализирует исправность информации и через блок 10 управления разрешает, в случае исправной информации, выдачу из устройства признака выдачи информаци по его выходу 12.Таким образом, при исправной информации бйстродействие запоминающего устройства не снижается и равно номинальному быстродействию накопителя 5 (фиг.2, режим."Чтение" ).В режиме записи устройство принимает информацию в регистр 17 и в дальнейшем работает автономно, Блок . 10 управления. по .поступившему сигнату "Запись.организовывает первоначально считывание.информации из накопителя 5, Одновременно снакопителей 15 и 16 считв 1 ваются контрольные суммы той области памяти, к которой произошло обращение, и через регистр 18 поступают на вход блока 7. Под управлением блока 10 блок 7 корректирует значение контрольньи сумм, вычитая значение считанной информации (содержимое регистра 6) и суммируя значение содержимого регистра 17. Откорректированные контрольаые суммы помещаются обратно в регистр 18. После этого под управлением блока 10 информация. с регистра 17 и контрольные суммыс регистра 18 записываются соответственно в накопителе 5 и накопителях 15 и 16.Таким образом, контрольные суммы модифицируются при записи каждогоъ 5 1 О и 15 20 25 30 35 40 45 нового значения информации и всегда отражают реальное содержание накопителя 5 (фиг.2, режим "Запись" ).В случае обнаружения ошибки блоком 13 запрещается вьдача из устройства признака выдачи информации. При одном ошибочном слове блок 10 управления организовывает считъвание горизонтальной контрольной суммы той ббласти памяти, в которой обнаружена ошибка, производит последовательное считывание слов всей области памяти и вычитания их значения контрольной суммы посредством блока 7. Заведомо ошибочное слово, которое определяется сравнением адресов блоком 3 сравнения, при этом не считывается. На последнем шаге вычисления в регистре 18 определяется истинное значение информации, ранее считанной ошибочной. Через регистр 17 эта информация под управлением блока 10 записывается в новую область памяти с дальнейшим обращением за ней в эту область (Фиг.2, режим исправления ошибочного слова) .В случае возникновения ошибки при считывании каждого слова блок 13 определяет ее как ошибку одного разряда всех слов (случай отказа выходного усилителя), блок 10 организовывает считьвание вертикальной контрольной суммы той области памяти, которая содержит ошибки. В дальнейшем организовывается считывание всех слов данной области памяти и их поразрядное суммирование внутри одного слова с последующим . вычитанием каждой поразрядной суммы из значения контрольной суммы.Таким образом, на последнем шагев регистре 18 определено истинное значение всех вертикальных разрядов, считываемвк ранее отказавшим выходным усилителем накопителя 5. Через регистр 17 эта информация записывается в новую область памяти с дальнейшим обращением к этой области (Фиг.2, режим исправления многократ- ной ошибки). Технико-экономическое преимущест,во предлагаемого устройства заключается в том, что оно обеспечивает эффективное исправление ошибочной ин-формации эа счет наделения его функциями самоисправления как одного ошибочно.го слова,так имногократных ошибок .1128294 Режим Режим Режим ислрадмиив Ремаю екрайеаетедив зааки оцкдооеого сддооа дддавкрюева аввйж ЛЛПЛГ 1 Резистр Ю.Л АГ 1.П Срабиенце абресод ррцьнак бидаеикр.рраем иео, б режтрм бц 17 взбюка 7 ставитель В хред А.Ачк орректор О.Би иколайч акто П Тираж 574 ВНИИПИ Государственного коми по делам иэобретений и от 3035, Москва, Ж, Раушская

СмотретьЗаявка

3455325, 18.06.1982

ПРЕДПРИЯТИЕ ПЯ В-2667

БРЮХОВИЧ ЕВГЕНИЙ ИВАНОВИЧ, КАСИЯН ИВАН ЛЕОНОВИЧ, КЕЙБАШ ВИКТОР САМОЙЛОВИЧ, ЧОФУ МАРЧЕЛ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 07.12.1984

Код ссылки

<a href="https://patents.su/5-1128294-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Способ передачи азимута и координат в подземные горные выработки

Следующий патент: Способ намагничивания четырехполюсного постоянного магнита с полюсами на внешней цилиндрической поверхности

Случайный патент: Способ получения изображений на цветных обращаемых галогенсеребряных фотографических материалах