Устройство для умножения двоичных чисел в дополнительных кодах

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

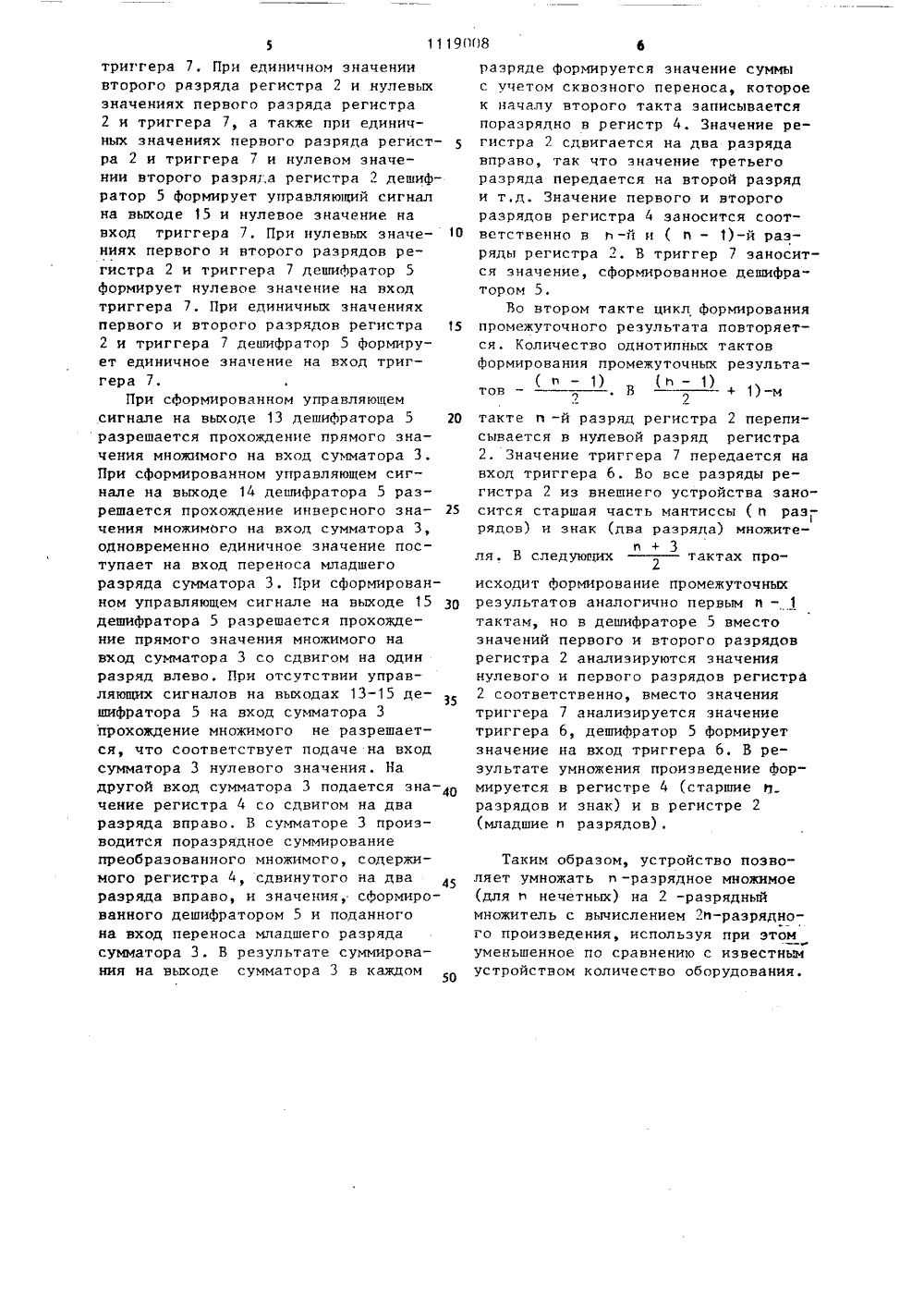

СОЮЗ СОВЕТСКИХСоЕЛИЛ акинкРЕСПУБЛИК 91 И 00 А зею о ОПИСАНИЕ ИЗОБРЕТЕНИЯ / " К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) 1. Авторское свидетельство СССРУ 487386, кл. 6 Об Г 7/52, 1975.2. Авторское свидетельство СССРМф 813420, кл, 5 Об Г 7/52, 1981(прототип),(54)(57) УСтРОЙСтво Для л 1 НОЖЕНияДВОИЧНЫХ ЧИСЕЛ В ДОПОЛНИТЕЛЬНЬЖ КОДАХ, содержащее регистр множимого,сдвиговый регистр множителя, трехвходовой сумматор, регистр поразрядныхсумм, дешифратор цифр множителя,первый и второй триггеры,первую,вторую и третью группы элементов И,группу элементов ИЛИ, причем выходыпервого и второго разрядов сднигового регистра множителя соединены спервым и вторым входами дешифраторацифр множителя, первый, второй итретий выходы которого соединены спервыми входами элементов И первой,второй и третьей групп соответственно, четвертый выход дешифратора цифрмножителя через первый триггер соединен с третьим входом дешифраторацифр множителя, вторые входы элементов 1 первой группы соединены соответственно с прямыми выходами регист ра множимого, вторые входы элементовИ второй группы соединены соответственно с прямыми выходами регистрамножимого со сдвигом на один разрядвлево, вторые входы. элементов Итретьей группы соединены соответственно с инверсными выходами регистрамножимого, выходы элементов И первой,второй и третьей групп соединены свходами соответствующих элементовИЛИ группы, выходы которых соединеныс соответствующими входными разрядами первого входа сумматора, первыйвыход которого соединен с разряднымивходами регистра поразрядных сумм,выход регистра поразрядных сумм соединен с соответствующими разрядамивторого входа сумматора со сдвигомвправо на дна разряда, о т л и ч а -ю щ е е с я тем, что, с целью упрощения устройства, пятый выход дешифратора цифр множителя через второйтриггер соединен с четвертым входомдешифратора цифр множителя, выходнулевого разряда сднигоного регюстрамножителя соединен с пятым входомдешифратора цифр множителя, третийвыход которого соединен с третьимвходом сумматора, выходы двух первыхмладших разрядов сумматора соединенысоответственно с входами первого ивторого знаковых разрядов сдниговогорегистра множителя, выход второготриггера соединен с входом установкив ноль первого триггера.1 111908 2 Изобретение относится к вычисли- запоминания единицы тельной технике и может быть исполь- кода и вторые входы завано в арифметических устройствах рой группы соединень ЗВМ. выходом дешифратора Известно устройство для умножения 5 выход триггера запо двоичных чисел в дополнительных ко- дополнительного код дах содержащее регистры множителя, младшим разрядом пер множимого и результата, дешифратор, полнительного суммат сумматор, элементы И 1. щего разряда регистр Недостаток данного устройства - .1 О переносов соединен с невысокая точность вычисления. дом пе ваго вхо а оНаиболее близким по технической сущности к изобретению является устРойство для умножения двоичных чисел в дополнительных кодах, содержащее регистр множимого, сдвиговый регистр множителя, трехвкодовой сумматор, регистр поразрядных сумм, регистрпорязрядных переносов, дешифратор рО цифр множителя, триггер запоминания результата дешифрации, три группы элементов И, группу элементов ИЛИ, триггер запоминания единицы дополнительного кода, триггер запоминания переноса и дополнительный сумматор, причем выходы двух младших разрядов сдвигового регистра множителя соединены с первым и вторым входами дешифратора цифр множителя, первый и второй выходы которого соединены с первыми входами элементов И первой и , второй групп соответственно, третий выход дешифратора цифр множителя через триггер запоминания результатов дешифрации соединен с третьим вкадом З 5 дешифратора цифр множителя, вторые входы элементов И первой группы соединены с прямыми выходами соответствующих разрядов регистра множимого, первые входы элементов Итретьей 4 О группы соединены с инверсными выходами соответствующих разрядов регистра множимого, вторые входы элементов И второй группы срединены со сдвигом влево на один разряд с прямыми выхо дами разрядов регистра множимого, выходы элементов И первой, второй и .третьей групп соединены с входами соответствующих элементов ИЛИ группы, выходы которых соединены с входами соответствующих разрядов первого входа сумматора, первый и второй выходы сумматора соединены с входами регист; ,Ра поразрядных сумм и регистра порази рядных переносовсоответственно, вы коды которых соединены соответственно с вторым и третьим входами сумматора, установочный вход триггера дополнительногоэлементов И вто с четвертымцифр множителя,минания единицыа соединен сваго входа доора, выход млада поразрядныхо старшим разряР д д полнительного сумматора, выход младшего разряда поразрядных переносов соединен со старшим разрядом первого входа дополнительного сумматора, разряды второго входа дополнительного сумматора соединены с выходами дополнительных разрядов регистра поразрядных сумм, входы которых соединены с выкодами разрядов дополнительного сумматора, выход переноса дополнительного сумматора через триггер запоминания переноса соединен с третьим входом дополнительного сумматора 2.Недостатком данного устройства является большой объем оборудования.Цель изобретения - упрощение устройства.Поставленная цель достигается тем, что в устройстве для умножения двоичных чисел в дополнительных кодах, содержащем регистр множимого, сдвиговый регистр множителя, трехвходовой сумматор, регистр поразрядных сумм, дешифратор цифр множителя, первый и второй триггеры, первую, вторую и третью группы элементов И, группу элементов ИЛИ, причем выходы первого и второго разрядов сдвиговога регистра множителя соединены с первым и вторым входами дешифратора цифр множителя, первый, второй и третий выходы которого соединены с первыми входами элементов И первой, второй и третьей групп соответственно, четвертый выход дешифратора цифр множителя через первый триггер соединен с третьим входом дешифратора цифр множителя, вторые входы элементов И первой группы соединены соответственно с прямыми выходами регистра множимога, вторые входы элементов И второй группы соединены соответственно с прямыми выходами регистра мнажимого со сдвигам на один Разряд влево, вторые входы элементов И третьей группы соединены соответственно с инверсными выходами регистра множимого, выходы элементов И первой,элементов ИЛИ 11 группы, выходы которих соединены с соответствующимивходными разрядами первого входа сумматора 3, первый выход которого соединен соответственно с разряднымивходами регистра 4 поразрядных сумм,выход регистра 4 поразрядных суммсоединен с соответствующими разрядами второго входа сумматора 3 со сдвигом вправо на два разряда, пятый выход дешифратора 5 циФр множителя через триггер 7 соединен с четвертымвходом дешифратора 5 цифр множителя,выход нулевого разряда сдвиговогорегистра 2 множителя соединен спятым входом дешифратора 5 цифр множителя, третий выход которого соединен с третьим входом сумматора 3, выходы двух первых младших разрядов сумматора 3 соединены соответственно с входами первого и второго знаковых разрядов сдвигового регистра 2 множителя, "выход триггера 7 соединен с входом установки в ноль триггера 6.Устройство работает следующим образом.Перед выполнением умножителя в регистре 1 множимого хранится множимое, представленное в дополнительном коде с ь -разрядной мантиссой и одним знаковым разрядом, а в сдвиговом регистре 2 множителя хранится и младших разрядов множителя, представленного в дополнительном коде с нразрядной мантиссой и двумя знаковыми разрядами. Регистр 4 поразрядных сумм обнулен.В каждом такте умножения в дешифраторе 5 анализируются первый и второй младшие разряды регистра 2 и значение триггера 7, которое в исходном положении равно нулю. При нулевых значениях второго разряда регистра 2 и триггера 7 и единичном значении первого разряда регистра 2, а также при единичном значении триггера 7 и нулевых значениях первого и второго разрядов регистра 2 дешифратора 5 Формирует управляюций сигнал на выходе 13 и нулевое значениена вход триггера 7. При единичныхзначениях первого.и второго разрядоврегистра 2 и нулевом значении триггера 7, а такде при нулевом значениипервого разряда регистра 2 и единич"ных значениях второго разряда регистра 2 и триггера 7 дешифратор 5 Формирует управляюций сигнал на выходе14 и единичное значение на вход Э 1119008 4второй и третьей групп соединены свходами соответствующих элементовИЛИ группы, выходы которых соединены с соответствуюцими входными разрядами первого входа сумматора, первый выход которого соединен с разряд 5ными входами регистра поразрядныхсумм, выход регистра поразрядныхсумм соединен с соответствующими разрядами второго входа сумматора сосдвигом вправо на два разряда, пятыйвыход дешифратора цифр множителя через второй триггер соединен с четвертым входом дешифратора цифр множителя, выход нулевого разряда сдвигово 15го регистра множителя соединен спять 1 м входом дешифратора цифр множителя, третий выход которого соединенс третьим входом сумматора, выходыдвух первых младших разрядов сумма 20тора соединены соответственно с входами первого и второго знаковых разрядов сдвигового регистра множителя,выход второго триггера соединен. свходом установки в ноль первого триг 25гера,Функциональная схема устройствадля умножения двоичных чисел в дополнительных кодах представлена начертеже.Устройство содержит регистр 1множимого, сдвиговый регистр 2 множителя, трехвходовой. сумматор 3, регистр 4 поразрядных сумм, дешифратор5 цифр множителя, триггеры 6 и 7,первую, вторую и третью группы элементов И 8-10 и группу элементов .ИЛИ 11, причем выходы первого и второго разрядов сдвигового регистра 2множителя соединены с первым и вторым входами дешифратора 5 цифр множителя, первьпЪ, второй и третий выходы которого соединены с первымивходами элементов И 8-10 групп соответственно, четвертый выход 12, дешифратора 5 цифр множителя через 45триггер 6 соединен с третьим входомдешифратора 5 цифр множителя, вторыевходы элементов И 8 групп соединенысоответственно с прямыми выходамирегистра 1 множимого, вторые входы 50элементов И 9 группы соединены соответственно с прямыми выходами регистра 1 множимого со сдвигом на одинразряд влево, вторые входы элементовИ 10 группы соединены соответственно 55с инверсными выходами регистра 1 множимого, выходы элементов И 8-10 группсоединены с соответствующими входамитриггера 7. При единичном значении второго разряда регистра 2 и нулевых значениях первого разряда регистра 2 и триггера 7, а также при единичных значениях первого разряда регистра 2 и триггера 7 и нулевом значении второго разряда регистра 2 дешифратор 5 формирует управляющий сигнал на выходе 15 и нулевое значение на вход триггера 7. При нулевых значе О ниях первого и второго разрядов регистра 2 и триггера 7 дешифратор 5 формирует нулевое значение на вход триггера 7. При единичных значениях первого и второго разрядов регистра 15 2 и триггера 7 дешифратор 5 формирует единичное значение на вход триггера 7.При сформированном управляющем сигнале на выходе 13 дешифратора 5 20разрешается прохождение прямого значения множимого на вход сумматора 3. При сформированном управляющем сигнале на выходе 14 дешифратора 5 разрешается прохождение инверсного зна чения множимого на вход сумматора 3, одновременно единичное значение поступает на вход переноса младшего разряда сумматора 3. При сформированном управляющем сигнале на выходе 15 дешифратора 5 разрешается прохождение прямого значения множимого на вход сумматора 3 со сдвигом на один разряд влево. При отсутствии управляющих сигналов на выходах 13-15 де 35 шифратора 5 на вход сумматора 3 прохождение множимого не разрешается, что соответствует подаче на вход сумматора 3 нулевого значения. На другой вход сумматора 3 подается эначение регистра 4 со сдвигом на два разряда вправо. В сумматоре 3 производится поразрядное суммирование преобразованного множимого, содержимого регистра 4, сдвинутого на два разряда вправо, и значения, сформированного дешифратором 5 и поданного на вход переноса младшего разряда сумматора 3. В результате суммирования иа выходе сумматора 3 В каждом 50 разряде формируется значение суммы с учетом сквозного переноса, которое к началу второго такта записывается поразрядно в регистр 4. Значение регистра 2 сдвигается на два разряда вправо, так что значение третьего разряда передается на второй разряд и т.д, Значение первого и второго разрядов регистра 4 заносится соответственно в ь -й и ( и - 1)-й разряды регистра 2. В триггер 7 заносится значение, сформированное дешифратором 5.Во втором такте цикл формирования промежуточного результата повторяется. Количество однотипных тактов формирования промежуточных результа( т - 1) ( о - 1) тов В, + 1)-м такте п -й разряд регистра 2 переписывается в нулевой разряд регистра 2. Значение триггера 7 передается на вход триггера 6. Во все разряды регистра 2 из внешнего устройства заносится старшая часть мантиссы ( п разрядов) и знак (два разряда) множитео + 3ля. В следующих2тактах происходит Формирование промежуточных результатов аналогично первым п - 1 тактам, но в дешифраторе 5 вместо значений первого и второго разрядов регистра 2 анализируются значения нулевого и первого разрядов регистра 2 соответственно, вместо значения триггера 7 анализируется значение триггера 6, дешифратор 5 формирует значение на вход триггера 6. В результате умножения произведение формируется в регистре 4 (старшие 1 разрядов и знак) и в регистре 2 (младшие и разрядов). Таким образом, устройство позволяет умножать и -разрядное множимое (для и нечетных) на 2 -разрядный множитель с вычислением 2 п-разрядное го произведения, используя при этом уменьшенное по сравнению с известньи устройством количество оборудования,1119008 каз 1454 Подписноео комитета СССРий и открытийская наб., д. 4/5 6 Тираж 698 ВНИИПИ Государственно по делам изобрете 3035, Москва, Ж, Рауш

СмотретьЗаявка

3603858, 16.06.1983

ПРЕДПРИЯТИЕ ПЯ А-1639

ДРАБКИН АЛЕКСАНДР АРНОЛЬДОВИЧ, ЕВДОКИМОВ АЛЕКСАНДР ВАСИЛЬЕВИЧ, ЖАРИКОВ ВЯЧЕСЛАВ ПЕТРОВИЧ, КАПЛАН ЛЕОНИД ВИКТОРОВИЧ, КРЕЙНДЛИН ЛЕОНИД ЭММАНУИЛОВИЧ, РОМАШОВ БОРИС ИЛЬИЧ

МПК / Метки

МПК: G06F 7/52

Метки: двоичных, дополнительных, кодах, умножения, чисел

Опубликовано: 15.10.1984

Код ссылки

<a href="https://patents.su/5-1119008-ustrojjstvo-dlya-umnozheniya-dvoichnykh-chisel-v-dopolnitelnykh-kodakh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения двоичных чисел в дополнительных кодах</a>

Предыдущий патент: Устройство для умножения

Следующий патент: Цифровой функциональный преобразователь

Случайный патент: Каталитический нагреватель