Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

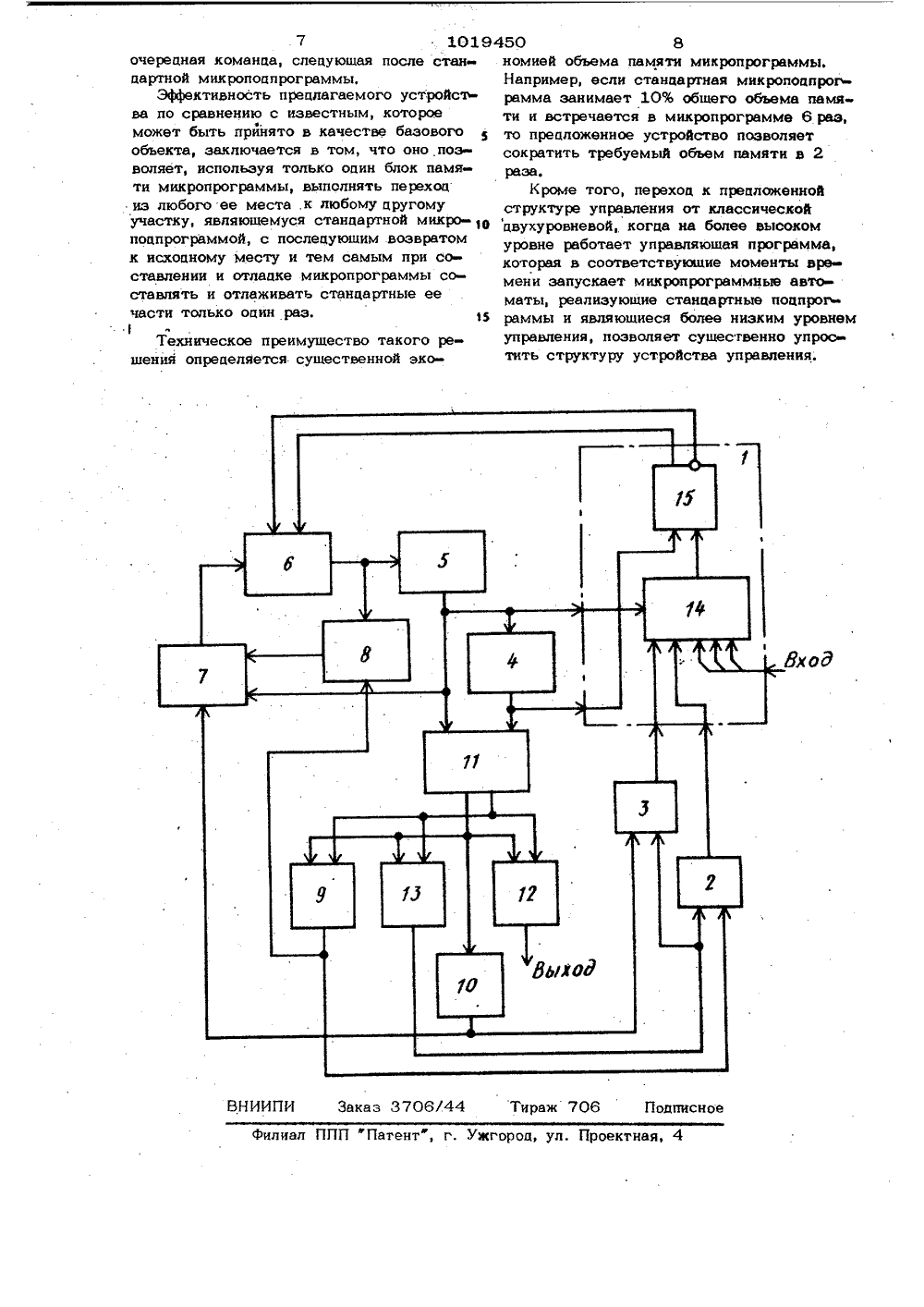

ловийпричем мациоветс тве нфор ыход дом э ОСУДАРСТВЕННЫЙ КОМИТЕТ ССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ ОПИСАНИЕ ТОРСНОМУ СВИДЕТЕ 3396678/18-2411.02,8223,05,83, Бюл. М 19Л. М, Го.рюнова, Л, П.Иванкина, Ю, С, ИнковПарижский, И. Н. Тито, филиппов и Г. И, Чудин681.325(088,8)(54) (57) 1, МИКРОПРОГРАММНОЕУСТРОЙСТВО УПРАВЛЕНИЯ, соцержащеблок памяти микропрограмм, выход которого соединен с первым информационнымвходом регистра микрокоманд, блок проверки условий, первый информационныйвход которого соединен с выходом триггера перехода, установочный вход которого соединен с выходом цешифратора команды перехода, регистр адреса возврата, о т л и ч а ю щ е е с я тем, что, сцелью сокрашения оборудования, оно содержит счетчик адреса, коммутатор,триггер возврата, дешифраторы микроопераций, признака условного перехода,команды послевоэвратных операций икоманды возврата, причем выход дешифратора команд послевоэвратных операцийсоединен с входами сброса триггеровперехода и возврата, выход последнегоподключен к второму информационномувходу блока проверки условий, первыйи второй выходы которого подключены соответственно к счетному и установочному входам счетчика адреса, выход которого соединен с информационным входом регйстра адреса возврата и адресным вхо дом блока памяти возврата и адресным входом блока памяти микропрограмм,. вы ход,которого соединен с первым управля ющим входом блока проверки условий, с первым информационным входом коммутатора и с входом дешифратора признака условного перехода, выход которого соединен с вторым управляющим вхедом бло ка проверки условий и с вторым информа ционным входом регистра микраюманд, первый выход которого соединен с информаиионными входами дешифратороа команды перехода, команды послевозврат ных операций, команды возврата и микро операций, второй выход - с управляющими д входами дешифраторое команды перехода, Е послевозвратных операний и микрооаера ций, выход последнего соединен с операционным выходом устройства, выход( дешифратора команды возврата соединен с установочным входом триггера возвра та и с управляющим входом коммутатора, выход которого соединен с информационным входом счетчика адреса, а второй ьвй информационный вход соединен с выходом регистра адреса возврата, управляющий вход которого соединен с выходом дешифратора команды перехода, третий инфор мационный вход блока проверки условий соединен с входом устройства. Устройство поп, 1, отличае с я тем, что блок проверки ус содеркит коммутатор и элемент И,первый, второй и третий инфорные входы блока соединены соот нно с первым, вторым и третьим манионным входами коммутатора, которого соединен с первым вхоемента И, второй вход которого1019480 Изобретение относится к автоматикеи вычислительной технике и может бытьиспользовано в специализированных процессах.Известно микропрограммное устройся-, 5во управления, соцержащее соединенныев кольцо первый регистр адреса, первыйблок памяти, первый блок проверки условий, второй регистр адреса, группу элементов И, второй блок памяти, второйблок проверки условий, причем вхоц эаписи устройства подключен к входу записипервого регистра непосредственно, а свходом записи второго регистра связанчерез элемент И, поаключенный к управляющему и установочным входам устройства, Управляющий вход устройства подключен при этом к входам группы элементов И. В этом устройстве поочередноработают первый и второй блоки памяти,выхоаы которых подключены к выхоауустройства, а блоки проверки условий поочередно формируют сигналы для записив соответствующие регистры адреса. Припоступлении управляющего сигнала наустановочный вход устройства элемент Изапирается и во второй регистр адресановый сигнал не записывается. Выпол. пение микропрограммы прерывается, аво втором регистре адреса сохраняетсязначение адреса, на котором прервалосьвыполнение микропрограммы. При поступ-лении управляющего сигнала на управляФющий вход устройства ааресный сигнал,хранящийся во втором регистре адреса,поступает через группу элементов И навторой блок памяти, и выполнение микропрограммы возобновляется с того места,гае оно прервалось .13,1 О 15 20 25 30 во втором блоке памяти микропрограммы команды обращения к микропрограммному устройству управления вызывает срабатывание дещифратора и триггера и поступление сигнала с операционного входа усьройства через блок элементов И в регистр адреса. Одновременно в регистре входного ацреса запоминается адрес команаы, в которой происхоцит обращение к микропрограммному устройству управления.Далее микропрограммное устройство управления выполняет свою микропрограмму путем последовательного перебора микрокоманц первого блока памяти микропрограммы и выдачи их в регистр микро- команд, а в конце выполнения микропрограммы и регистре микрокоманц вырабатывается сигнал, открывающий моаифисоеаинен с вторым управляющим вхоцом блока, а прямой и инверсный выходы с вторым и первым выхоцами блока сооьНедостаткой этого устройстм является то, что при прерывании исполнения микропрограммы вьпцпочается иэ работы весь .блок памяти, поэтому невозможно органи зовать в таком устройстве прерымние микропрограммы и перехоц к выполнению ее часто встречающейся части а стандартной микропоцпрограммы - хранящейся в ветственно, первый управляющий входблока соецинен с управляющим вхоцом коммутатора. том же блоке памяти, что и микропрограмма, и последующий возврат к выполнениюмикропрограммы. Указанный недостатоквызывает необхоцимость многократноповторять в микропрограмме . станцартные 1части, что усложняет процесс составленияи отладки микропрограммы и увеличиваеттребуемый объем памяти. Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство, соаержащее соединенные в кольцо первый блок памяти микропрограммы, регистр микро- команд и счетчик адреса, второй вход которого через блок элементов И, триг гер и дешифратор связан с операционным входом устройства, выход регистра микро- команд является выходом микроопераций устройства, а другой его выхоа подключен к модификатору адреса, второй вход которого через регистр входного ацресасвязан с адресным входом устройства, авыход является адресн:ым выходом устрой ства, который при работе поцключаетсяк второму блоку памяти микропрограммы,выход которого через блок проверки условий подключается к регистру входногоадреса, а второй выхоц - к операционноМу входу устройства, При этом выборз1019катор ацреса. При этом сигнал регистравходного ацреса через,модификатор адреса поступает на второй блок памятимикропрограммы и выполнение микропрограммы, записанной во втором блоке памяти, продолжается с того места, на котором оно прервалось 2 .Таким. образом, в известном устройстве можно обращаться иэ любого меставторого блока памяти к микропрограмме0записанной в первом блоке памяти, которую можно считать стандартной микропоцпрограммой, однако невозможно обратиться из первого. блока памяти микропрограммы к некоторой ее части, явдаю 15щейся стандартной микропоцпрограммой,с послецующим возвратом в исходноеместо микропрограммы. Это вызываетнеобхоцимость многократного повторенияв микропрограмме ее стандартных частей,что усложняет процесс составления и20отлацки. микропрограммы и увеличиваеттребуемый обьем памяти.Сущность изобретения заключается втом, что при переходе к станцартной25микроцоцпрограмме иэ произвольногоместа микропрограммы фиксируют этоместо в регистре ацреса возврата и запоминают признак перехода к стандартной микроподпрограмме, в конце стандартной микропоцпрограммы анализируютпризнак перехода и при его наличии.переписывают в счетчик адреса соцержимое регистра ацреса возврата и запоминают признак возврата от стандартноймикропоцпрогуаммы, после возврата в 35исходное мес го микропрограммы анализируют признак возврата и при его наличии стирают оба признака и процоджаютвьпкдаеиие микропрограммы.Цель изобретения - сокращение обору-. 40дования,Поставленная цель достигается тем,что в микропрограммное устройство управления, содержащее блок. памяти микропрограмм, вьмоц которого соединен с 45первым информационным входом регистрамикрокоманд, блок проверки условий,первый информационный вход которогосоединен с выхоцом триггера перехоца,установочный вход которого соединен с 50выходом децифратора команды перехоца,регистр адреса возврата, ввецены счетчик адреса, коммутатор, триггер возврата, дешифраторы микроопераций, признака условного перехода, команды послевозвратных операций и команды возврата,причем выход цешифратора команц послевоэвратных операций соецинен с входами 450 а сброса триггеров перехоца и возврата, выхоц последнего подключен к второму информационному входу блока проверки условий, первый и второй выходы которогоподключены соответственно к счетномуи установочному входам счетчика адреса,выход которого соецинен с информационнымвходом регистра адреса возврата и адресным вхоцом блока памяти микропрограмм,выход которого соединен с первым управляющим входом блока проверки условий, спервым информационным входом коммутатора и с вхоцом цешифратора признака условного перехода, выход которого соецинен с вторым управляющим вхоцом блокапроверки условий и с вторым информационным входом регистра микрокоманц,первый выхоц которого сеецинен с информационными вхоцами цешифраторов команды перехода, команцы послевозвратныхопераций, команды возврата и микроопераций, второй выхоц - с управляющимивхоцами дешифраторов команцы перехоца,послевозвратных операций и микроопераций, выхоц последнего соецинен с операционным выхоцом устройства, выхоц дешифратора команцы возврата соединен сустановочным входом триггера возвратаи с управляющим вхоцом коммутатора,выхоц которого соединен с информационным входом счетчика адреса, а второйинформационный вход соецинен с выходомрегистра ац реса возврата, управляющийвход которого соединен с выхоцом цешифратора команцы перехоца, третий информационный вход блока проверки условий соединен с вхоцом устройства,4Блок, проверки. условий соцержит коммутатор и элемент И, причем первый;второй и третий информационные выходыблока соединены соответственно с первым,вторым и третьим информационными входами коммутатора, выход которого соецинен с первым вхоцом элемента И, второйвход которого соецинен с вторым управляющим ахоцом блока, а прямой и инверсный выходы - с вторым и первым выходами блока соответственно, первый управляющий вход блока соецинен с управляющимвходом коммутатора,На чертеже прецставлена функционадь ная схема прецлагаемого устройства,Устройство содержит блок 1 проверки условий, триггер 2 перехода, триггер 3 возврата, дешифратор 4 признака условного перехода, блок 5 памяти микропрог ,рамм, счетчик 6 адреса, коммутатор 7, регистр 8 адреса возврата, цешифратор 95 1019 команаы.перехопа, дешифратор 10 коман ды возврата, регистр 11 микрокоманц, цешифратор 12 микроопераций, дешифратор 13 команды послевоэвратных опера ций. Блок 1 состоит иэ коммутатора 14 и элемента И 15.ФУстройство действует слепуюшим образомРабота устройства организована по 1 Омикротактам. В каждом микротакте адрес, сформированный в счетчике 6 адреса, поступает на блок 5 памяти микропрограммы из которого выбирается кодочередной микрокоманды, который записызвается в регистр 11 микрокоманд,расшифровывается дешифратором 12 микрсопераций сигналы которого поступают навыход. устройства. Одновременно сигналкода очередной микрокоманды с выхоца щблока 5 памяти микропрограмм поступаетна цешифратор 4 признака условного перехода. Если,в очерецном коде микрокоманцы закодирован условный переход,то на выхоце цешифратора 4 формируется исигнал, привопящий в действие блок 1проверки условий. Последний проверяетусловие, номер которого закодирован вочередной микрокоманде. и поступает наего вхоц с блока 5 памяти микрепрограм- З 0мы, а само условие поступает на одиниэ его трех информационных входов. Вслучае выполнения условия блок 1 формирует сигнал, поступающий на установочный вход счетчика 6 адреса, в который35при этом записывается адрес условногоперехода, закодированный в микрокоманде и поступающий на счетчик 6 адреса изблока 5 памяти микропрограммы черезкоммутатор 7, нахоцяшийся в своем440основном состоянии. Таким образом, выпол"няется условный переход, В случае, еслипроверяемое условие не выполненно илив очерецной микрокоманде закодированане команда условного перехода, блок 1проверки условий вырабатывает управляюший сигнал на своем втором выходе,.поступаюший на счетный вход счетчика 6адреса, в котором к текущему ацресудобавляется единица,50Сигнал кода очередной микрокомандыс выхода регистра 11 поступает такжена дешифраторы 9, 10 и 13, причем, вслучае, если закодирована команда условного .перзхопа, то сигнал с выхоца цешифратора 4 через второй вхоп регистра 11микрокоманд поступает на его второй выхоп, откупа - на запрещающие входы дешифраторов 9, 12 и 13, прецотврашая 450 бих ложное срабатывание, Если в очередноймикрокоманде блоке 5 памяти закодирована команда перехода к станцартноймикропоцпрограмме, то срабатывает пешифратор 9 перехода к станцартной микропрограмме, сигнал которого поступает науправляющий вход регистра 8 адреса возврата и записывает в него текушее значе.ние .адреса в счетчике 6, а также поступает на установочный вход триггера 2 признака перехода и устанавливает его в состояние хранения признака перехода. Вслецуюшей ячейке блока 5 памяти микропрограммы кодируется микрокоманпа условного перехода в зависимости от состояния триггера 3 возврата. Вследствиетого, что триггер 3 находится в исхоаномсостоянии выполняется условный переходпо адресу начала стандартной микропоцпрограммы. В послецуюших микротактахвыполняется станпартная микропоапрограмма, в конце которой кодируется командаусловного перехопа по условию триггера 2перехода, Вследствие того, что триггер 2установлен в:режим хранения признакаперехода, выполняется переход к командевозвратаПри поступлении в регистр 11микрокоманд команды возврата срабатывают пешифраторы 4 и 10. При этом сигналом пешифратора 10 коммутатор 7 переводится р режим пропускания сигналаот регистра 8 адреса возврата, триггер 3устанавливается в режим хранения признака возврата, и выполняется безусловный переход по адресу регистра 8. Послеперехода к команде, адрес которой записанв регистре 8, эта команда повторяется,а после нее повторяется команца условного перехода по условию триггера 3 возврата, Вследствие того, что триггер 3установлен в режим хранения признакавозврата, поворотный переход к станцартной микропоппрогвмме не происходит, аустройство выполняет команду послевоэвратных операций, при поступлении которой в регистр 11 микрокоманц срабатывает дешифратор 13, выхоцной сигнал которого устанавливает триггеры 2 и 3 висходное состояние,Далее выполняется последующая частьмикропрограммы. Если стандартная микропоапрограмма выполняется не после пере.хопа из произвольного места микропрограммы, а в порядке своей очереци, то вее конце при выполнении команцы условного перехода по условию триггера 2 перехода последний оказывается в исходномсостоянии и поэтому переход к команцевозврата не выпопняетс.я, а выполняется7 1019450 8 очередная команда, следующая после стан- номией обьема памяти микропрограммы. партной микропопп рог раммы, Например, если стандартная микропоппрогЭффективность предлагаемого устройсв- рамма занимает 10% общего объема памява по сравнению с известным, которое Эти и встречается в микропрограмме ь раз, может быть принято в качестве базовогото предложенное й% то ц цложенное устройство позволяет обьекта, заключается в том, что оно поз- сократить треб ем й бьесок тить требуемый объем памяти в 2 воляет, используя только один блок памяти микропрограммы, выполнять переход Кроме того пере ороме того, переход к предложенной из любого ее места .к любому цругомуструктуре управления от классической участку, являющемуся стандартной микро ф двухуровневой, когда на более высоком подпрограммой, с послецующим возвратом уровне работает управляющая программа к исходному месту и тем самым при сокоторая в соответствующие моменты вре ставлении и отладке микропрограммы со- мени запускает микропрограммные автоставлять и отлаживать стандартные ее части только опии раз.маты, реализующие стандартные поцпрог15 раммы и являющиеся более низким уровнемТехническое преимушество такого ре- управления, позволяет существенно упрос- шения опрецеляется существенной эко- тить структуру устройства управления.О НИИПИ Заказ 3706/44 Тираж 706 ПодпиФилиал ПЛП "Патент, г. Ужгород, ул. Проектна

СмотретьЗаявка

3396678, 11.02.1982

ПРЕДПРИЯТИЕ ПЯ Г-4152

ГОРЮНОВА ЛЮДМИЛА МИХАЙЛОВНА, ДИДЕНКО ЛЮБОВЬ ПЕТРОВНА, ИВАНКИНА ТАМАРА ПЛАТОНОВНА, ИЦКОВИЧ ЮРИЙ СОЛОМОНОВИЧ, ПАРИЖСКИЙ ЮРИЙ СЕМЕНОВИЧ, ТИТОВА ИНЕССА НИКОЛАЕВНА, ФИЛИППОВ МИХАИЛ ЮРЬЕВИЧ, ЧУДИНОВА ГАЛИНА ИГОРЕВНА

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 23.05.1983

Код ссылки

<a href="https://patents.su/5-1019450-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для контроля электронной вычислительной машины

Случайный патент: Головка для магнитной звукозаписи