Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1509889

Авторы: Козюминский, Насимов

Текст

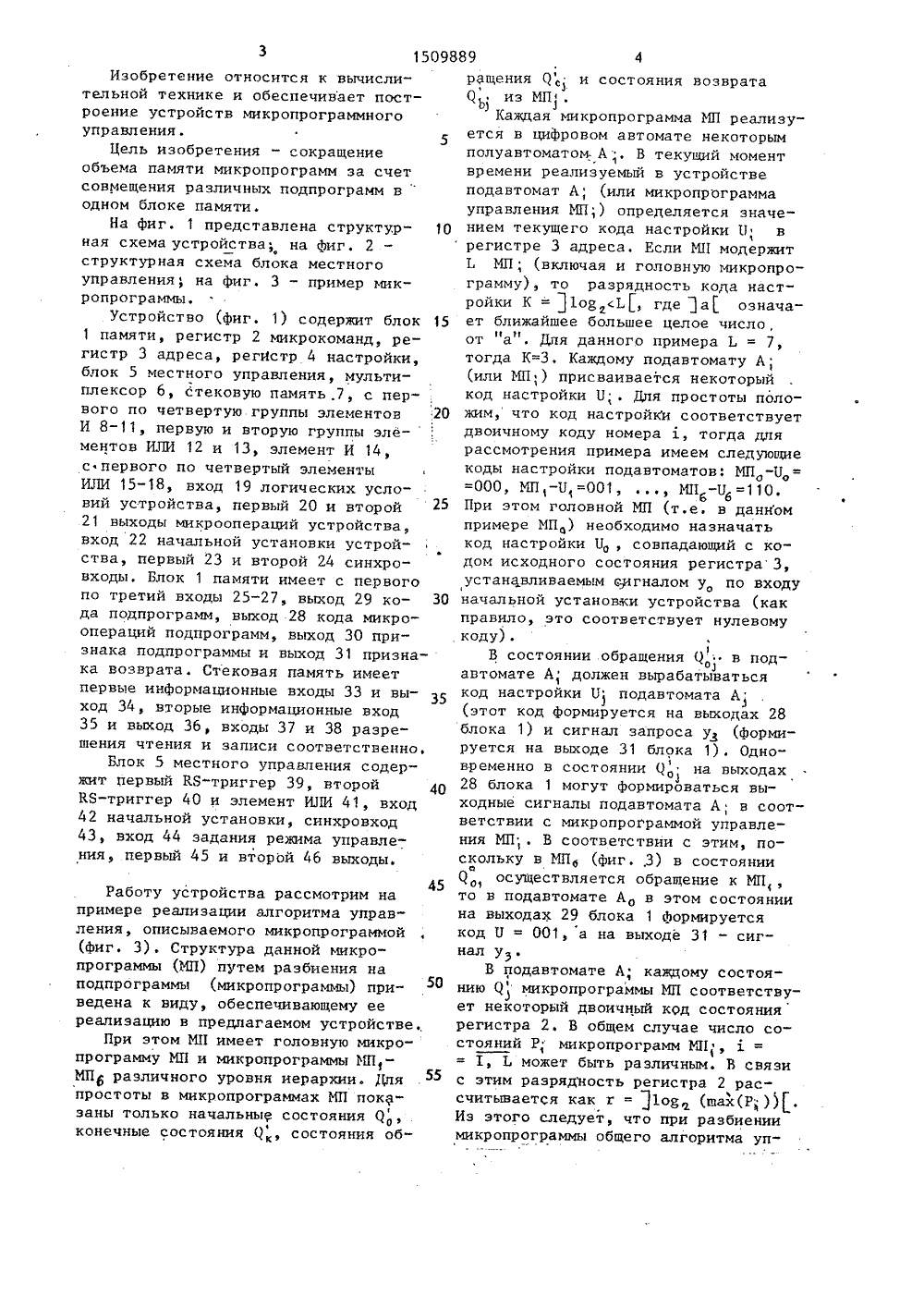

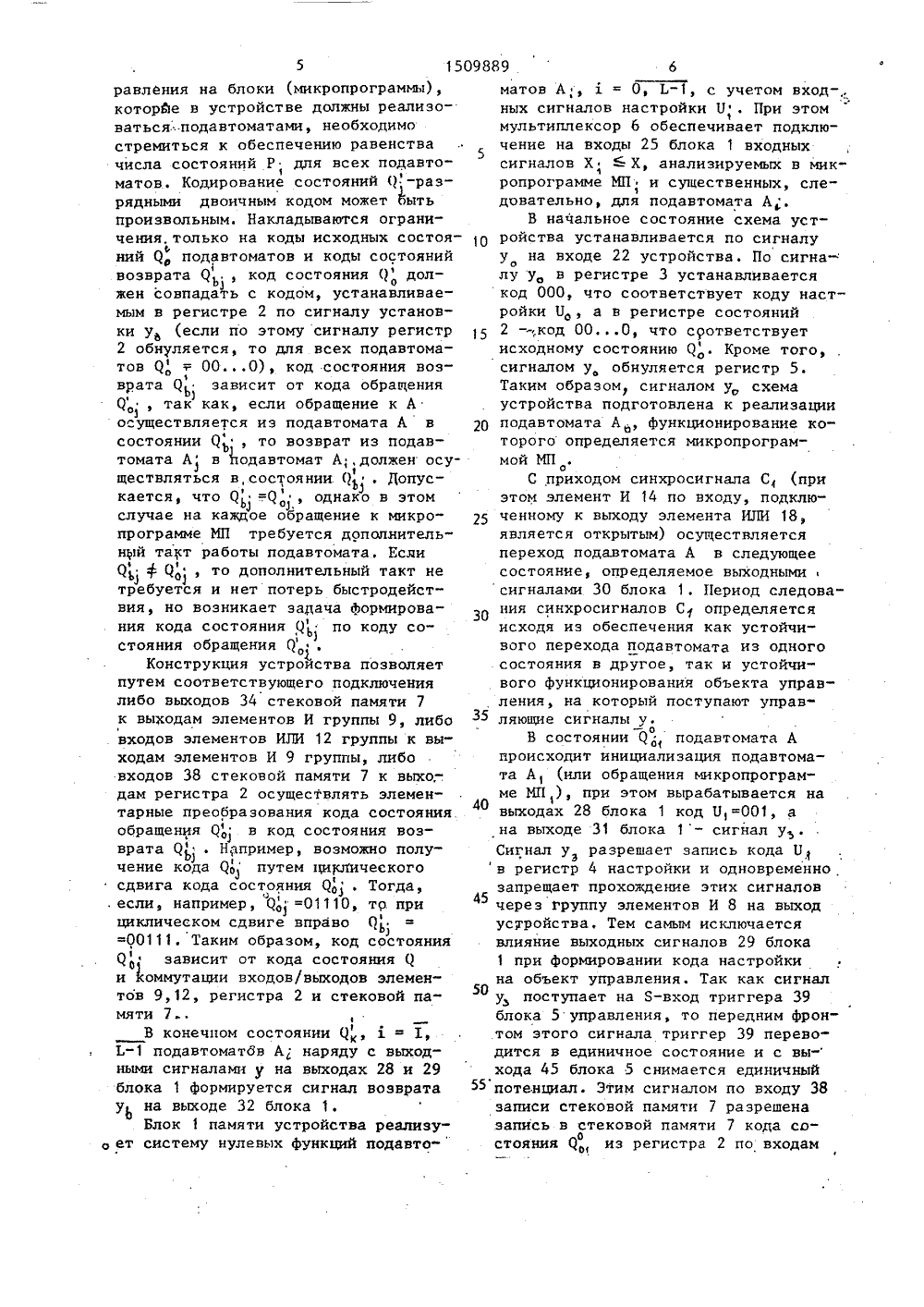

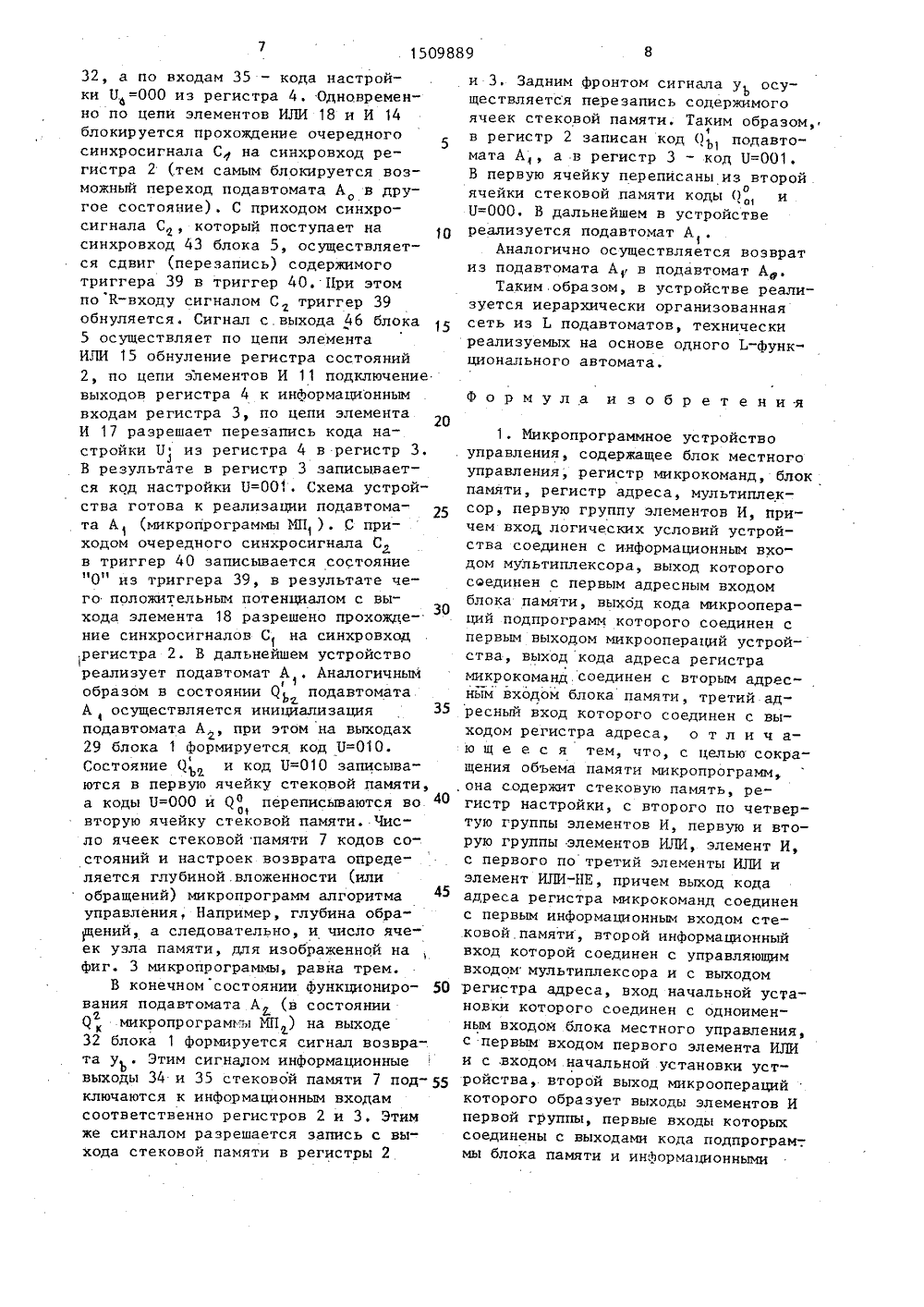

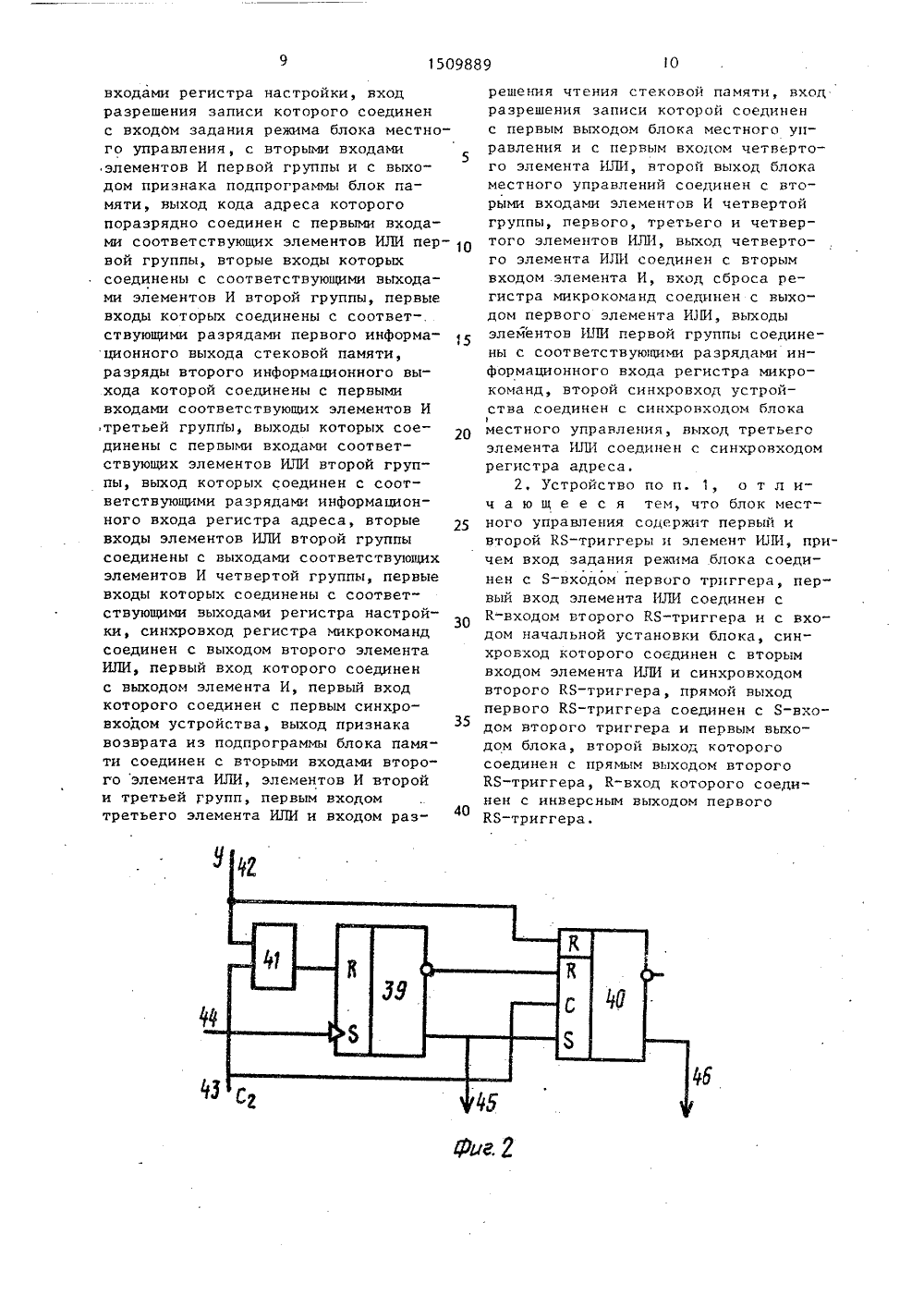

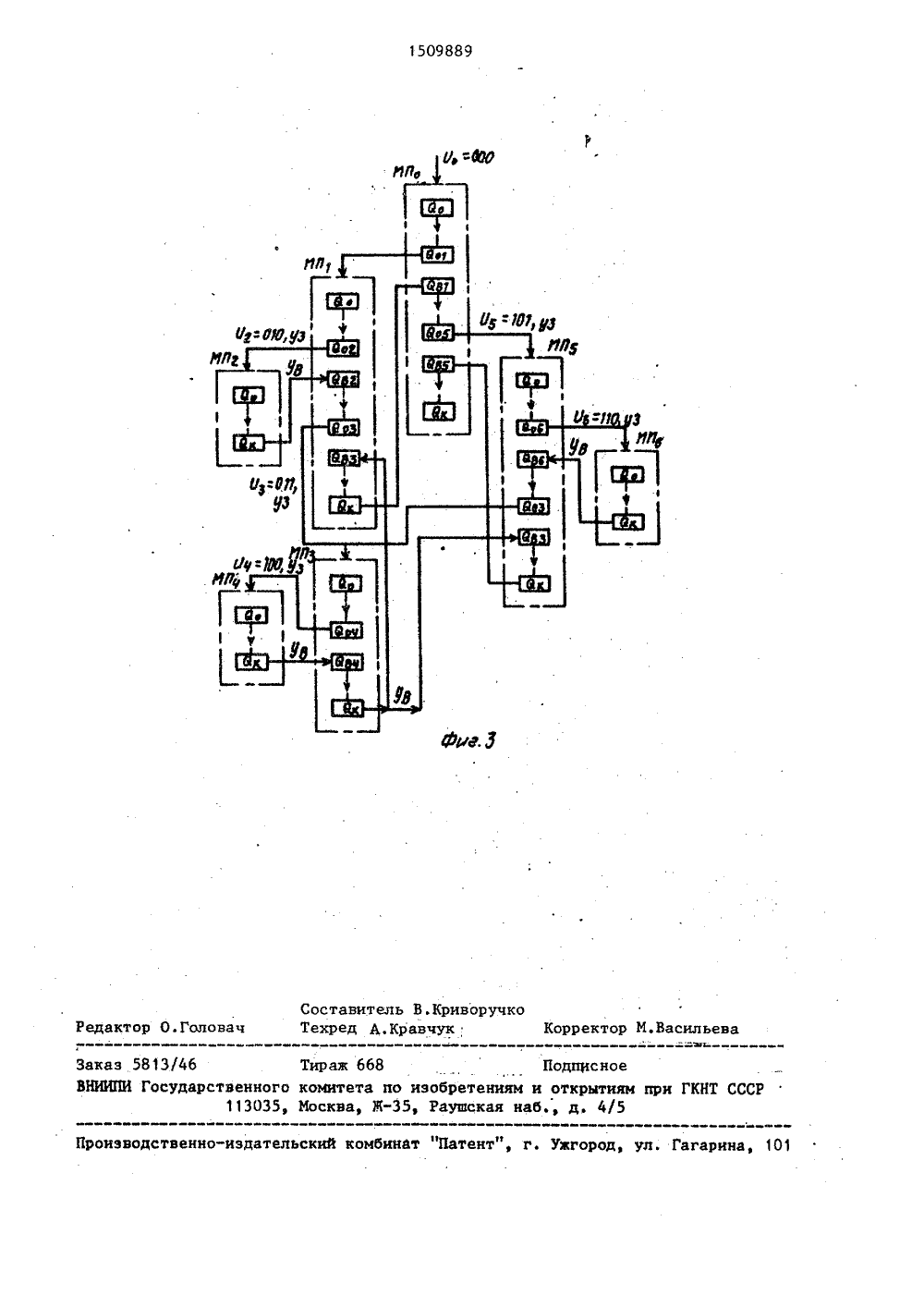

СОЮЗ СОВЕТСКИХ,СОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК А 1 06 Г 9(22 НИЯ У асимо ммируе М,. рис б. ОЕ УСТРОИСТБОносится к вычиможет быть исроении устрой ств ю гс фие.ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР ИСАНИЕ ИЗОБ АВТОРСКОМУ СВИДЕТЕЛЬ 121) 4313655/24-24(53) 681.3(088 .8)56) Авторское свидетельство СУ 1062701, кл. С Об Р 9(22, 1Баранов С.И., Скляров ВА.Цифровые устройства на програмых БИС с матричной структураРадио и связь, 1986, 2722.4,Авторское свидетельство ССН 1339558, кл. С 06 Р 9(00, 1(57), Изобретениелительиой техникепользовано при по ЯО 15098 управления и управляющих автоматов.Целью изобретения является сокращение объема памяти микропрограмм засчет совмещения различных подпрограмм в одном блоке памяти. Устройство содержит блок 1 памяти, регистр2 микрокомаид, регистр 3 адреса, регистр 4 настройки, блок 5 местногоуправления, мультиплексор 6, стековую память 7, с первой по четвертуюгруппы элементов И 8-11, первую 12и вторую 13 группы элементов ИЛИ,элемент И 14, с первого по четвертыйэлементы ИЛИ 15-18. Поставленнаяцель достигается тем, что в устройстве реализуется иерархически организованная сеть из 4 подавтоматон,реализуемых на основе одного 1.-Функ-ционального автомата, 1 з,п. А-лы,3Изобретение относится к вычислительной технике и обеспечивает построение устройств микропрограммного управления. 5Цель изобретения - сокращение объема памяти микропрограмм за счет совмещения различных подпрограмм в одном блоке памяти.На фиг. 1 представлена структур ная схема устройства; на фиг. 2 структурная схема блока местного управления, на фиг. 3 - пример микропрограммы.Устройство (фиг. 1) содержит блок 15 1 памяти, регистр 2 микрокоманд, регистр 3 адреса, регйстр 4 настройки, блок 5 местного управления, мультиплексор б, стековую память,7, с первого по четвертую группы элементов 20 И 8-11, первую и вторую группы элементов ИЛИ 12 и 13, элемент И спервого по четвертый элементы ИЛИ 15-18, вход 19 логических условий устройства, первый 20 и второй 21 выходы микроопераций устройства, вход 22 начальной установки устройства, первый 23 и второй 24 синхровходы, Блок 1 памяти имеет с первого по третий входы 25-27, выход 29 ко да подпрограмм, выход 28 кода микро- операций подпрограмм, выход 30 признака подпрограммы и выход 31 признака возврата. Стековая память имеет первые информационные входы 33 и выход 34, вторые информационные вход 35 и выход Зб, входы 37 и 38 разрешения чтения и записи соответственно,Блок 5 местного управления содержит первый КБ-триггер 39, второй 40 КБ-триггер 40 и элемент ИЛИ 41, вход 42 начальной установки, синхровход 43, вход 44 задания режима управления, первый 45 и второй 46 выходы.45Работу устройства рассмотрим на примере реализации алгоритма управления, описываемого микропрограммой (фиг, 3), Структура данной микропрограммы (МП) путем разбиения на подпрограммы (микропрограммы) приведена к виду, обеспечивающему ее реализацию в предлагаемом устройстве.,При этом МП имеет головную микропрограмму МП и микропрограммы МП- МП 6 различного уровня иерархии. Для простоты в микропрограммах МП показаны только начальные состояния Яо, конечные состояния , состояния обращения Й е и состояния возврата 0 МП, .)Каждая микропрограмма МП реализуется в цифровом автомате некоторым полуавтоматом- А, В текущий момент времени реализуемый в устройстве подавтомат А, (или микропрограмма управления МП;) определяется значением текущего кода настройки П в% регистре 3 адреса, Если МП модержит Ь МП(включая и головную микропрограмму), то разрядность кода настройки К = 11 оя Ь, где 1 а означает ближайшее большее целое число, от "а". Для данного примера Ь = 7, тогда К=З. Каждому подавтомату А; (или МП,) присваивается некоторый код настройки П,. Для простоты положим, что код настройки соответствует двоичному коду номера 1, тогда для рассмотрения примера имеем следующие коды настройки подавтоматов: МП -Ц,= -000, МП, П 001, , МП П 110, При этом головной МП (т.е. в данном примере МП) необходимо назначать код настройки П , совпадающий с кодом исходного состояния регистра 3, устанавливаемым сигналом у, по входуначальной установки устройства (как правило, это соответствует нулевому коду) .В состоянии обращения ( в подО 1 автомате А, должен вырабатываться код настройки П подавтомата А (этот код формируется на выходах 28 блока 1) и сигнал запроса у (формируется на выходе 31 блока 1). Одновременно в состоянии Цо на выходахО 128 блока 1 могут формироваться выходные сигналы подавтомата А, в соответствии с микропроГраммой управления МП;, В соответствии с этим, поскольку В МП (фиге,З) В состоянииосуществляется обращение к МП, то в подавтомате Ао в этом состоянии на выходах 29 блока 1 формируется код П = 001, а на выходе 31 - сигнал уреВ подавтомате А; каждому состояниюмикропрограммы МП соответствует некоторый двоичный код состояния регистра 2. В общем случае число состояний Р микропрограмм МП ь. =1, Ь может быть различным. В связи с этим разрядность регистра 2 рассчитывается как г = 1 оя (шах(Р).Из этого следует, что при разбиении микропрограммы общего алгоритма уп 5 15равления на блоки (микропрограммы),которйе в устройстве должны реализоватьсяподавтоматами, необходимостремиться к обеспечению равенствачисла состояний Р для всех подавтоматов. Кодирование состояний-разрядными двоичным кодом может бытьпроизвольным. Накладываются ограничения, только на коды исходных состояний Яо подавтоматов и коды состоянийвозврата Я,код состояниядоль,жен совпадать с кодом, устанавливаемым в регистре 2 по сигналу установки у (если по этому сигналу регистр2 обнуляется, то для всех подавтоматов Я - 000), код состояния воз 1врата Я зависит от кода обращенияЯ , так как, если обращение к А11о)осуществляется из подавтомата А всостоянии Я , то возврат из подавтомата А в подавтомат А,.должен осуществляться в, состоянии ( Допускается, что Я =.Я , однако в этомо), фслучае на каядое обращение к микропрограмме МП требуется дополнительнй такт работы подавтомата, Если0Цо, то дополнительный такт нетребуется и нет потерь быстродействия, но возникает задача формирования кода состояния Ц по коду со, Ь)стояния обращения оКонструкция устроиства позволяетпутем соответствующего подключениялибо выходов 34 стековой памяти 7к выходам элементов И группы 9, либовходов элементов ИЛИ 12 группы к выходам элементов И 9 группы, либовходов 38 стековой памяти 7 к выхо;.дам регистра 2 осуществлять элементарные преобразования кода состоянияобращения Я) в код состояния возврата О . Н 1 зпример, возможно получение кода Яо путем циническогосдвига кода состояния Яо . Тогда,. если, например, Яо 1 =01110, тр прициклическом сдвиге вправо О=00111, Таким образом, код состоянияЯ зависит от кода состояния Ци коммутации входов/выходов элементов 9,12, регистра 2 и стековой памяти 7В конечпом состоянии Ц, д = 1,Ьподавтоматдв А наряду с выходными сигналами у на выходах 28 и 29блока 1 формируется сигнал возвратау на выходе 32 блока 1,Блок 1 памяти устройства реализуо ет систему нулевых функций подавто 09889матов АО, 1.-1, с учетом вход-ных сигналов настройки П. При этоммультиплексор б обеспечивает подключение на входы 25 блока 1 входныхсигналов ХХ, анализируемых в мнк 1ропрограмме МП и существенных, следовательно, для подавтомата А;.В начальное состояние схема устройства устанавливается по сигналуу на входе 22 устройства. По сигна-лу у в регистре 3 устанавливаетсякод 000, что соответствует коду настройки По, а в регистре состояний2 =,код 000, что соответствуетисходному состоянию Ч. Кроме того,сигналом у, обнуляется регистр 5.Таким образом) сигналом у схемаустройства подготовлена к реализацииподавтомата А, функционирование которого определяется микропрограм"мой МПоС приходом синхросигнала С (приэтом элемент И 14 по входу, подключенному к выходу элемента ИЛИ 18,является открытым) осуществляетсяпереход подавтомата А в следующеесостояние, определяемое выходнымисигналами 30 блока 1. Период следования синхросигналов С( определяетсяисходя из обеспечения как устойчивого перехода подавтомата из одногосостояния в другое, так и устойчивого функционирования объекта управления, на который поступают управ ляющие сигналы у- оВ состоянии Я;, подавтомата Апроисходит инициализация подавтомата А (или обращения микропрограмме МП,), при этом вырабатывается навыходах 28 блока 1 код У=001, ана выходе 31 блока 1- сигнал у .Сигнал у разрешает запись кода 01в регистр 4 настройки и одновременнозапрещает прохождение этих сигналовчерез группу элементов И 8 на выходустройства, Тем самым исключаетсявлияние выходных сигналов 29 блока1 при формировании кода настройкина объект управления. Так как сигнал 50у поступает на Я-вход триггера 39блока 5 управления, то передним фронтом этого сигнала триггер 39 переводится в единичное состояние и с вы"хода 45 блока 5 снимается единичный 55 потенциал. Этим сигналом по входу 38записи стековой памяти 7 разрешена32, а по входам 35 - кода настройки Б =000 из регистра 4 . Одновременно по цепи элементов ИЛИ 18 и И 14 блокируется прохождение очередного синхросигнала С на синхровход регистра 2 (тем самым блокируется возможный переход подавтомата А в другое состояние), С приходом синхросигнала С , который поступает на синхровход 43 блока 5, осуществляется сдвиг (перезапись) содержимого триггера 39 в триггер 40.При этом поК-входу сигналом Сг триггер 39 обнуляется. Сигнал с выхода 46 блока 5 осуществляет по цепи элемента ИЛИ 15 обнуление регистра состояний 2, по цепи элементов И 11 подключение выходов регистра 4 к информационным входам регистра 3, по цепи элемента И 17 разрешает перезапись кода настройки Б из регистра 4 в регистр 3, В результате в регистр 3 записывается код настройки 0=001, Схема устройства готова к реализации подавтомата А (микропрограммы МП ), С при 1ходом очередного синхросигнала С в триггер 40 записывается состояние "0" из триггера 39, в результате чего положительным потенциалом с вы 30 хода элемента 18 разрешено прохождение синхросигналов С на синхровход ,регистра 2. В дальнейшем устройство реализует подавтомат А , Аналогичным1образом в состоянии ЯЪ подавтомата А, осуществляется инициализация 35 подавтомата А , при этом на выходах2 ф29 блока 1 формируется код 0=010. Состояние ъ и код 0=010 записываются в первую ячейку стековой памяти, а коды 0=000 и Я переписываются воо 40О 1вторую ячейку стековой памяти. Число ячеек стековой памяти 7 кодов состояний и настроек возврата опреде" ляется глубиной. вложенности (илиобращений) микропрограмм алгоритма45 управления, Например, глубина обра 1 щений, а следовательно, и число ячеек узла памяти, для изображенной на фиг. 3 микропрограммы, равна трем.В конечном состоянии функциониро" 50вания подавтомата Аг (в состоянии Цмикропрограммы МП ) на выходег32 блока 1 формируется сигнал возвра-.та уЪ. Этим сигналом информационныевыходы 34 и 35 стековой памяти 7 подключаются к информационным входамсоответственно регистров 2 и 3, Этимже сигналом разрешается запись с выхода стековой памяти в регистры 2 и 3. Задним фронтом сигнала у осуЪ ществляется перезапись содержимого ячеек стековой памяти. Таким образом,1 в регистр 2 записан код ОЪ подавто 1 мата А а в регистр 3 - код 0=001В первую ячейку переписаны из второй ячейки стековой памяти коды О и 0=000, В дальнейшем в устройстве реализуется подавтомат А,.Аналогично осуществляется возврат из подавтомата А в подавтомат А,Таким. образом, в устройстве реализуется иерархически организованная сеть из Ь подавтоматов, технически реализуемых на основе одного Ь-функционального автомата.Формула изобретения1. Микропрограммное устройство управления, содержащее блок местного управления, регистр микрокоманд, блок памяти, регистр адреса, мультиплексор, первую группу элементов И, причем вход, логических условий устройства соединен с информационным входом мультиплексора, выход которого соединен с первым адресным входом блока памяти, выход кода микроопераций подпрограмм которого соединен с первым выходом микроопераций устройства, выход кода адреса регистра микрокоманд.соединен с вторым адресным входом блока памяти, третий адресный вход которого соединен с выходом регистра адреса, о т л и ч аю щ е е с я тем, что, с целью сокращения объема памяти микропрограмм, она содержит стековую память, регистр настройки, с второго по четвертую группы элементов И, первую и вторую группы элементов ИЛИ, элемент И, с первого по третий элементы ИЛИ и элемент ИЛИ-НЕ, причем выход кода адреса регистра микрокоманд соединен с первым информационным входом стековой памяти, второй информационный вход которой соединен с управляющим входом мультиплексора и с выходом регистра адреса, вход начальной установки которого соединен с одноименным входом блока местного управления,с первым входом первого элемента ИЛИи с .входом .начальной установки устройства, второй выход микроопераций которого образует выходы элементов И первой группы, первые входы которых соединены с выходами кода подпрограм-. мы блока памяти и информационнымивходами регистра настройки, вход разрешения записи которого соединен с входом задания режима блока местного управления, с вторыми входами элементов И первой группы и с выходом признака подпрограммы блок памяти, выход кода адреса которого поразрядно соединен с первыми входами соответствующих элементов ИЛИ пер О вой группы, вторые входы которых соединены с соответствующими выходами элементов И второй группы, первые входы которых соединены с соответ-. ствующими разрядами первого информационного выхода стековой памяти, разряды второго информационного выхода которой соединены с первыми входами соответствующих элементов И третьей группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ второй группы, выход которых соединен с соответствующими разрядами информационного входа регистра адреса, вторые входы элементов ИЛИ второй группы соединены с выходами соответствующих элементов И четвертой группы, первые входы которых соединены с соответствующими выходами регистра настройки, синхровход регистра микрокоманд соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом элемента И, первый вход которого соединен с первым синхровходом устройства, выход признака возврата из подпрограммы блока памяти соединен с вторыми входами второго элемента ИЛИ, элементов И второй и третьей Групп, первым входом третьего элемента ИЛИ и входом раз 40 решения чтения стековой памяти, вход разрешения записи которой соединен с первым выходом блока местного управления и с первым входом четвертого элемента ИЛИ, второй выход блока местного управлений соединен с вторыми входами элементов И четвертой группы, первого, третьего и четвертого элементов ИЛИ, выход четвертого элемента ИЛИ соединен с вторым входом .элемента И, вход сброса регистра микрокоманд соединен с выходом первого элемента И 11 И, выходы элементов ИЛИ первой группы соединены с соответствующими разрядами информационного входа регистра микро- команд, второй синхровход устройства .соединен с синхровходом блока 1местного управления, выход третьего элемента ИЛИ соединен с синхровходомрегистра адреса.2, Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок местного управления содержит первый и второй КБ-триггеры и элемент ИЛИ, причем вход задания режима .блока соединен с Б-входом первого триггера, первый вход элемента ИЛИ соединен с К- входом второго КБ-триггера и с входом начальной установки блока, синхровход которого соединен с вторым входом элемента ИЛИ и синхровходом второго КБ-триггера, прямой выход первого КБ-триггера соединен с Б-входом второго триггера и первым выходом блока, второй выход которого соединен с прямым выходом второго КБ-триггера, К-вход которого соединен с инверсным выходом первого КБ-триггера.

СмотретьЗаявка

4313655, 06.10.1987

МИНСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

КОЗЮМИНСКИЙ ВАЛЕРИЙ ДМИТРИЕВИЧ, НАСИМОВ ВЛАДИМИР ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 23.09.1989

Код ссылки

<a href="https://patents.su/6-1509889-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для приоритетного распределения заданий

Следующий патент: Устройство для формирования структурированных файлов

Случайный патент: Контактная тарелка