Сумматор по модулю

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 855659

Автор: Червяков

Текст

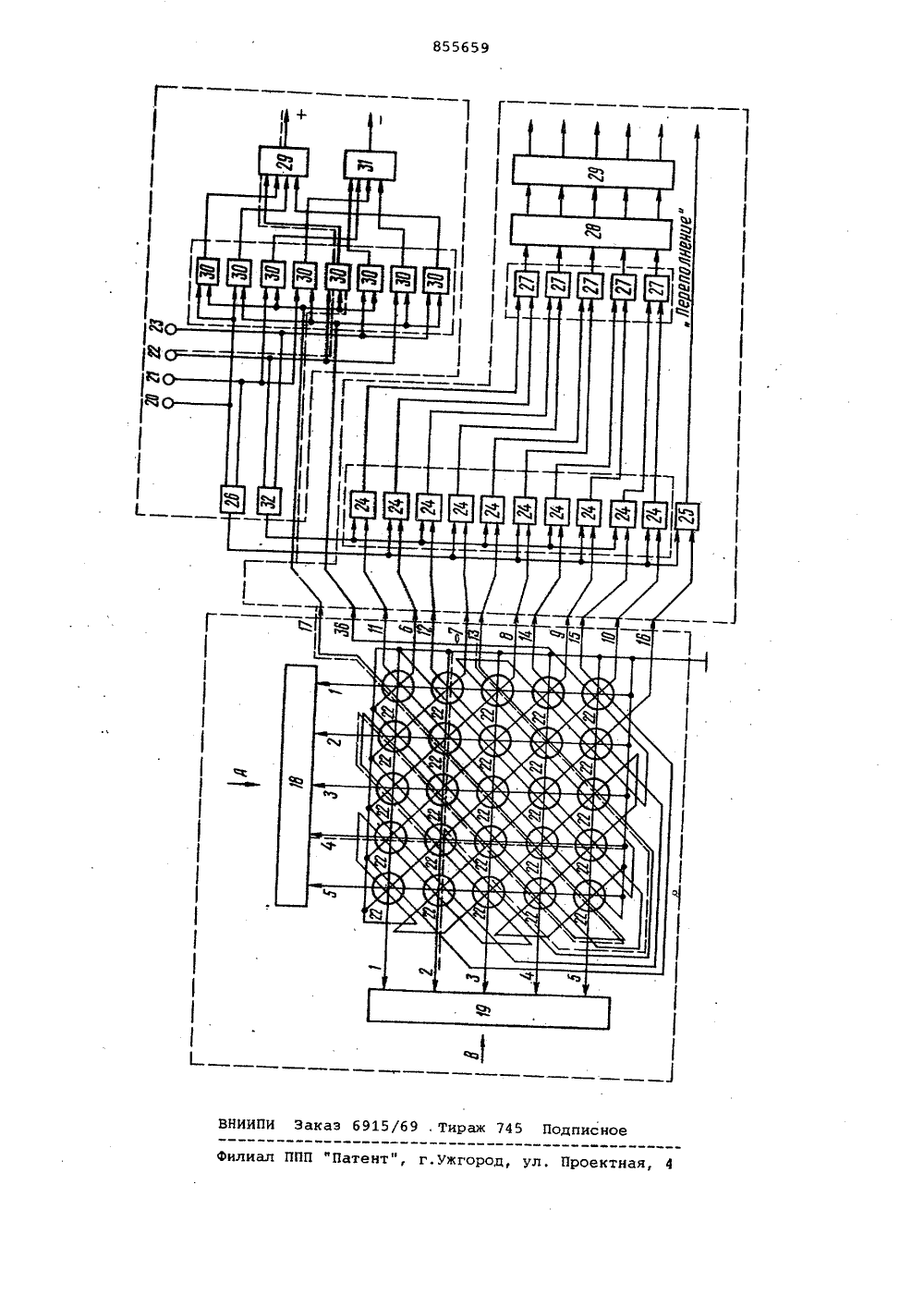

Союз Советских Соцмалистнческ их РеспубликОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ 1 ц 855659 61) нительное к авт. свнд-ву 1(5)М. Кл.з Заявлено 20,1179 (2 45176/18-2 присоединением заяв 6 Г 7/72 осударстаеиный комите СССР ио делам изобретений н открытий(23 Приорите Опубликована 15 Ю 881. Бюллетень ЙЯДата опубликования описания 15,08.81 53) УДК 681. 325.(71) Заявитель 54) СУММАТОР ПО диого и соот ового мы со ой др егист- тст- ердечинена ого 10 Для опо опреде- находитзнака зна я выполя чисел. ьхаение 5 редл стем на ф ЛИ,матр ерде 30 Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах и системах, работающих в непозиционных системах счисления, в системах контроля передачи дискретной информации и системах контроля работы вычислительных машин при построении сумматоров по произвольному модулю.Известен сумматор в системе остаточных классов, в котором вычитание заменяется сложением уменьшаемого с дополнением вычитаемого по модулю, содержащий позиционный и не- позиционный сумматоры, блок инвентирования кода, блок переполнения позиционного сумматора, группы элементов И и ИЛИ Г 11Однако необходимость перевода вычитаемого в дополнение по модулю сумматора значительно увеличивает время выполнения операции вычитания по сравнению с временем вы-. полнения сложения.Наиболее близким к п агаемому является сумматор в си е остаточных классов, содержащий два выходных регистра, операционный блок ( ицу), выполненный ерритовых с чниках,и элемент И причем каждая выходная шина о Рра через элемент ИЛИ вевующую обмотку феррит сника операционной схе едс каждой выходной шин угрегистра 2,Однако при представлении чиселв обобщенной искусственной формезнак скрыт в форме представлениячисел и нет воэможности визуальноопределить является ли оно положительньм или отрицательнымределения знака необходимлить интервал, в которомся число, Но определениечительно увеличивает времнения сложения и вычитаниЦель изобретения - повбыстродействия сумматора.Поставленная цель достигаетсятем, что сумматор содержит две группы элементов И, группу элементовИЛИ, элемент И, четыре элемента ИЛИ,выходной регистр, причем информационные выходы операционного блока соединены с первыми входами соответствующих элементов И первой группы, выходы каждых двух элементов И первойгруппы соединены со входами соответствующего элемента ИЛИ группы, вы 855659Формулй изобретения ходы элементов Или группы соединены со входами выходного регистра, выходы которого являются информационными выходами устройства, знаковыйвыхоц операционного блока соединенс первыми входами четных элементовИ второй группы, выход переполнения операционного блока соединен с первым входом элемента И, выход которого является выходом "Переполнения"устройства, первые входы первого ивторого элементов И второй группы соединены между собой и с первым входом первого элемента ИЛИ и являются входом "Операнды"Ф устройства,первые входы третьего и четвертогоэлемента И второй группы соединенымежду собой и со вторым входом первого элемента ИЛИ и являются входом "Операнды"-устроГства, первыевходы пятого и седьмого элементов Ивторой группы соединены между собойи с первым входом второго элементаИЛИ и являются входом "А+В"-устройства, первые входы шестого и восьмого элементов И второй группы соединены между собой и со вторым входом второго элемента ИЛИ и являютсявходом "А-В"+устройства, выходыпервого и второго элементов ИЛИсоединены со вторыми входами соответственно четных и нечетных элементов И первой группы, выходы первого, второго, четвертого и восьмого элементов И второй группы соединены со входами третьего элементаИЛИ, выход которого является выходом "Результат"+устройства, выходытретьего, четвертого, шестого и седьмого элементов И второй группы сое динены со входами четвертого элемента ИЛИ, выход которого является выходом "Результат"-устройства. На чертеже представлена блок-схема устройства.Устройство содержит входные обмотки 1-5 ферритовых сердечников, соответствующие остаткам чисел А и В по модулю пять, выходные обмотки 6-10 ферритовых сердечников результата суммы чисел при одинаковых знаках чисел А и В; выходные обмот" ки 11-15 ферритовых сердечников резу льтата суммы порядка при разных знаках порядков чисел А и В; выходнуюобмотку 16, вырабатывающую признакпереполнения при одинаковых знакахчисел А и В; выходную обмотку 17определения знака результата суммычисел при условии, что абсолютнаявеличина числа А больше, чем абсолютная величина числа В или при равенстве абсолютных величин чисел А и В; входные регистры 18 и 19 хранения соответственно чисел А и В в коде 1 из в; вход 20 "Операнды+", вход 21 Операнды-", вход 22 "А+В"; вход 23 "А-В+"; первую группу элементов И 24 для формирования зна 0 5 20 25 30 35 40 45 чения суммы чисел при разных и одинаковых знаках чисел; элемент И 25для формирования значения суммы чисел при одинаковых знаках чиселсигнал переполнения); первый элемент ИЛИ 26 для сборки сигналов,соответствующих одновременным знакам чисел А и В, группу элементовИЛИ 27 для сборки результатов сум-.мирования чисел при различных комбинациях знаков порядков; третий элемент ИЛИ 29 для сборки сигналов, соответствующих положительному. рвзультату; выходной регистр 28 результата суммирования чисел; вторую группу элементов И 30 для формирования знака результата суммирования чисел; четвертый элемент ИЛИ 31 для сборки сигналов, соответствующих отрицательному результату, второй элемент ИЛИ 32 для сборки сигналов, соответствующих разным знакам чисел А и В.Устройство работает следующим образом.При выполнении операции суммирования на регистры 18 и 19 заносят-, ся значения слагаемых в коде 1 из в, а знаки чисел по входам 20-23 поступают на элементы И 30 второй группы и первый и второй элементы ИЛИ 26 и 32. Одна из выходных шин (1-5) входных регистров 18 и 19 воз" буждена, что приводит к возбуждению одного вполне определенного ферритового сердечника. Каждый ферритовый сердечник имеет три выходные обмотки, сигналы с которых поступают на входы соответствующих элементов И. В зависимости от знаков чисел формируется результат суммирования, переполнение и знак результата суммирования, Результат суммирования чисел в коде 1 из а поступает на, выходной регистр 28, элементы ИЛИ 29 и 31 формируют знак результата, элемент И 25 - сигнал "Переполнение". Таким образом, выполнение операции суммирования по любому модулю осуществляется в один такт. Сумматор по модулю, содержащий два входных регистра, входы которых являются информационными входами сумматора и операционный блок, выполненный в виде ферритовой матрицы, инфоряациониые входы которого соединены с соответствующими выходами входных регистров, о т л и ч а ю - щ и й с я тем, что, с целью повышения быстродействия, он содержит две группы элементов И, группу элементов ИЛИ, элемент И, четыре элемента ИЛИ, выходной регистр, причем информационные выходы операционного блока соединены с первыми входамисоответствующих элементов И первой группы, выходы каждых двух элементов И первой группы соединены со входами соответствующего элемента ИЛИ группы, выходы элементов ИЛИ группы соединены со входами выходного регистра, выходы которого яв 5 ляются информационными выходами устройства, знаковый выход операционного блока соединен с первыми входами четных элементов И второй группы, выход переполнения операционного блока соединен с первым входом элемента И, выход которого являетсяивыходом "Переполнения устройства, первые входы первого и второго элементов И второй группы соединены между собой и с первым входом первого элемента ИЛИ и являются входом "Операнды+" устройства, первые входы третьего и четвертого элементов И второй группы соединены между со бой и со вторым входом первого элемента ИЛИ и являются входом "Операнды-" устройства, первые входы пятого и седьмого элементов И второй группы соединены между собой и с 25 первым входом второго элемента ИЛИ и являются входом "А+В-" устройства, первые входы шестого и восьмого элементов И второй группы соединены между собой и со вторым входом второго элемента ИЛИ и являются входом фА-В+" устройства, выходы первого и второго элементов ИЛИ соединены со вторыми входами соответственно четных и нечетных элементов И первой группы, выходы первого второго, четвертого и восьмого элементов И второй группы соединены со входами третьего элемента ИЛИ, выход которого является выходом "Результат+" устройства, выходы третьего четвертого, шестого и седьмого элементов И второй группы соединены со входамн четвертого элемента ИЛИ, выход которого является выходом "Результат-" устройства,/ Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР Р 570052, кл. 6 06 Г 7/50, 1977. 2. Авторское свидетельство СССР Р 377771, кл. 0 06 Г 7/50, 1973

СмотретьЗаявка

2845176, 20.11.1979

СТАВРОПОЛЬСКОЕ ВЫСШЕЕ ВОЕННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ СВЯЗИ ИМ. 60-ЛЕТИЯ ВЕЛИКОГО ОКТЯБРЯ

ЧЕРВЯКОВ НИКОЛАЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/72

Опубликовано: 15.08.1981

Код ссылки

<a href="https://patents.su/4-855659-summator-po-modulyu.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор по модулю</a>

Предыдущий патент: Цифровое устройство для вычисления функций

Следующий патент: Устройство для управления обменом

Случайный патент: Устройство для флоуресцентного рентгенорадиометрического анализа