Преобразователь кода грея в параллельный двоичный код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

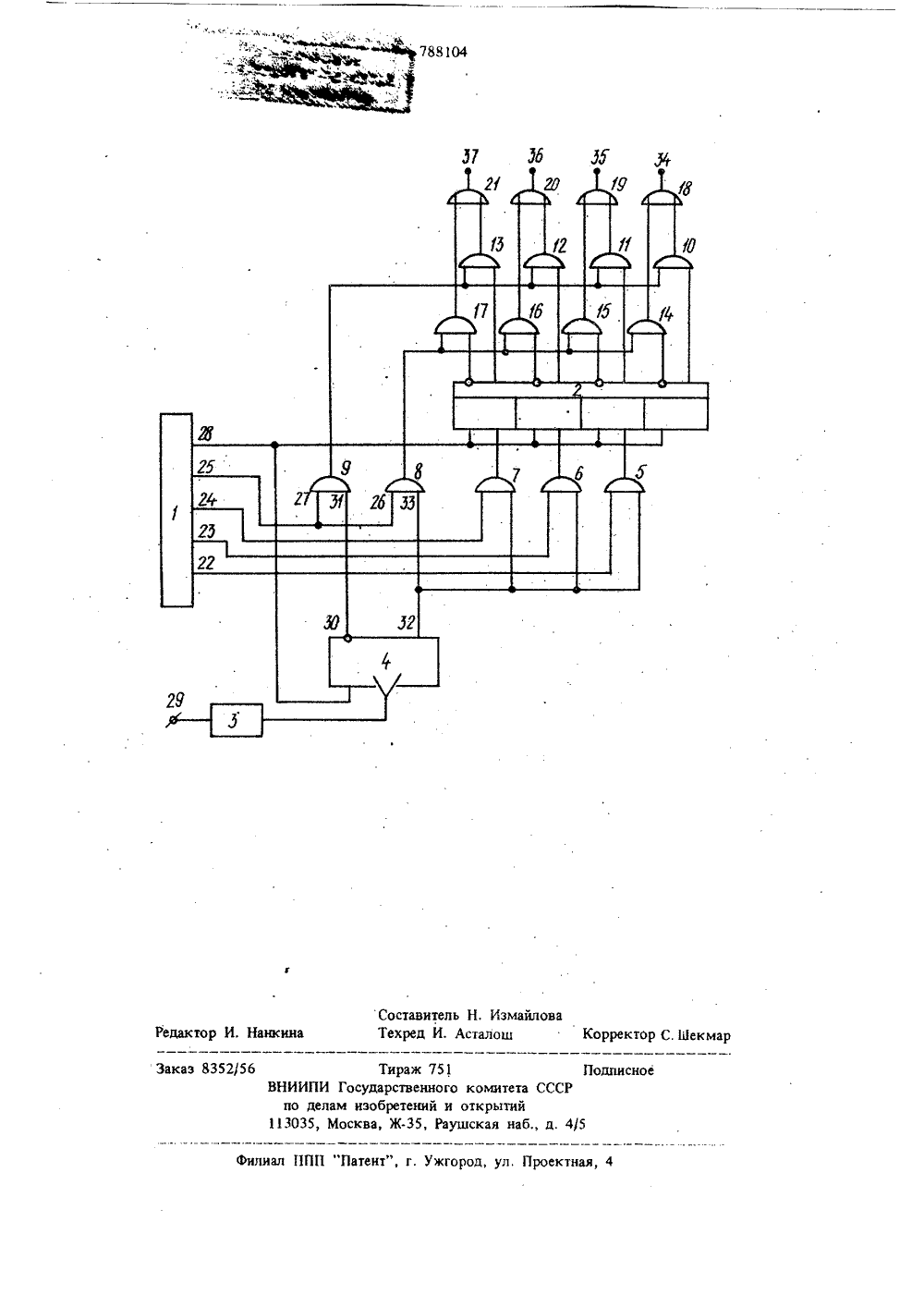

ОП ИСАИЗОБРЕТЕН ИЯ Н И Е О 1) 788104 Союз СоаетсннкСоцнвпнстнческнкРеспублнк К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ8) Приоритет 5,12.80,публикова ла делам изооретеии и открытий летеиь .% 4 53) УДК 681.3(71) мский авиационный институт им. Орджоник ель 54) Г 1 РЕОБРАЗОВАТЕЛЬ КОДА ГРЕ В ПАРАЛ 31 ЕЛЬНЫЙ ДВОИЧНЫЙ тветст- устройнам выдачи дво о код асляется ействие,пление быстм, что вельный литель ационроме Изобретение о;косит:.л к устройствам автоматики и вычислительной техники, а более конкретно к преобразователям кодов, и может быть использовано при построении цифровых следящих систем, в цели обратной связи кото 5 рых используется преобразователь типа перемещение-код.Известен преобразователь кода Грея в двоичный код, содержащий сдвигающий регистр, триггер счета, элемент И, распределитель и ячейку запрета И).Недостатком известного преобразователя является низкое быстродействие.Наиболее близким к предлагаемому является преобразователь кода Грея, содержащий р пределитель, выходной регистр, входные поразрядные элементы И, выходы которых подключены к соответствующ 1 входам установки "1" выходного регистра, выходные поразряд. ные схемы И, входы которых соединены с еди- о ничными выходами соответствующих разрядов выходного регистра, дополнительный элемент И, триггер счета, элемент задержки, вход ко. торого соединен с шиной подачи кода Грея,а выход - со счетным входом триггера счета, причем управляющие выходы распределителя соединены со входами входных поразрядных элементов И, со входом дополнительного элемента И, со входами всех выходных поразрядныхэлементов И исо входами установки "0" всехразрядов. выходного регистра, единичный выходтриггера счета соединен со входом дополнительного элемента И и со входами входных поразрядных элементов И, выход дополнительного элемента И соединен со счетными входами всех разрядов одного регистра, а выходы выходнь ядных элементов И подключены к свующим ши ичнства.2.Недостатком устройства явносительно невысокое быстроЦель изобретения - повь ствия преобразователя.Поставленная цель достигаетсяпреобразователь кода Грея в параллдвоичный код, содержащий распредна и выходов, выходной регистр,ные входы всех разрядов которого3 788 0младшего, подключены к выходам элементовИ входной группы, первые входы которыхобъединены и подключены к прямому выходулетного триггера, счетный вход которого через элемент задержки подключен ко входу5преобразователя, п.ный выход распределителяподключен к управляющим входам выходногорегистра, вторые входы элементов И входнойгруппы подключены к соответствующим, выхо.дам распределителя, первый дополнительньа10элемент И, первый вход которого соединенс (и)-м выходом распределителя, а второйвход - с единичным выходом счетного триггера,первые входы элементов И первой выход.ной, группы соединены с единичными выходами1соответствующих разрядов выходного регистра,введены вторая выходная группа элементов И,первые входы которых соединены с нулевымивыходами соответствующих разрядов выходного. регистра, второй дополнительный элемент И,первый вход которого соединен с первым вхо 20дом первого дополнительного элемента И, авторой вход подключен к нулевому выходусчетного триггера, управляющий вход которогоподключен к и-му выходу распределителя, вто 25рые входы элементов И первой и второй выходных групп объединены и подключены к выходам соответственно второго и первого дополнительных элементов И, первые входы элементовИЛИ группы подключены к выходам соответствующих элементов И выходной группы, вторыевходы - к выходам соответствующих элементов И первой выходкой группы, а выходы элементов ИЛИ группы являются выходами преобразователяБлок-схема предлагаемого устройства приве. З 5дена на чертеже. Устройство содержит распределитель 1, выходной регистр 2, элемент 3 задержки, счетный триггер 4, входные блоки элементов И старших ф(2 разрядов 5 - 7 (входной элемент И младшего разряда отсутствует), первый 8 и второй 9 дополнительные элементы И, выходные 10 - 13 и добавочные 14 - 17 блоки элементов И и поразрядные элементы ИЛИ 18 - 21. Управляющие выходы 22 - 24 распределителя 1 соединены соот. ветственио со входами входных блоков элементов И 5 - 7, уцравляющий выход 25 соединен со входом 26 первого 8 и со входом 27 второго 9 дополнительных элементов И, а управляющий выход 28 распределителя 1 подключен ко входам установки "0" всех разрядов выход. ного регистра 2 и ко входу установки "0" триг. гера 4 счета. Вход элемента 3 задержки, соединен с шиной 29 подаю кода Грея, а выход - со счетным входом счетного триггера 4. Нулевой выход 30 счетного триггера 4 подключен ко входу 31 второго дополнительного элемента И 9, а единичный выход 32 счетного триггера 4 -4 4ко входу 33 первого дополнительного элементаИ 8 и ко входам всех входных блоков элементов И 5 - 7, Выходы входных блоков элементовИ 5 - 7 соединены со входами установки "1"соответствующих разрядов выходного регистра 2,Единичные выходы всех разрядов выходного ре.гистра 2 соединены со входами соответствующихвыходных элементов И 10 - 13, а нулевые выходы всех разрядов выходного регистра 2 -со входами соответствующих добавочных элементов И 14 - 17. Выход первого дополнительногоэлемента И 8 подключен ко входам всех доба.вочных элементов И 14 - 17, а выход второгодополнительного элемента И 9 - ко входам всехвыходных блоков элементов И 10 - 13. Выходывыходных блоков элементов И 10 - 13 и выходы добавочных элементов И 14 - 17 через соот.ветствующие поразрядные элементы ИЛИ 18-21подключены к шинам 34 - 37 выдачи двоичногокода устройства. Устройство работает следующим образом, В первом такте на выходе 28 распределителя 1 появляется импульс, устанавливающий все триггеры выходного регистра 2, а также триггер 4 счета в исходное нулевое состояние. Одно. временно с этим импульсом с шины 29 на вход элемента 3 задержки поступает сигнал, соответ. ствующий первому (младшему) разряду кода Грея: задержка его поступления на счетный вход триггера 4 счета не превышает периода следования тактовых импульсов с распределителя 1, т,е. кодовые сигналы поступают на счетный вход триггера 4 счета в промежутках между подачей импульсов с распределителя 1, После прохождения элемента 3 задержки сигнал, соответствующий первому разряду кода Грея, появляется на счетном входе триггера 4. Затем на вход блока 5 подается второй тактовый импульс с выхода 22 распределителя 1. Одновременно с ним на вход элемента 3 задержки приходит сиг. нал, соответствующий второму разряду кода Грея. Импульсом второго такта с выхода 22 через блок 5 во второй разряд регистра 2 записы. вается состояние триггера 4, вызванное приходом на его счетный вход сигнала первого (младше. го) разряда кода Грея (триггер младшего разряда регистра 2" всегда находится в нулевом состоянии). После этой записи на счетном входе триггера 4 появляется сигнал, соответствующий второму разряду кода Грея (уже прошедший через элемент 3 задержки). Состояние триггера 4 счета, Вызванное действием этого сигнала, им. пульсом третьего такта с выхода 23 через блок 6 записывается в третий разряд регистра 2. Одновременно с импульсом третьего такта на вход элемента 3 задержки поступает сигнал, соответствующий третьему разряду кода Грея. 1 ройдя элемент 3 задержки, данный си(нал появляется на счетном входе триггера 4 счета (ос 1 олние788104 последнего, вызванное появлением на его счетном входе сигнала третьего разряда, импульсомчетвертого такта с выхода 24 через блок 7 записывается в четвертый разряд регистра 2. Одновременно с импульсом четвертого такта на входэлемента 3 задержки поступает сигнал, соответствующий четвертому (старшему) разряду кодаГрея. Пройдя через элемент 3 задержки, данныйсигнал появляется на счетном входе триггера 4счета. После этого с выхода 25 распределителя1 на входы 26 и 27 элементов 8 и 9 подаетсяпятый (последний) тактовый импульс, Если кэтому времени триггер 4 счета хранит "0" (чтопредставляет собой результат сложения по модулю два всех разрядов кода Грея), то задействуетего выход 30 и срабатывает элемент И 9. Возникающий на выходе последнего сигнал поступает.на входы выходных элементов И 10 - 13, в результате чего через поразрядные элементы ИЛИ18 - 21 на шины 34 - 37 проходит прямой код 2 Очисла, записанного в регистре 2 (т,е. на шины34 - 37 поступают сигналы с единичных выходоврегистра 2). Если же к моменту поступленияпятого тактового импульса с распределителя 1триггера 4 счета хранит "1" (что представляет 2 чсобой результат сложения по модулю два всехразрядов кода Грея), то задействует его выход32 и србатывает элемент И 8. Возникающийна выходе последнего сигнал поступает на входыдобавочных элементов И 14 - 17, в результате че. рго через поразрядные элементы ИЛИ 18 - 21 нашины 34 - 37 проходит обратный код числа, записанного в регистре 2 (т,е, на шины 34 - 37 по.ступают сигналы с нулевых выходов разрядоврегистра 2),С шин 34 - 37 полученный параллельный двоичный код может быть подан на другое уст 1 эойство, например на вход вычислительной машины.Таким образом, в предлагаемом устройстведля преобразования и-разрядного кода Грея впараллельный двоичный код требуется всего(и + 1) такт (т.е. (и + 1) временный интервал,что на два такта меньше, чем в известной схеме. Это достигается тем, что в предлагаемомпреобразователе исключен такт инвертирования45содержимого регистра 2, а также совмещениеммомента подачи первого (младшего) разряда кодаГрея с первым тактом (с тактом установки ре.гистра 2 в исходное нулевое состояние), В итоге увеличивается быстродействие преобраэовате.%0ля кода Грея в параллельный двоичный код. ьФормула изобретения Преобразователь кода Грея в параллельный двоичный код, содержащий распределитель на и выходов, выходной регистр, информационные входы всех разрядов которого, кроме младше. го, подключены к выходам элементов И входной группы, первые входы которых объедине. ны и подключены к прямому выходу счетного триггера, счетный вход которого через элемент задержки подключен ко входу преобразователя, п.ный выход распределителя подключен к управляющим входам выходного регистра, вторые входы элементов И входной группы подключе. ны к соответствующим выходам распределителя, первый дополнительный элемент И, первый вход которого соединен с (п).м выходом распределителя, а второй вход - с единичным выходом счетного триггера, первые входы элементов И первой выходной группы соединены с единич. ными выходами соответствующих разрядов выходного регистра, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия в него введены вторая выходная группа эле. ментов И, первые входы которых соединены с нулевыми выходами соответствующих раэря. дов выходного регистра, второй дополнительный элемент И, первый вход которого соеди. нен с первым входом первого дополнительного элемента И, а второй вход подключен к нуле. вому выходу счетного триггера, управляющий вход которого подключен к и-му выходу рас. пределителя, вторые входы элементов И первой и второй выходных групп объединены и под. ключены к выходам соответственно второго и первого дополнительных элементов И, первые входы элементов ИЛИ группы подключены к выходам соответствующих элементов И второй выходной группы, вторые входы - к выходам соответствующих элементов И первой выход. ной группы, а выходы элементов ИЛИ группы являются выходами преобразователя. Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР Мф 193787,кл. б 06 Р 5/02, 18.02.66. 2. Авторское свидетельство СССР Иф 431512,кл. 6 06 Е 5/02, 22.08,72 (прототип).И. Нанк Корректор С. Иекмар каз 8352/56 Тираж 751 одписное Филиал ППП "Патент", г. Ужгород, ул, Проекты НИИПИ по де 3035,Составитель Н, ИзмайлоТехред И, Асталош сударственного комитета СССРизобретений и открытийква, Ж-З 5, Раушская набд, 4/5

СмотретьЗаявка

2635249, 28.06.1978

УФИМСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ ИМ. ОРДЖОНИКИДЗЕ

ЗАРИПОВ МАДИЯР ФАХРИТДИНОВИЧ, ГАФАРОВ ЗИКАФ МИДХАТОВИЧ, РАХИМОВ БУЛАТ ЭНВЕРОВИЧ, ЩЕГЛОВ АЛЕКСАНДР НИКОЛАЕВИЧ, ТУХВАТШИН ОЛЕГ КУРЯШОВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: грея, двоичный, код, кода, параллельный

Опубликовано: 15.12.1980

Код ссылки

<a href="https://patents.su/4-788104-preobrazovatel-koda-greya-v-parallelnyjj-dvoichnyjj-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь кода грея в параллельный двоичный код</a>

Предыдущий патент: Генератор псевдослучайной последовательности

Следующий патент: Операционное устройство для суммирования произведений двух массивов чисел

Случайный патент: 416819