Формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 750701

Автор: Бондаренко

Текст

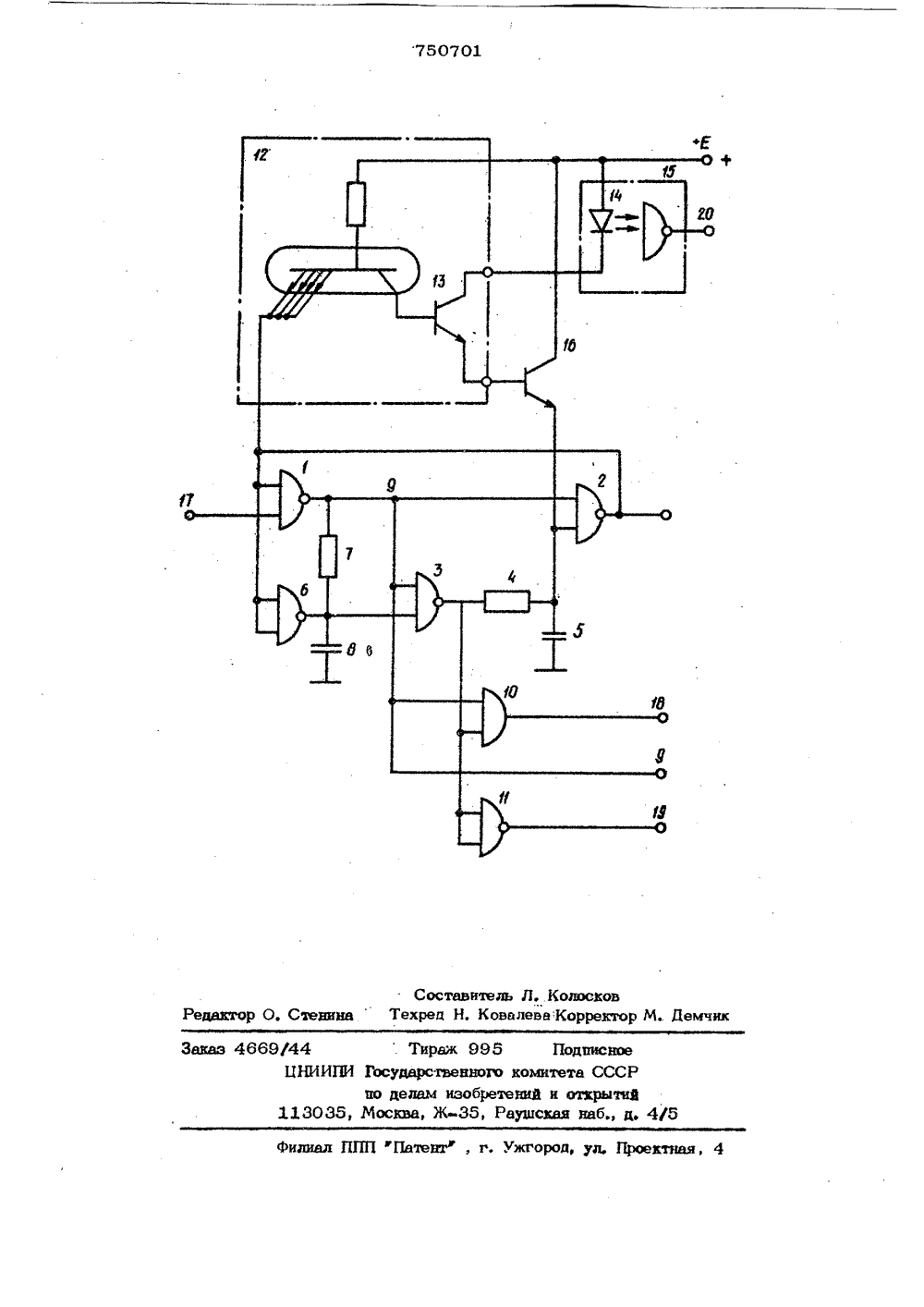

Согоз СоветскихСоцнапистнчесннхРеспубпнк оц 750701ио дилан изабретеиий и открытий(54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВИзобретение относится к импульснойтехнике и может быть использовано в различных цифровых устройствах и устройсъвах дискретной автоматики,Известен формирователь импульсов, содержащий триггер, выполненный на вентц"лях ТТЛ И-НЕ, вход которого через времязадающую цепь соединен с выходом ло. гического элемента И-НЕ, охваченного. через резисторный делитель отрицательной обратной связи, вхоч которого черездиод подключен к единичному выходу тритгера Я Однако время восстановлениятаких формирователей велико, так как после возвращения триггера в заданное устой 15чивое состояние заряд времязадающегоконденсатора происходит в основном через эквивалентное сопротивление в колжкторнрй ден выходного транзистора логического элемента и связанного с нимвремязадавщего резистора,Наиболее близким по ртношещпо к пред- .ложенному устройству яваяется формнроЯватель импульсов, содержащий триггер на 2элементах И-НЕ, вход которого соединенчерез времязадающую цепь с выходом логического элемента И-НЕ, один вход которого соединен с единичным выходом триггера непосредственно, а другой - черездополнительную интегрирукицую цель 12 )Однако такой формироватег; также имеетбольшое время восстановления из за того,что разряд конденсатора дополнительнойинтегрирующей цепи и заряд конденсаторавремизадаюшей цепи проходит через резисторы, величина которых тем больше, чем,больше длнтепьность, которые необходимоформировать.Кроме того, перечисленные устройстване обладают расширенными функциональными возможностями.Цель изобретения - уменьшение времени восстановления устройства и раапирениеего фунщиональных возможностей,Указанная цель достигается за счет того, что в формировател импульсов, содержащий триггер на элемеатах И-НЕ, первый вход которого соединен через время7507задающую цепь с выходомлогического элемента И-НЕ, один вход которого соединенс единичным выходом триггера непосредственно, а другой - через интегрирующую цепьвведены логический элемент И-НЕ со свободным коллектором, расширитель числавходов ИЛИ,г Р - о -транзистор, инвертор,логический элемент И иоптронн й ииверторпереключатель, при этом нулевой выходтриггера соединен через логический элемент И-НЕ со свободным коллектором свыходом интегрирующей цепи и подключен ко входам расширителя числа входовИЛИ, в коллекторной цепи выходного транзистора которого включен излучавший диод оптронн ого инвертора-переключателя,анодом подключенный к источнику питания и коллектору о- р-отранзистора,база которого соединена с эмиттером выходного транзистора расширителя числа 20входов ИЛИ, а эмиттер - к первому входу триггера, причем один выход логического элемента И соединен с выходом логического элемента И-НЕ и входом инвертора, а второй его вход соединен с 25единичным выходом триггера,На чертеже представлена принципиальная схема предлагаемого формирователя импульсов.30формирователь импульсов, выполненныйна логических элементах, содержи триггер на элементах И-НЕ 1, 2, охваченных перекрестными связями; единичный. выход триггера соединен со своим первым входом35 через последовательно сОединенные логический элемент И-НЕ 3 и времяэадающую цепь, состоящую из резистора 4 и конденсатора 5. Нулевой выход триггера соединен с входами логического элемента И-НЕ 6,40свободный коллектор которого подключен к выходу интегрирующей пепи, состоящей из резистора 7 и конденсатора 8, и одному из входов логического элемента И-НЕ 3, второй вход которого соединен с единич 45 ным выходом 9 триггера и одним из входов логического элемента И 10, второй .вход которого соединен с выходом логического элемента 3 и входами инвертора 11, Нулевой выход триггера соединен также50 с входамирасширителя числа входов ИЛИ 12, в коллекторной цепи выходного транзистора 13 которого включен излучающий диод 14 оптронного инвертора-переключателя 15 анод которого подключен к источ 155 нику питания и коллектору о-р-й,транзистора 16, база которого соединена с эмиттером. транзистора 13, а эмиттер - с первым входом триггера. 01 фСхема работает следующим образом.В исходном состоянии на сигнальныйвход 17 триггера подается положительный потенциал. При этом на единичном инулевом выходах тригРэра действуют соответственно низкий и высокий уровни напряжения, Под действием высокого уровнянапряжения на нулевом выходе триггеравыходной транзистор 13 расширителя числа входов ИЛИ и о -рЪ-транзистор 16,а также выходной транзистор логическогоэлемента 6 открыты и насыщены. Приэтом конденсатор 5 заряжен практически,до напряжения источника питания, Конденсатор 8 разряжен через насыщенный выходной транзистор логического элемента 6.На выходах 18 и 19 действуют низкие(нулевые) уровни напрякения. На выходе20 оптронного инвертора-переключателя15 действует высокий уровень напряжения,При поступлении отрицательного импульса на сигнальный вход 17 триггера последний переходит в противоположное состояние характеризуемое логической "единицейф на единичном выходе триггера и логическим нулем" - на нулевом. При этом транзистор 16 и выходной транзистор логического элемента 6 скачкообразно закрываются и в дальнейшем, в тече ние всего времени квазиустойчивого равновесия, на работу схемы не оказывают никакого влияния. Под действием высокого уровня напряжения на единичном выходе триггера происходит заряд конденсатора 8 через резистор 7 и сопротивление в цепи коллектора выходного транзистора логического элемента 1, Через время, задаваемое интегрирующей цепью, напряжение на нем достигает порога срабатывания элемента 3. В результате воздействия высоких уровней напряжения на обоих входах логического элемента З.на его выходе устанавливается уровень логического "нуляф Конденсатор 5, заряженный через насыщенный транзистор 16 практически до уровня напряжения питания, начинает разряжаться через резистор 4 и сопротивление промежутка колжктор-эмиттер выходного транзистора логического элемента 3. Через время, определяемое времязадающей цепью, напряжение на конденсаторе 5 достигает порога срабатывания элемента 2 и триггер возвратится в исходное состояние, заканчивая формированиеимпульса.Под воздействием высокого уровня напряжения на нулевом выходе триггера зарядный транзистор 16 и выходной тран5 7507 зистор логического элемента 6 открываются и насыщаются. При этом конденсатор 8 разряжается через сопротивление участка коллектор-эмиттер насыщенного выходного транзистора элемента 6, а конденсатор 5 бьв.тро дозаряжается через насыщенный зарядный транзистор 16. В момент заряда конденсатора 5 через излучающий диод 14 протекает ток дозаряда, возбуждающий оптронный инвертор-переключатель, на выходе 20 которого формируется короткий отрицательный импульсконец формирования.Таким образом, применение устройства форсированного дозаряда одного из время задающих конденсаторов и принудительный разряд другого позволяет уменьшить время восстановжния устройства, Кроме того, всждствие того, что конденсатор 5 удается дозарядить до более высокого уровня (по сравнению с прототипом) длительность формируемого импульса автоматически увеличивается.Предложенный формирователь импульсов25 обладает расширенными функциональными возможностями, так как позволяет дополнительно формировать импульс конец формированияф, а такжеположительные импульсы различной длительности; снимаемый с выхода 18 логического элемента 10, и снимаемый с выхода 19 логического элемента 11.формула изобретенияФормирователь импульсов, содержащий триггер на элементах И-НЕ, первый вход35 которого соединен через времяэадаюшую 01 6цепь с выходом логического эжмента И-НЕ, один вход которого соединен с еди-ничным выходом триггера непосредственно, а другой - через интегрирующую петь, о т л и ч а ю ш и й с я тем, чтс,сцельюуменьшения времени восстановления и расширения функциональных воэможностей устройства, в него введены логический элемент И-НЕ со свободным колжктором, расширитель числа входов ИЛИ, о-р-отранзистор, инвертор, логический элемент И и оптронный инвертор-переключатель, при этом нулевой выход триггера соединен через логический эжмент И-НЕ ео свободным коллектором с выходом интегрируюшей цепи и подключен ко входам расширителя числа входов ИЛИ, в коллекторной цепи выходного транзистора которого включен излучающий диод оптронного ии вертора-переключателя, анодом подключенный к источнику питания и коллектору - -ртранзистора, база которого соединена с эмиттером выходного транзистора расширителя числа входов ИЛИ, а эмиттер - к первому входу триггера, причем один вход логического элемента И соединен с выходом логического элемента И-НЕ и входом инвертора, а второй его вход со едйПвн с единичным выходом триггера. Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР В 539367, кл. Н 03 К 3/284, 1975. 2. Авторское свидетельство СССР М 487449, кл. Н 03 К 3/28, 1974.750701 Составитель Л, КолосковО. СеменинаТехред Н, Ковалева:Корректор М Демчик Редакто илиал ППП фПатентф, г, Ужгород, у Я 4 . Тираж ЦНИИПИ Росударствепо делам из 3.13035, Москва, Ж 998 Подписное ного комитета СССР обретений и открычий 5, Раушс 3 иы наб., д. 4/б

СмотретьЗаявка

2624176, 05.06.1978

ПРЕДПРИЯТИЕ ПЯ А-3646

БОНДАРЕНКО ЮРИЙ ФЕДОРОВИЧ

МПК / Метки

МПК: H03K 3/28

Метки: импульсов, формирователь

Опубликовано: 23.07.1980

Код ссылки

<a href="https://patents.su/4-750701-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов</a>

Предыдущий патент: Измерительный генератор импульсов

Следующий патент: Мультивибратор

Случайный патент: Установка для диффузионной сварки