Система контроля параметров интегральных схем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 746437

Авторы: Белянин, Володарский, Самарцев, Туз

Текст

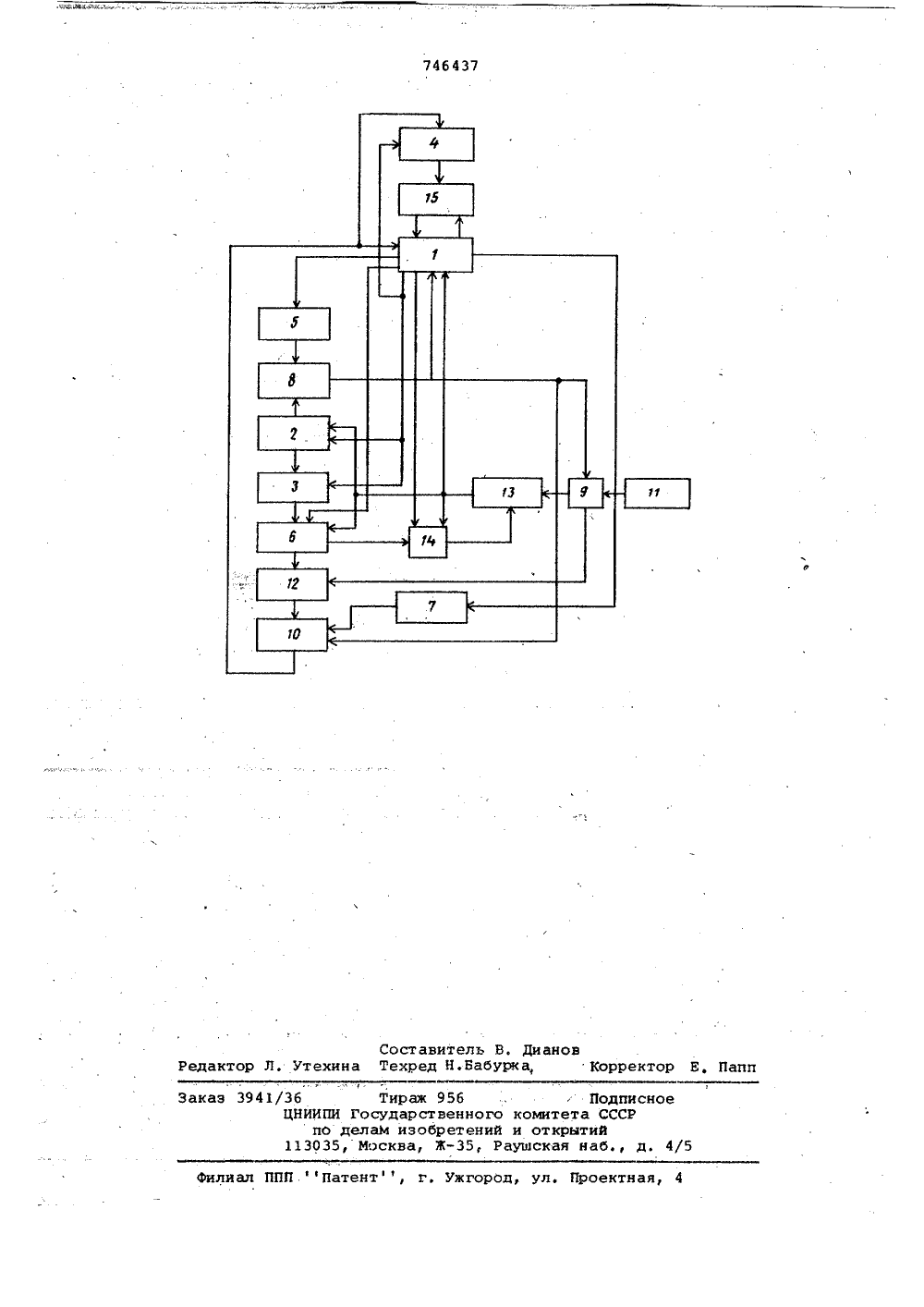

Союз Советских Социалистических Республикрц 746437 льнов 1) Допо вт. свид-ву 2556384/18-24 3) М. 2) Заявлено 19.12,77 исоеди Приор ением заявки йо 6 05 В 23/02 0 06 Р 15/46 Государственный комите СССР по делам изобретений и отнрытийте 7,80. Бюллетень Мо Яописанин 070780 ковано 07. убликован Опуб Дата 3) УДК 621 396(72) Ав изоб Ю.Н. Самарц ский, ляний я Киевский ордена Ленина50-летия Великой Октябр литехнический инсти кой социалистическо(54) СИСТЕ НТРОЛЯ ПАРКЕТСХЕМ ИНТЕГРАЛЬНЫ е к Изобретение относится к области автоматизированных систем для контроля и может быть использовано при контроле больших интегральных схем (БИС) и сверхбольших интегральных схем (СВИС) .Известны устройства для контроля эЛектрических параметров электронных схем (1),и 2), содержащие оммутационную матрицу, источники тока и напряжения, измерительный блок, блок управления и индикации, блок согласования, в ко торых в соответствии с программой контроля, поступающей из управляющей вычислительной машины УВМ, при помО- щи коммутационной матрицы к соответствующим выводам контролируемой электронной схемою подключаются программные истдачники напряжения, тока и измерительный блок. В результате контроля Формируются команды фГоден, Не годен в зависимости от того, находится параметр в требуемых пределах или выходит из их. Недостаткавы таких устройствяется жесткость программ контроольшое число управляющих команд 2низкая оперативность,контроля инт гральных схем,Наиболее близким техническим ре"шением к изобретению является система контроля параметров интегральныхсхем, содержащая УВМ, первый выходкоторой соединен с первым входомблока памяти, второй выход - с пер 10 вым входом счетчика адреса памяти,третий выход - с первым входом пер-,вого блока совпадения, четвертый выход через регистр выходных тестовыхкомбинаций - с Первым входом многоканального амплитудного дискРиминатора и пятый выход через регистр адреса тестовых комбинаций - с первымвходом блока с,равнения, второй входкоторого соединен с первым выходом .счетчика адреса памяти, а выход - спервым входом УВМ, одним входом второго блока совпадений и вторым входом ьФогоканального амплитудногодискриминатора, выход которого подключен ковторому входу УВМ, и генератор тактовых импульсов, соединен"ный .через последовательно включенныевторой блок совпадения и счетчикчисла повторений тестовых комбина 30ций с третьим входом УВМ, вторымвходом счетчйка адреса памяти, вторым входом блокапамяти и вторымвходом первого блока совпадения,третий вход которого соединен с выходом блока памяти, а выход - с другим входом счетчика числа повторений тестовых комбинаций 3),В процессе производства схем,бывает необходимо изменение "очередности контроля параметров схем иэза изменения соотношений между удельными весами параметров, по которымсхемы оказываются негодными (в результате возможных изменений условий технологического цикла при производстве очередной партии и внутриэтого цикла) . :: - 15Чтобы уменьшить потери временипри- контроле негодных схем очередность контроля параметров схем должна быть такой, что в первую очередьдолжны контролироваться те параметры, по которым схемачаще всего ока зываются негодными. Применение известной систеьы автоматического контроля больших интегральных схем прикрупносерийном производстве их оказывается малоэффективным из-за того,- что данная система производит -конт-роль йараметров интегральйых схем ив очередности, которая соответствует очередности опроса счетчиком адреса памяти ячеек ЗУ и не может иэме"йятьсяв"процессе койтроля,Целью изобретения является повышение быстродействия системы.Эта цель достигается тем, чтов"предложенную систему введены дешифратор кода очередности, блок-счет- чиков тестовых комбинаций икоммутатор тестовых комбинаций, первый входкбтоРогосоединен с выходом многокайальйож"амплитудного дискриминатора выход через блок счетчиков тестовых комбинаций - с четвертымвхо. дом и шестым выходом УВИ, а второйвход - со вторым выходом УВИ и первым входом дешифратора кода очередности, второй вход которого подключей кб "второму выходу счетчика адреса"памяти, а выход - к третьему входу блока памяти,На чертеже показана структурнаясхема системз.Выходы УВМ 1 соединены со входа-ми счетчика адреса памяти 2, дешифратбра кода очередности 3, коммутатора тестовых комбийаций 4; регистра адреса тестовых комбинаций 5,блока памяти б и регистра выходных тестовых комбинаций 7. Входы блокасравйения 8 соединенй с выходамй "регистра 5 и счетчика 2, а выходс входами второго блока совпадения 409, "ййооканыьного амплитудного дискриминатора 10 и УВМ 1, Другой входблока 9 соединен с вйходом генератора тактовых импульсов 11, а вй-хбды - с контролируемой большой ин 7гегральной схемой 12 и счетным входом счетчика числа повторений тестовых комбинаций 13, Входы первогоблока совпадений 14 соединены с выходами блока б, УВМ 1, счетчика 13и входами счетчика 2, УВМ 1 и блока б, Выход блока б соединен со схемой 12, Входы дискриминатора 10 соедйнены с выходами схемы 12 и регистра 7, а выход - с входами УВМ 1 икоммутатора 4. Счетный вход блока15 счетчиков тестовых комбинаций соединен с выходом коммутатора 4,входопроса и выход - с УВМ 1.Выход счетчика 2 соединен с дешифратором З,авыход последнего - со входом блокаб,Работа системы начинается с того,что по команде с УВМ 1 опрашиваютсясчетчики в блоке 15 и значения кодов,записанных в них, переписываются вУВМ 1, которая по программе, заложенной в ней, по результатам опросаформирует команды очередности, поступающие на дешифратор 3 таким образом, что первой поступает команда,соответствующая наибольшему коду,поступавшему из определенного счетчика блока 15, затем - команда, соответствующая меньшему по величинекбду и так в порядке убывания величины кодов до наименьшего (иначе УВМ1 формирует команды очередности всоответствии с величиной кодов счетчиков в блоке 15 в порядке их убывания). Если коды ряда счетчиков иливсех равны, то команды очередностиформируются в определенной последовательности, определяемой программой, заложенной в УВМ 1,УВМ 1 передает в счетчик 2 начальный адрес номера последовательности тестовых комбинацийВ то жевремя на вход дешифратора 3 и коммутатора 4 из УВМ 1 поступает кодочередности, соответствующей тойтестовой комбинации, которая должнаконтролировать схему первой. Навыходе дешифратора 3 появится разрешение на считывание той ячейки блока б, в которой хранится тестоваякомбинация входных воздействий, .соОтветствующая коду очередности,поступившему из УВМ 1 на дешифратор3, Коммуаатор 4 подключает выходдискриминатора 10 к счетному входутого счетчика из блока 15, которыйсоответствует проверяемой тестовойкомбинации. В регистр 5 записывается адрес номера тестовой комбинации,на которой требуется зафиксироватьвыходные сигналы контролируемой схемы, В регистр 7 иэ блока памяти выходных"теотовых комбинаций, входящего в состав УВМ 1, поступает выходная тестовая комбинация, соответствующая выходным сигналам схемы 12на указанном в регистре 5 номеретестовой комбинации.формула изобретения Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР Р 399802, кл, 6 01 К 31/28, 1970.На блок 6 иэ УВМ 1 поступает импульс запроса, В каждой ячейке блока 6 выделен ряд разрядов, и в последних записывается число цйклов генератора 11, в течение которых на проверяемую схему должна подава сяг данная тестовая комбинация входных воздействий. При считывании ячейки блока 6 на входы схемы 12 поучаются входные воздействия, а число циклов, в течение которых данные воздействия должны подаваться на схему 12, переписывается в обратном коде в счетчик 13 через блок 14. На счетный вход счетчика 13 подаются импульсы с генератора 11 через блок 9.При заполнении счетчика 13 наращивается на1содержимое счетчика 2, и подается на УВМ 1 команда на смену кода очередности, пбступающего на дешифратор 3. Запрашивается блок 6 по следующему адресу, сост ветствующему коду очередности, формируемому УВМ 1, и открывается блок 14 для записи в счетчик 13 следующей тестовой комбинации, На требуемом номере цикла (при равенстве ад ресов в счетчике 2 и регистре: 5) блок 8 запрещает прохождение тактовых импульсов на счетчик 13, закрывая блок 9, и подает стробирующий импульс на дискриминатор 10, 30Если в ходе контроляинтегральной схемы по какой-нибудь тестовой комбинации дискоиминатор 10 опРеделит несоответствие выходных сигналов схемы 12 и выходных тестовых комбина ций регистра 7, он формирует импульс, который через коммутатор 4 поступитна счетный вход того счетчика из блока 15, который соответствует данной контролируемой комбинации, и в нем 40 код увеличится на1Затем система переходит к контролю следующей интегральной схемы, Если импульс из дискриминатора 10 не поступает, контРолиРуется следующий 45 параметр схемы. Если все параметры схемы проходят контроль успешно,система переходит к контролю следующей схеж.Таким образом, в процессе контроля интегральных схем в счетчиках блока 15 накапливается информация в виде кодов, записанных в них, о том, но каким параметрам схемы чаще всего оказываются негодными и УВМ 1, обрабатывая эту информацию, формирует код очередности контроля параметров интегральных схем. Если хотя бы один иэ счетчиков блока 15 полностью заполнится, все счетчики сбрасываются в нулевое состояние. 60Испольэовайие данной сйстемы для автоматического контроля больших интегральных схем позволит в 2-3 раза увеличить производительность операций контроля при крупносерийное 65 производстве интегральных схем иполучить на заводах отрасли экономический эффект не менее 300 тыс.руб.в год. Система контроля параметров интегральных схем, содержащая управляющую вычислительную машину, (УВМ), первый выход которой соединен с первым входом блока памяти, второй выход - с первым входом счетчика адреса памяти, третий выход - с первым входом первого блока совпадения,чет- " вертый выход через регистр выходных тестовых комбинаций - с первым вхс- дом многоканального амплитудного дискриминатора и пятый выход через регистр адреса тестовых комбинаций с первым входом блока сравнения,второй вход которого соединен .с первым выходом счетчика адреса памяти, а выход - спервым входом УВМ, одним входом второго блока совпадений и вторым входом многоканального ампли- трудного дискримин атора, выход которого подключен ко второму входу УВМ и генератор тактовйх импульсов, соединенный через последовательно включенные второй блок совпадений и счетчик числа повторений тестовых комбинаций с третьим входом УВМ,вто" рым входом счетчика адреса памяти, вторым входом блока памяти и вторым входом первого блока совпадения,третий вход которого соединен с выходом блока памяти, а выход - с другим входом счетчика числа повторений тестовых комбинаций, о т л и ч а ющ а я с я тем, что, с целью повышения быстродействия системы, в нее введены дешифратор кода очередностИ блок счетчиков тестовых комбинаций и коммутатор тестовых комбинаций, первый вход которого соединен с выходом многоканального амплитудною дискриминатора, выходчерез блок счетчиковтестовых комбинаций - с ;четвертым входом и шестым выходоМ УВМ, а второй вход - со вторым выходом УВМ и первым входом дешифратора кода очередности, второй вход которого подключен ко второму выхо ду счетчика адреса памяти:, а выходк третьему входу,блока. памяти. 2, Авторское свидетельство СССРМ 416700, кл, О 06 Р 15/46, 1972.3. Авторское свидетельство СССР9 377738, кл. 6 05 В 23/02, 1971746437 Составитель В. Диановтехина Техред Н,Бабурка, Корректор Е, Папп Редактор з 394 ППП.фПатент,ул. Проектна жго л Тираж ИИПИ Государст по делам изоб 3035,Москва,56 . Подписноенного комитета СССРетений и открытий

СмотретьЗаявка

2556384, 19.12.1977

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

САМАРЦЕВ ЮРИЙ НИКОЛАЕВИЧ, ВОЛОДАРСКИЙ ЕВГЕНИЙ ТИМОФЕЕВИЧ, ТУЗ ЮЛИАН МИХАЙЛОВИЧ, БЕЛЯНИН ЮРИЙ ПАВЛОВИЧ

МПК / Метки

МПК: G01R 31/303, G06F 11/07

Метки: интегральных, параметров, схем

Опубликовано: 05.07.1980

Код ссылки

<a href="https://patents.su/4-746437-sistema-kontrolya-parametrov-integralnykh-skhem.html" target="_blank" rel="follow" title="База патентов СССР">Система контроля параметров интегральных схем</a>

Предыдущий патент: Устройство для контроля и регулирования параметров

Следующий патент: Устройство для контроля напряжений

Случайный патент: Установка для оборки откосов и очистки берм скальных уступов