Микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 646336

Авторы: Калмыков, Кириченко, Кривоносов, Сычев

Текст

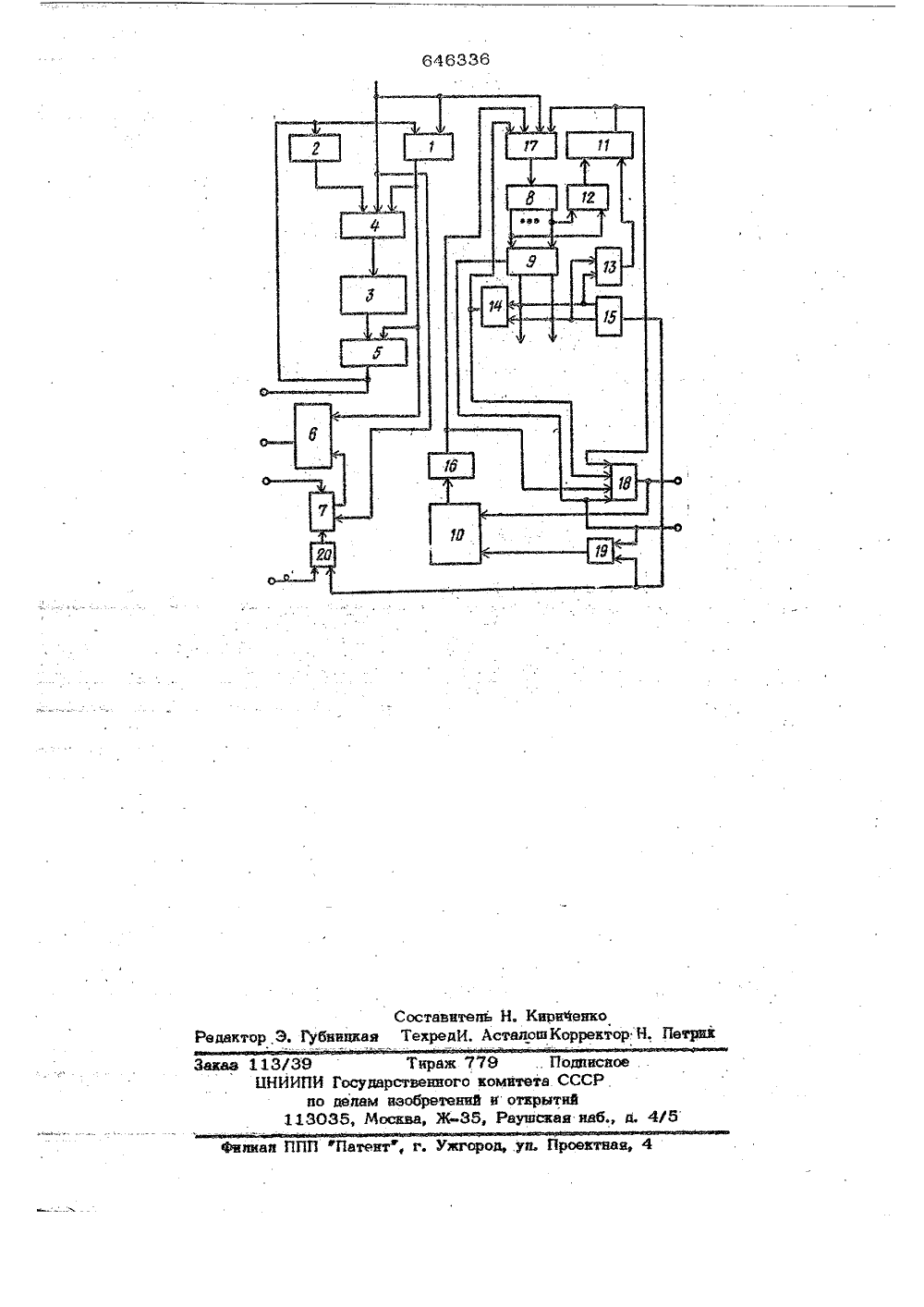

(22) Заявлено с присоедине (23) Приорите л осударстееннвй нонетет СССР. ео делам нзееретеннй н открытей(71) Заявител ИК РОПРОЦЕССО я повыИзобретение относится к области вычислительной техники и может быть использовано при создании больших интегральных схем, предназначенных для построения вычислительных управляющих систем.Известнът микропроцессоры, содержащие управляющую и информационные магистрали, арифметико-логический блок, блок памяти чисел, программнопогнческую матрицу, счетчик команд циклов), блок сдвига и управления ЯНедостатком известного микропроцессора является большой объем оборудованияНаиболее близким по существу тех- ническим решением задачи является микропроцессор, содержащий блок управления, первый вход которого соединен с первым входом микропроцессора, выход .ф блока управления соединен,с первыми входами первого, . второго и третьего мультиплексоров, второй вход первого мультиплексора, соединен с первым вхо . дом микропроцессора и первым входомсчетчика команд, первый выход которогонепосредственно, а второй выход черезтретий мультиплексор соединены с первым и вторым выходами микропроцессора, выход первого мультиплексора черезпоследовательно соединенные арифметикологический блок и второй мультиплексорсоединетт с третьим выходом микропроцессора и вторым входом блока управления,память, выходы которой через первыйдешифратор соединены с первым входомтриггера условного перехода, а черезстэковую память соединены с входамивторого, третьего и четвертого дешифраторов, выход второго дешифратора соединен со вторым входом триггера условных переходов 21.Недостатком известного микропроцессора является недостаточная надежность.Белью изобретения являетстйение надежности.,Поставленная цель достигается тем,что в микропроцессор введены реверсинный счетчик пятый дешифратор, четыре646333элемента И, причем выход реверсивногосчетчика через пятый дешифратор соединен о первыми входами первого и второго элементов И, вторые,и третьиовходы которых соединены соответствен,но с выходами триггера условного перехода и третьего дешифратора, четвертыйвход первого элемента И соединен спервым входом микропроцессора,четвертый вход второго элемента И соединен осо,вторым входом микропроцессора, управляющим входом стэковой памяти ипервым входом третьего элемента И,второй вход которого соединен с выходомчетвертого дешифратора и первым входом четвертого элемента И, второй входи выход которого соединены соответственно с третьим входом микропроцессораи вторым входом счетчика команд, выход второго элемента И соединен с чет фвертым выходом микропроцессора и первым входом реверсивного счетчика, второй вход которого соединен с выходомтретьего элемента И,25Блок-схема микропроцессора приведена на чертеже,Микропроцессор содержит блок 1управления, оперативную память 2, арифметико-логический блок 3, мупьтиппек 30соры 4-6, счетчик 7 команд, память 8,стаковую память .9, реверсивный счетчик10, триггер 11 условных переходов,дешифраторы 12-16, элементы И 1720,Устройство работает следующим образом.Управляющая и числовая информация через элемент И 17 поступает в40память 8. Преобразованное в памяти 8управляющее слово поступает в стэковую память 9 и записывается в первуюего ячейку.По приходу второго тактового им 45пульса первое управляющее слово переписывается во вторую ячейку, а второеслово записывается в первую ячейку нтак далее.Одновременно с записью информации56в память 9 производится суммированиев счетчике 10 единичного импульса,сформированного на выходе элемента И18, который выдается также на выходмикропроцессора и является стробом55выдачи управляющих слов иэ внешнейпрограммно-цогической матрицы илевнешнего постоянного запоминающегоустройства,Оо тех пор, пока в память 9 небудет внесено й спов (где п - чиспоячеек в памяти 9), на выходе его присутствует нулевой код, который распознается в дешифраторе 15, на выходекоторого присутствует нулевой потенциал,запрещающий вычитание единицы изсчетчика 10 и прибавпение единицы всчетчик 7,Этот запрет осуществляется на элементах И 19, 20,При записи И слов в память 9 всчетчике 10 накопится И импульсов,при этом на выходе дешифратора 16появится сигнал, который бпокируетвыдачу сигнапа на выход микропроцессора и запрещает.прохождение информации через элемент И 17,Начиная с этого момента временимикропроцессор готов к выполнениюпрограммы, хранящейся в стэковой памяти 9. При выдаче каждого слова навыходы текущей микрооперации из солдержнмого счетчика 10 вычитается едй-.ница, запрещающий сигнал на выходедешифратора 16 исчезает, что позвопяетпринимать управляющие слова в память9. При появлении на выходе стэковойпамяти 9 управляющего словахарактеризующего прием чисновой информации,на выходе дешифратора 14 вырабатывается сигнал, запрещающий прием информации в память 9.В этом случае эта информация поступает в память 2 или в счетчик 7,ипи в блок 1, или в блок 3, Коммутация информации межцу этими блокамиосуществляется . мультиплексорами 4-,. 6,При появлении на выходе памяти 8управляющего слова, характеризующегоусловный или безусловный переходы ипидругие ветвления программы, на выхо -де дешифратора 12 вырабатывается сигнал, устанавливающий в единичное состояние триггер 11, нулевой выход которого бпокирует прием информации впамять 8 и выдачу управляющего сигнала на выход процессора.При появлении этого управляющегослова на выходе стэковой памяти 9на выходе дешифратора 13 вырабатывается сигнал, устанавлимюший триггер11 в нулевое состояние, восле чегоприем информации в стэковую память 9,модификация содержимого счетчика10 и выдача управляющего сигнала навыход процессора разрешается, чемобеспечивается правильный выбор кодовпрограммы при ветвлениях и усповных переходах. При напичии нупевого кода на выходе стэковой памяти 9 модификация содержимого счетчика 7 блокируется, что исключает ложное формированне адреса текущей команды и выдачи переноса из счетчика 7 на выход процессора в хопостых циклах.Таким образом, изобретение позвопяет совместить информационную и управпяющие магистрапи практически без потери быстродействия, что приводит к исключению восьми наружных выводов Ь микропроцессоре по сравнению с нрототипом, Это позволяет ввести в состав микропроцессора значительно бопьшее чиспо признаков внешних усповий и повысить его разрядность в два раза, что обеспечивает повышение надежности микропроцессора и снижение аппаратных затрат при построении вычиспитепьных систем,Микропроцессор, содержащий блок управпения, первый вход которого соединен с первым входом микропроцессора, выход блока управления соединен с первыми входами первого, второго и третьего мупьтиппексоров второй вход первого мупьтиппексора соединен с первым вхсь. дом микропроцессора и первым входом счетчика команд, первый выход которого соединен непосредственно, а второй вйход через третий мупьтиппексор соединен ". первым и вторым выходами микропроцессора, выход первого мупьтиппекссьра через последовательно соединенные арифметико-логический бпок и второй мультиплексор соединен с третьим выходом микропроцессора и вторым входом блока управцения, память, выходы котоФормула изобретения 46 ЗЗ 6 брой через первый дешифратор соединеныс первым входом триггера усповногоперехода а через стэковую память соединены с входами второго, третьегоу и четвертого дешифраторов, выход второго дешифратора соединен со вторымвходом триггера условных переходов,о т л и ч а ю щ и й с я тем, что,с целью повышения надежности, в него16 введены реверсивный счетчик, пятыйдешифратор, четыре элемента И, причемвыход реверсивного счетчика черезпятый дешифратор соединен с первымивходами первого и второго эпементов И,33 вторые и третьи входы которых соединены соответственно свыходами триггера условного перехода и третьегодешифратора, четвертый вход первогоэпемента И соединен с первым входом2 ф микропроцессора, четвертый вход второгоэпемента И соединен со вторым входоммикропроцессора, управляющим входомстэковой памяти и первым входом третьего эпемента И, второй вход которогосоединен с выходом четвертого дешифратора и первым входом четвертогоэлемента И, второй вход и выход которого соединены соответственно с третьим входом микропроцессора и вторымф входом счетчика команд, выход второгоэпемента И соединен с четвертым выходом микропроцессора и первым входом реверсивного счетчика, второй входкоторого соединен с выходом третьегоф элемента И.Источники информации, принятые вовнимание. при экспертизе1,ф Эпектроника", М 8, 1974с. 46-51.ф 2. Разработка микропроцессоров имикропроцессорных систем, ч. 1. Обзоры по эпектронной технике, серия .3фМикроэпектроника вып. 5, 1 ЙИП.раж 779Подписное . нного комптета СССРобретений и отнритий Ж, Раушсжан наб., а,13/39ЦНИИПИ Государстно юлам иэ113036, Москва Составитепь К. КириченкоРедактор.Э. Губнинкая ТехредИ, ЛсталошКорректор Н. Летний

СмотретьЗаявка

2380545, 02.07.1976

ПРЕДПРИЯТИЕ ПЯ А-7160

КРИВОНОСОВ АНАТОЛИЙ ИВАНОВИЧ, КИРИЧЕНКО НИКОЛАЙ ВАСИЛЬЕВИЧ, КАЛМЫКОВ ВАЛЕНТИН АЛЕКСАНДРОВИЧ, СЫЧЕВ АЛЕКСАНДР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропроцессор

Опубликовано: 05.02.1979

Код ссылки

<a href="https://patents.su/4-646336-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор</a>

Предыдущий патент: Запоминающее устройство

Следующий патент: Цифровое вычислительное устройство

Случайный патент: Устройство для передачи дискретной информации