Микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

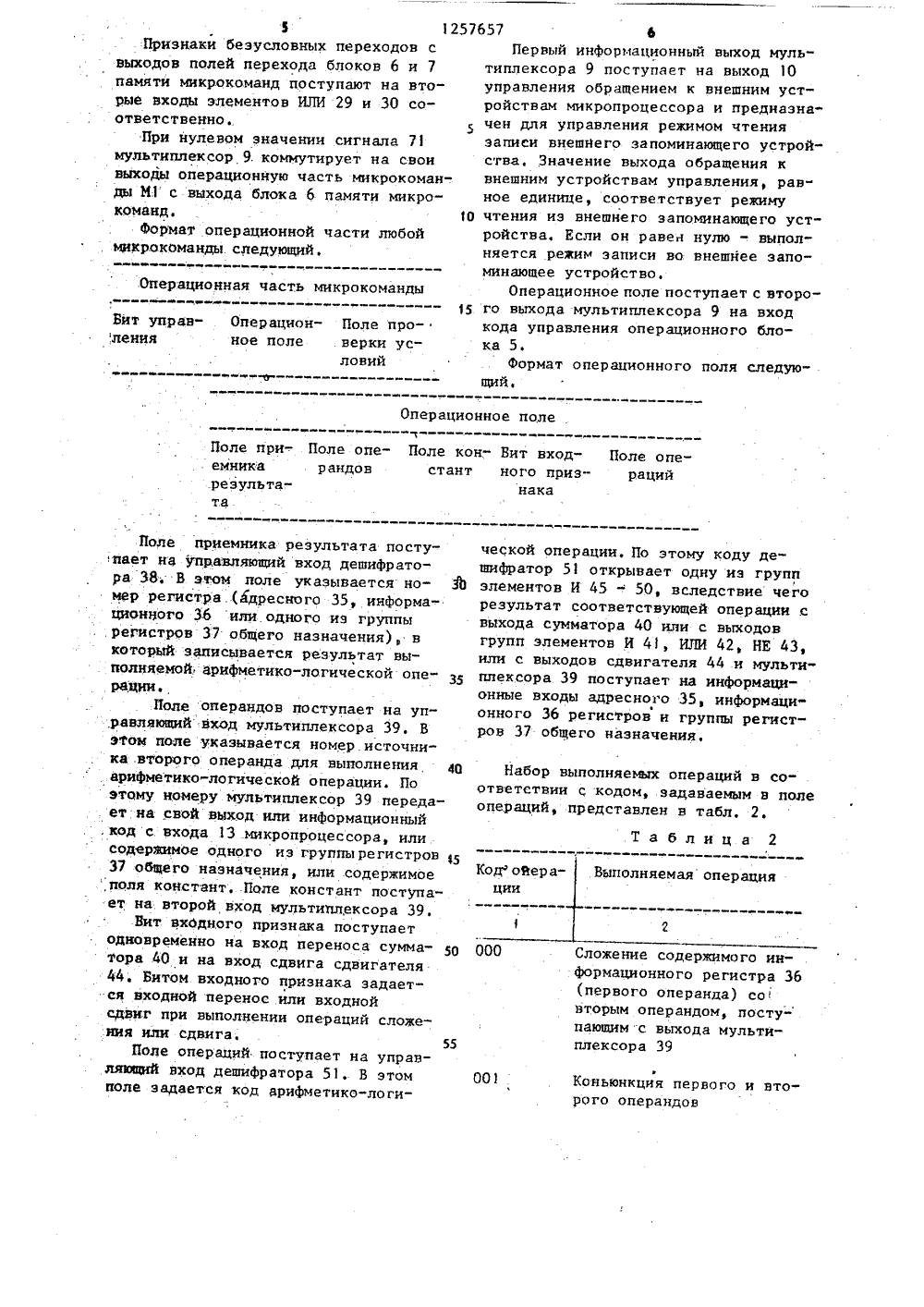

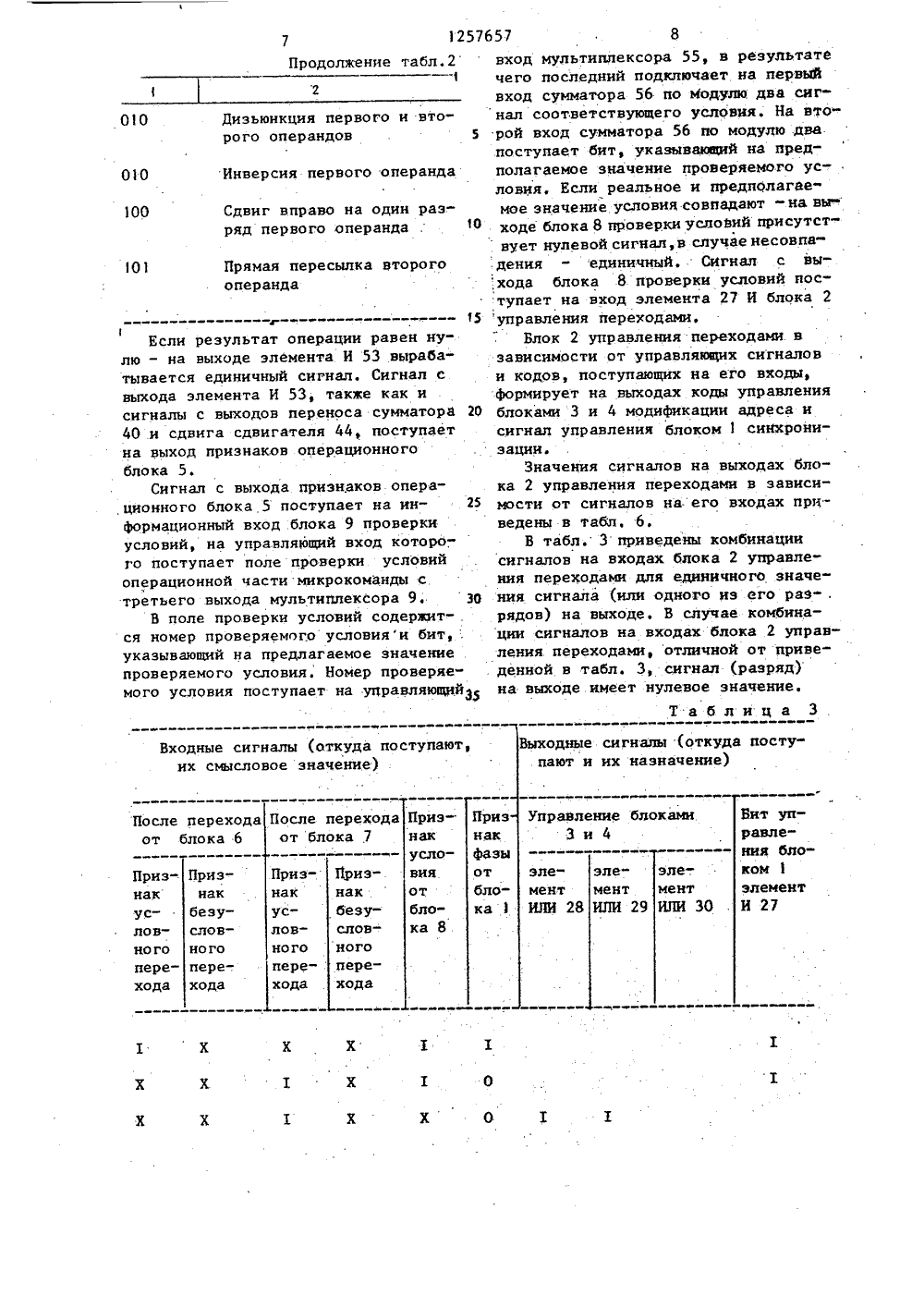

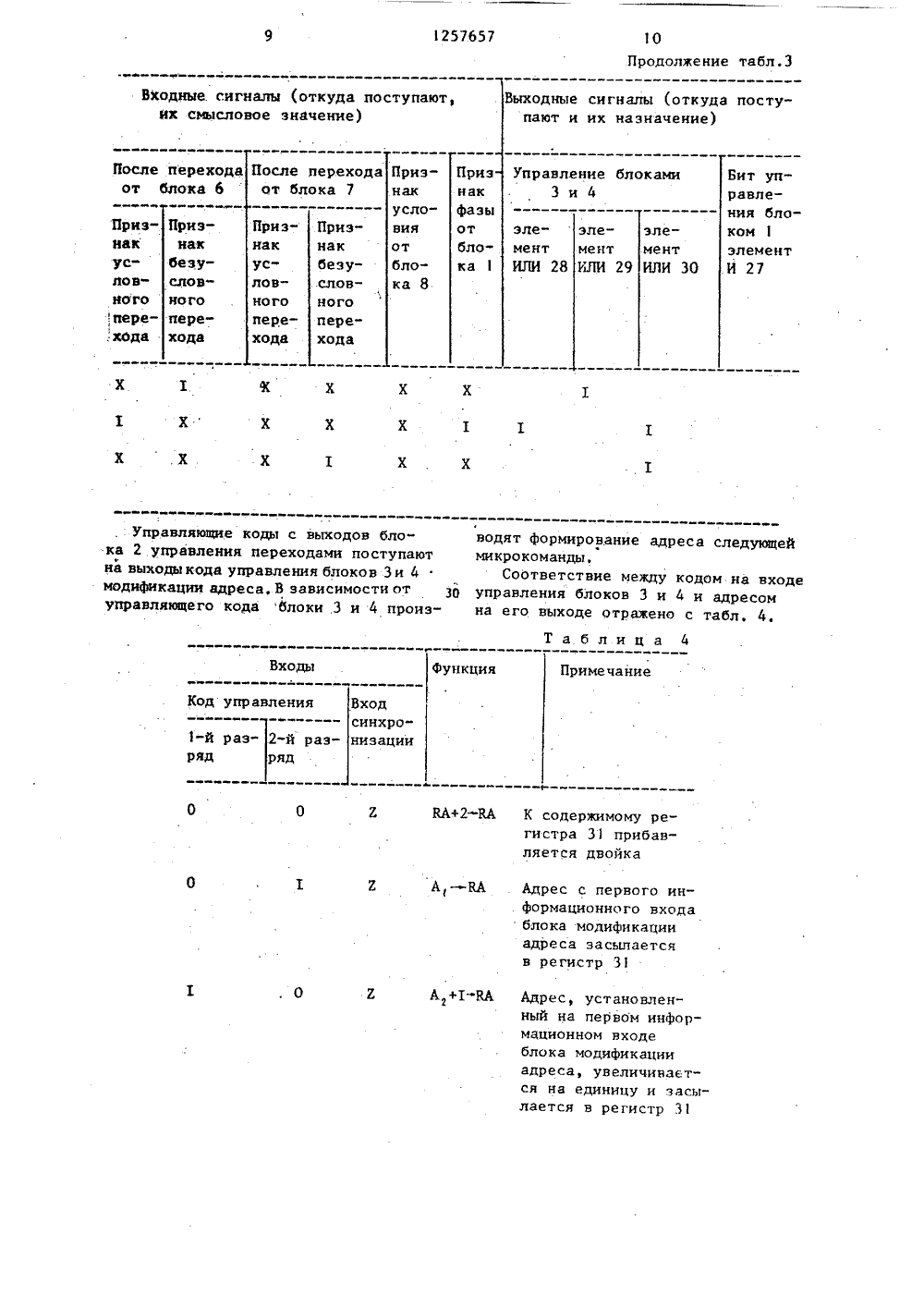

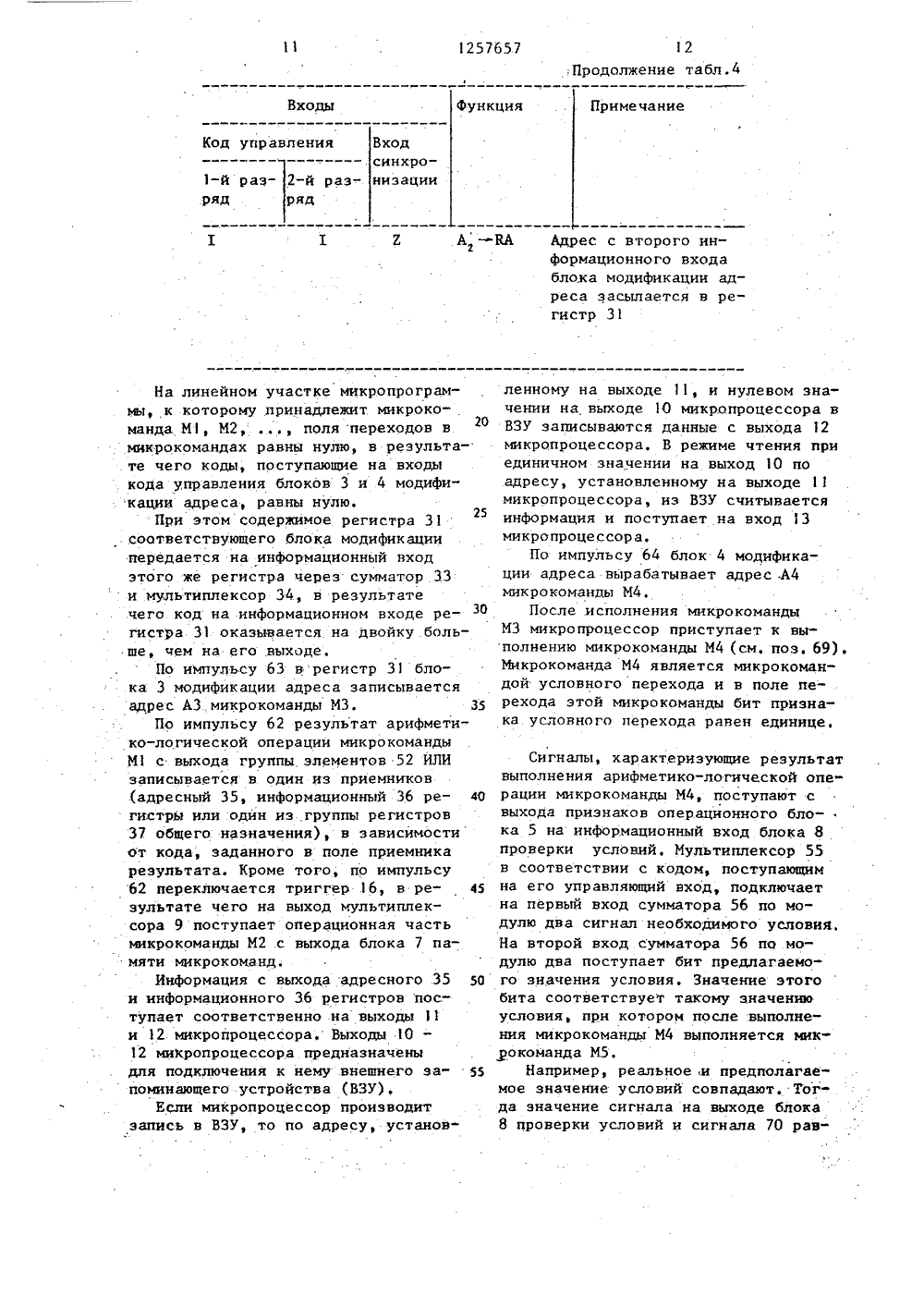

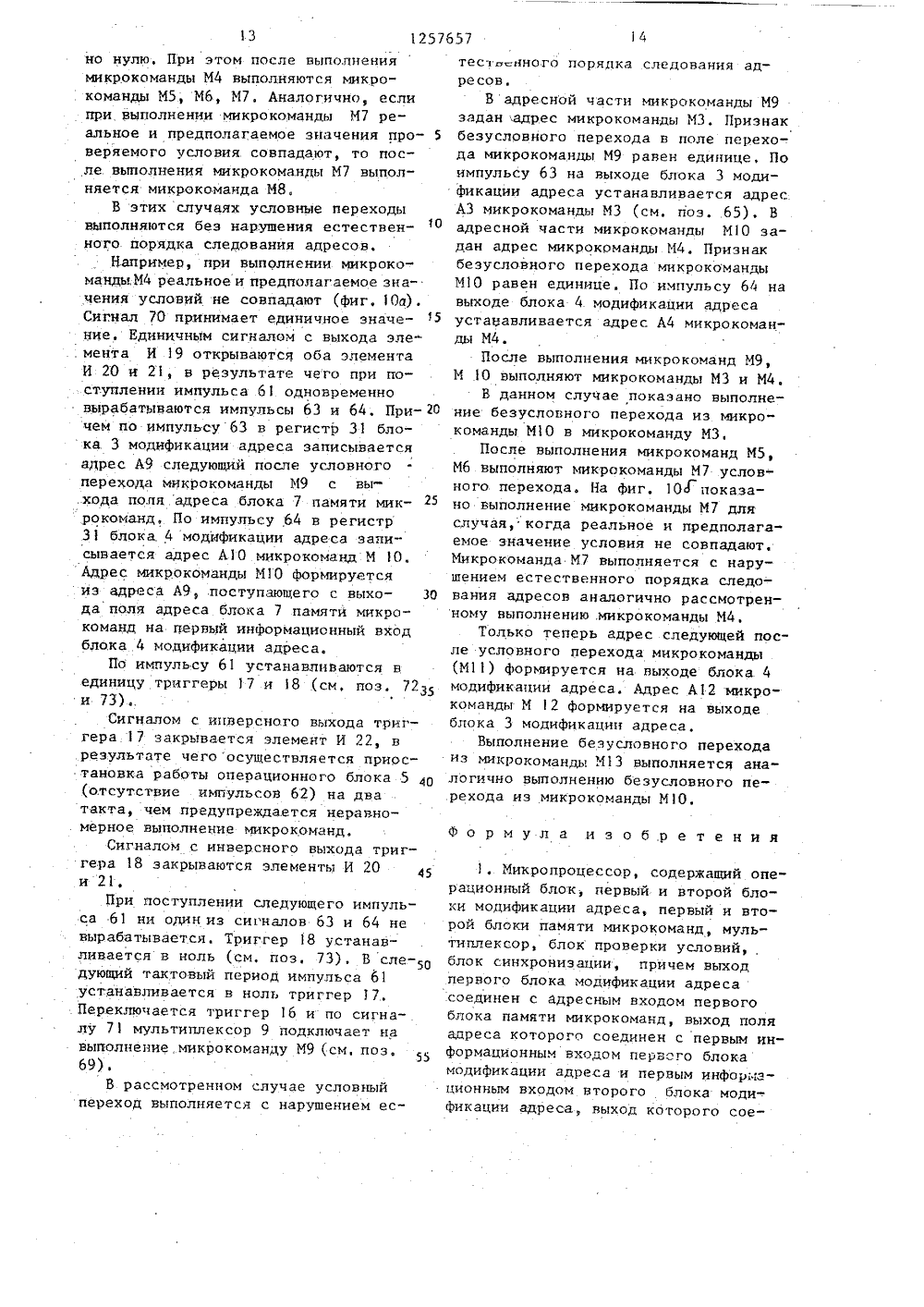

(46) 15.09.86. У 3 72) Ю. Який арев и Д. В. Полон о СССР л ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ТОРСНОМ,Ф СВИДЕТЕЛЬСТВ(57) Изобретете относится к вычислительной технике и может быть использовано для обработки данных всистемах управления. Целью изобретения является повьипение производительности микропроцессора. Микропроцессор содержит блок синхронизации,блок управления переходами, блоки модификации адреса, операционный б ок,блоки памяти микрокоманд, блок проверки условий, мультиплексор, управляющий, адресный н информационныйвыходы, информационный вход, входсинхронизации и вход начальной устанонки. В данном микропроцессоре непроизводится разбиение микропрограммы на четные и нечетные последовательности микрокоманд, что приводитк потере производительности микропроцессора при выполнении безусловныхпереходов. В обоих блоках памятихранится полный набор микрокоманд,а исполнение их производится поочередно: то нз одного блока памяти,то из другого, Поэтому выполнениебезусловных переходов не зависит оттого, производится переход между мик"рокомандами в одноименной последовательности или между разноименнымипоследовательностями мнкрокоманд. Врезультате безусловные переходывсегда выполняются без холостых циклов, что в целом повышает производительность микропроцессора. 1 э.п.ф-лы, 10 нл, 7 табл, 1257617тьими входами второго и третьего элементов И и с входом К второго 1 К- триггера блока синхронизации, прямой выход третьего 1 К-триггера блока синхронизации соединен с входом К третьего 1 К-триггера блока синхронизации, выход четвертого элемента И блока синхронизации соединен с входом синхронизации операционного блока, выход блока проверки условий 1 О соединен со вторым входом третьего элемента И блока управления перехо"дами,2. Микропроцессор по п. 1, о тл и ч а ю щ и й с я тем, что блокмодификации адреса содержит регистр,два сумматора и мультиплексор, причемпервый информационный вход мульти"плексора соединен с вторым информационным входом блока, второй информационный вход мультиплексора соединен с выходом первого сумматора,первая группа входов которого соединена с третьим информационным входоммультиплексора и с первым информаци 57 Яонным входом блока, вход младшегоразряда второй группы входов первогосумматора соединен с шиной логической единицы, остальные входы второйгруппы первого сумматора подключенык шине логического нуля, первый ивторой разряды управляющего входамультиплексора соединены соответственно с .первым и вторым разрядамивхода управления блока, выход мультиплексора соединен с информационнымвходом регистра, входы сброса И записикоторого соединены соответственно свходом начальной установки и с входом синхронизации блока, выход региСтра соединен с выходом блока и спервой группой входов второго сумматора, второй разряд второй группывходов второго сумматора .соединен сшиной логической единицы, остальныевходы второй группы второго суммато"ра соединены с шиной логического нуля, выход второго сумматора соединенс четвертым информационным входоммультиплексора,1257657 4 ьг пу Составитель В. КочедыковТехред ЛСердюковаКорректор И. Мус каз 49 Тирык 671 ВНИИПИ Государственного коми по делам изобретений и отк 3035, Москва, Ж, Раушскаяодписное 4/5 лиграфическое предприятие л. Проектная, 4 изводств ород Редактор М. Недолужен та ССтийаб., 1257657Изобретение относится .к вычислительной технике и может быть использовано для обработки данных в системах управления.Целью изобретения является повышение производительности микропроцессора.На фиг, 1 изображена схема микропроцессора;иа фиг. 2 - схема блокасинхронизации; на фиг. 3 - схема блока управления переходами; на фиг. 4 "схема блока модификации адреса;, наФиг. 5 - схема операционного блока;, на Фиг. 6 - схема блока проверки условий; на Фиг. 7 - схема мультиплек. сора; на фиг. 8 - блок-схема алгоритма микроцрограмьи; на Фиг. 9 и10 а, б - временные диаграммы рабо- .ты микропроцессорАМикропроцессор содержит блок 1синхронизации, блок 2 управленияпереходами, блохи 3 и 4 модификацииадреса, операционный блок 5 блоки6 и 7 памяти микрокоманд блок 8проверки условий, мультиплексор 9,управляющий 10, адресный 11 и информационный 12 выходы, информационныйвход 13, вход 14 синхронизации и:вход 15 начальной установки,Блок синхронизации содержит 1 Ктриггеры 16 - 18, элементы 19 - 22,элементы ИЛИ 23 и 24.Блок управления переходами содержит элементы И 25 - 27, элементыИЛИ 28 - 30.Каждый иэ блоков модификации адреса содержит регистр 31, сумматоры32 и 33 и мультиплексор 34,Операционный блок содержит адресный 35 и информационный 36 регистры,группу регистров 37 общего назначения, дешифратор 38 приемника результата, мультиплексор 39 операндов,сумматор 40, группы операционныхэлементов И 41, ИЛИ 42, НЕ 43,сдвигатель И 44, группы коммутирующих элементов И 45 - 50, дешифратор51 ойераций, группу элементов ИЛИ 52,. элемент И 53 и свертку 54 по модулюдва.Блок проверки условий содержитмультиплексор 55 и сумматор 56 помодулю два. Группа входов мультиплексоре 55 соединена с информационнымвходом блока 8 проверки условийВыход мультиплексора 55 соединен спервым входом сумматора 56 по модулюдва, выход которого соединен с выхо 55 ропрограииы, при котором производитсяпоочередное выполнение иикрокомандиз одного и другого блоков памятииикрокоианд. без нарушения естествендом блока 8 проверки условий. Управлякиций вход мультиплексора 55 и второй вход сумматора 56 по модулю двасоединены с входом кода управления5 блока 8 проверки условий,Мультиплексор содержит группыэлементов И 57, И 58 и ИЛИ 59.На временных диаграммах работыустройства принятыми следукщие обозначения: 60 - сигнал начальной установки на входе 15. устройства; 61импульсы на входе 14 синхронизацииустройства; 62 - импульсы на выходе.элемента 22 И; 63 - импульсы на выходе элемента 21 И; 64 - импульсы навыходе элемента 20 И; 65 - сигналадреса на выходе блока 3 модификации адреса; 66 " сигнал кода микрокоманды на выходе блока б памятимикрокоманд; 67 - сигнал адреса навыходе блока 4 модификации адреса;68 - сигнал кода микрокоманды навыходе блока 7 памяти микрокоманд;69 - сигнал кода микрокоманды навыходе мультиплексора 9; 70 - сигнална выходе элемента 27 И; 71 - сигнална выходе 1 К-триггера 16; 72 - сигнал на выходе 1 К-триггера 17; 73 -сигнал на выходе 1 К"триггера 18;л" цикл микрокоманды; е - время считывания из памяти микрокоманд,Рассмотрим работу устройства напримере выполнения им микропрограммы, алгоритм которой показан на35 фиг, 8,Полный набор микрокоманд хранитсякак в блоке 6 памяти микрокоманд, таки в блоке 7 памяти микрокоманд.Во время работы микропроцессора4 О из одного бпока памяти микрокоиандсчитываются для выполнения тольконечетные микрокоманды (М 1, МЗ, М 5,(М 2, М 4, Мб,). При выполнении ус 45 ловньп или безусловных переходовможет изменяться Фаза выборки микрокоманд из блоков памяти.Из первого блока памяти уже начинают считываться четные иикрокоманды, а нз другого - нечетные.В процессе работы микропроцессоравозможны следующие особенности выполнения микропрограмиы:выполнение линейного участка иикАлгоритм микросхемы, лредставленный.на фиг. 8, предполагает выполнение микропрограммы .с учетом перечисленных особенностей,Рассмотрим работу устройства всоответствии с временной диаграммой,показанной на фиг. 9. Входы Х О О О О 1 0 Е О О В соответствии с табл. 1 триг-Адресные части микрокоманд постугер 16 постоянно находится в счет- . .пают с выходов поля адреса блоков 6 ном режиме распределяя входную се- и 7 памяти микрокоманд на информа"140рию импульсов 61 на две выходные:63ционные входы блоков 3 и 4 мо и 64. ции адреса. В адресной частиВсе действия в микропроцессоре манды задается адрес микроком осуществляются по задним фронтам которую вЫполняется условный импульсов б - 64. безусловный переход.По адресам А 1 (О:.00) и А 2Операционные части микрокоманд45(001) (см. поз. 65 и 67), соот- поступают с выходов поля операции ветственно из блоков 6 и 7 памяти блоков 6 и 7 памяти:микрокоманд на микрокоманд через время С считываются. первый и второй информационные входы микрокоманды МЕ и И 2 (см. поз 66 и мультиплексора 9 соответственно68). . 1 О Поле перехода каждой командыформат каждой микрокоманды приве- содержит два выхода: признак условден ниже, ноГо перехода в признак безусловного-перехода,нда Признаки условных переходов с выходов полей перехода блоков 6 и 7е- памяти микрокоманд поступают навторые входы элементов И 26 и 25соответственно. дификаиикроко"анды, в Микро кома Адресная Операцион- После пчасть ная часть рехода 3 1 ного порядка следования адресов (адрес каждой следующей микрокоманды на единицу больше предыдущей);выполнение условного перехода без нарушения естественного порядка следования адресов; :выполнение условного перехода с нарушением естественного порядка следования адресов;выполнение безусловного перехода. 257657 4Для приведения микропроцессора висходное состояние подается сигнал60, в результате чего регистр 31 вблоке 3 модификации адреса и 1 Ктриггер 16 устанавливаются в ноль,а регистр 31 в блоке 4 модификацииадреса устанавливается в состояние001.После снятия сигнала 60 блок1 О синхронизации начинает .вырабатыватьдве серии импульсов 63 и 64, сдви-.нутых относительно друг друга наполупериод. Блок 1 синхронизациипостроек .на базе 1 К-триггеров, 15 Таблица истинности ЕК". триггерапоказана в табл. 1, где символом "Х"в этой и. в последующих таблицах,обозначено безразличное или неопределенное состояние сигнала.Таблица 1бПервый информационный выход мультиплексора 9 поступает на выход 10 управления обращением к внешним устройствам микропроцессора и предназна чен для управления режимом чтениязаписи внешнего запоминающего устройства, Значение выхода обращения к внешним устройствам управления, рав" ное единице, соответствует режиму 1 О чтения из внешнего запоминающего устройства, Если он раве нулю - выполняется режим записи во внешнее запоминающее устройство,Операционное поле поступает с второ го выхода мультиплексора 9 на входкода управления операционного блока 5.Формат операционного поля следующий 1257657 Бит управления Операционное поле Поле кон- Бит вход- Поле опестант ного приз- рацийнака Поле при- Поле опеем них:а рандоврезультата. Поле приемника результата поступает на управляющий вход дешифратора 38. В этом поле указывается но- ,й мер регистра.(адресного 35, информаци 0 щого 36 или одного из группы .регистров 37 общего назначения), в который записывается результат выполняемой арифметико-логической оперзцииеПапе операндов поступает на управляющий вход мультиплексора 39. В этом поле указывается номер.источника .второго операнда для выполнения 40 арифметико-логической операции. По этому номеру мультиплексор 39 передает на свой выход или информационный , код с входа 13 микропроцессора, или содержкмое одного из группырегистрон 15 37 общего назначения, или .содержимоеполя констант. Поле констант поступает на второй вход мультиплексора 39,Бит вхбдного признака поступает одновременно на вход переноса сумматора 40 и на вход сдвига сдвигателя44. Битом входного признака задается входной перенос или входной сдзиг при выполнении операций сложения или сдвига. 55Поле операций поступает на управлааций вход дешифратора 51. В этомполе задается код арифметико-логи.Та блиц а 2 я 00 о(перво вторым ающиплекс Фньюнкция первого и вго операндов 0 3Признаки безусловных переходов с выходов полей перехода блоков 6 и 7 памяти микрокоманд поступают на вторые входы элементов ИЛИ 29 и 30 соответственноПри нулевом значении сигнала 7 мультиплексор 9. коммутирует на свои выходы операционную часть микрокоманды М 1 с выхода блока 6 памяти микро- команд.Формат операционной части любой микрокоманды следующий,Операционная часть микрокоманды Операцион" Поле проное поле верки ус- ловий ческой операции, По этому коду дешифратор 51 открывает одну иэ групп/элементов И 45 ". 50, вследствие чегорезультат соответствующей операции свыхода сумматора 40 или с выходовгрупп элементов И 41, ИЛИ 42, НЕ 43,или с выходов сдвигателя 44 и мультиплексора 39 поступает на информационные входы адресного 35, информационного 36 регистров и группы регистров 37 общего назначения,Набор выполняемых операций в соответствии с кодом, задаваемым в поле операций, представлен в табл. 2. ние содержимого инционного регистра 36го операнда) сооперандом, посту"с выхода мультира 39657 010 010 100 101 Т аблица 3 После переходаот блока 7 Признакфазыот Управление блоками Зи 4 Признак Бит управле"ния блоком 1 После перехода от блока 6услоПризнак .безусловПризнак ее- эле-. Признак беэу- словного пере- хода ризак элементИ 22 отблоблока мент меИЛИ 29 ИЛИ т2 сусловловного иере ного ного ере ода перехода Х Х О 1 Х Х 7 1257Продолжение табл,2-1 Дизьюнкция первого и второго операндов 5 Инверсия первого операнда Сдвиг вправо на один разряд первого операнда . 10 Прямая пересылка второгооперанда Ю 15Если результат операции равен нулю - на выходе элемента И 53 вырабатывается единичный сигнал. Сигнал с выхода элемента И 53, также как и сигналы с выходов переноса сумматора 10 40 и сдвига сдвигателя 44, поступает на выход признаков операционного блока 5.Сигнал с выхода признаков опера,ционного блока 5 поступает на ин формационный вход блока 9 проверки условий, на управляющий вход которого поступает поле проверки условий операционной части микрокоманды с. третьего выхода мультиплексора 9. зоВ поле проверки условий содержит- . ся номер проверяемого условияи бит, . указывающий на предлагаемое значение проверяемого условия. Номер проверяемого условия поступает на управляющий 5 Входные сигналы (откуда поступают, их смысловое значение) 8вход мультиплексора 55, в результате чего последний подключает на первый вход сумматора 56 по модулю два сигнал соответствующего условия. На вто.рой вход сумматора 56 по модулю два поступает бит, указывающий на предполагаемое значение проверяемого условия, Если реальное и предполагае мое значение условия совпадают -на выходе блока 8 проверки условий присутствует нулевой сигнал,в случае несовпадения - единичный. Сигнал с вы;хода блока 8 проверки условий ноступает на вход элемента 27 И блока 2 управления переходами.Блок 2 управления переходами в зависимости от управляющих сигналов и кодов, поступающих на его входы, формирует на выходах коды управления блоками 3 и 4 модификации адреса и сигнал управления блоком 1 синхронизации.Значения сигналов на выходах блока 2 управления переходами в зависимости от сигналов на. его входах лрцведены в табл. 6.В табл. 3 приведены комбинации сигналов на входах блока 2 управления переходамн для единичного значения сигнала (или одного иэ его раз- . рядов) на выходе. В случае комбинации сигналов на входах блока 2 управления переходами, отличной от приведенной в табл. 3, сигнал (разряд) на выходе имеет нулевое значение. Выходные сигналы (откуда поступают и их назначение)257657 ОПродолжение табл.З Входные. сигналы (откуда поступают, их смысловое значение) Выходные сигналы (откуда поступают и их назначение) После перехода Призот блока 7 накПосле перехода от блока 6Управление блоками 3 и 4 условия Признак элеэлементИЛИ ЗО элеотблока 8 ментИЛИ 28 ментИЛИ 29 элементИ 27 условногоперехода пере- хода Х Х Х 1 1 Х . Х ХХ Х Х,Х Управляющие коды с выходов блока 2 управления переходами поступают на выходы кода управления блоков Зи 4 модификации адреса, В зависимости от управляющего кода блоки 3 и 4 производят формирование адреса следующей микрокоманды,Соответствие между кодом на входе управления блоков 3 и 4 и адресом на его выходе отражено с табл, 4. Таблица 4 Примечание Входы Функция Код управления Входсинхронизации 1-й раз-й разряд Ряд О О К содержимому регистра 3 прибавляется двойка А ВА О А +1-ВА Признакус- ловного.,пере;хода Признак безу- словного пере- хода Признакбеэу.славного ПризнакфазыотблокаАдрес с первого информационного входа блока модификации адраса засылается в регистр 3 Адрес, установленный на первом информационном входеблока модификации адреса, увеличивается на единицу и засылается в регистр 3 Бит управления блоком12Продолжение табл.4 1257657 Входы функция Примечание Код управления Вход.синхро- низации 1-й раз-й разряд ряд А ВА 2 На линейном участке микропрограммы, к которому принадлежит микрокоманда М 1, М 2 поля переходов в20микрокомандах равны нулю, в результате чего коды, поступающие на входы. кода управления блоков 3 и 4 модификации адреса, равны нулю.При этом содержимое регистра 3125соответствующего блока модификациипередается на информационный входэтого же регистра через сумматор 33и мультиплексор 34., в результатечего код на информационном входе регистра 31 оказывается на двойку больше, чем на его выходе.По импульсу 63 в регистр 31 блока 3 модификации адреса записываетсяадрес АЗ микрокоманды МЗ. 35По импульсу 62 результат арифметико-логической операции микрокомандыМ 1 с выхода группы элементов 52 ИЛИзаписывается в один из приемников(адресный 35, информационный 36 регистры или одйн из группы регистров37 общего назначения), в зависимостиот кода, заданного в поле приемникарезультата. Кроме того, по импульсу62 переключается триггер 16, в резулътате чего на выход мультиплексора 9 поступает операционная частьмикрокоманды М 2 с выхода блока 7 памяти микрокоманд,Информация с выхода адресного 35 50и информационного 36 регистров пос. -тупает соответственно на выходы 11и 12 микропроцессора. Выходы 10 -12 микропроцессора предназначеныдля подключения к нему внешнего запомииающего устройства ВЗУ),Если микропроцессор производитзапись в ВЗУ, то по адресу, установАдрес с второго информационного входа блока модификации адреса засылается в регистр 31 ленному на выходе 11, и нулевом значении на выходе 10 микропроцессора в ВЗУ записываются данные с выхода 12 микропроцессора, В режиме чтения при единичном значении на выход 10 по адресу, установленному на выходе 11 микропроцессора, из ВЗУ считывается информация и поступает на вход 13 микропроцессора.По импульсу 64 блок 4 модификации адреса вырабатывает адрес А 4 микрокоманды М 4.После исполнения микрокоманды МЗ микропроцессор приступает к выполнению микрокоманды М 4 (см, поз. 69). Микрокоманда М 4 является микрокомандой условного перехода и в поле перехода этой микрокоманды бит признака условного перехода равен единице. Сигналы, характеризующие результатвыполнения арифметико-логической операции микрокоманды М 4, поступают свыхода признаков операцйонного бло-ка 5 на информационный вход блока 8проверки условий. Мультиплексор 55в соответствии с кодом, поступающимна его управляющий вход, подключаетна первый вход сумматора 56 по модулю два сигнал необходимого условий,На второй вход сумматора 56 по модулю два поступает бит предлагаемого значения условия. Значение этогобита соответствует такому значениюусловия, при котором после выполнения микрокоманды М 4 выполняется мик;рокоманда М 5,Например, реальное и предполагаемое значение условий совпадают. Тогда значение сигнала на выходе блока8 проверки условий и сигнала 70 рав 1257657 4но нулю, При этом после выполнениямикрокоманды М 4 выполняются микрокоманды М 5, М 6, М 7. Аналогично, еслипри выполнении микрокоманды М 7 реальное и предполагаемое значения проверяемого условия совпадают, то после выполнения микрокоманды М 7 выполняется микрокоманда М 8,В этих случаях условные переходывыполняются без нарушения естественного порядка следования адресов,Например, при выполнении микрокомандыМ 4 реальное и предполагаемое значения условий не совпадают (фиг, Оа).Сигкал 70 принимает единичное эначение, Единичным сигналом с выхода эле"мента И 19 открываются оба элементаИ 2 О и 21, в результате чего при поступлении импульса 6 одновременновырабатываются импульсы 63 и 64. Причем по импульсу 63 в регистр 31 бло ка 3 модификации адреса записываетсяадрес А 9 следующий после условногоперехода микрокоманды М 9 с вы.хода поля адреса блока 7 памяти микрокаманд, По импульсу 64 в регистр31 блока. 4 модификации адреса записывается адрес А 10 микрокоманд М 10.Адрес микрокоманды М 10 формируетсяиэ адреса А 9, .поступающего с выхода поля адреса блока 7 памяти микрокоманд на первый информационный входблока 4 модификации адреса.По импульсу 61 устанавливаются вединицу триггеры 17 и 18 (см, поз. 2 З 5и 73)Сигналом с инверсного выхода триггера 17 закрывается элемент И 22, врезультате чегоосуществляетсн приостановка работы операционного блока 5(отсутствие импульсов 62) на дватакта, чем предупреждается неравномерное выполнение микрокоманд,Сигналом с инверсного выхода триггера 18 закрываются элементы И 20и 21,При поступлении следующего импульса 61 ни один из сигналов 63 и 64 кевырабатывается. Триггер 18 устанавливается в коль (см. поз, 73). В слеОдующий тактовый период импульса 61устанавливается в ноль триггер 17.Переключается триггер 16 и по сигналу 71 мультиплексор 9 подключает навыполнение микрокоманду М 9 (см, поз,69),В рассмотренном случае условныйпереход выполняется с нарушением естесч нного порядка следования адресов.В адресной части микрокоманды М 9задан .адрес микрокоманды МЗ. Признакбезусловного перехода в поле перехода микрокоманды М 9 равен единице, Поимпульсу 63 на выходе блока 3 модификации адреса устанавливается адресАЗ микрокоманды МЗ (см, поэ. 65). Вадресной части микрокоманды М 10 задан адрес микрокоманды М 4. Признакбезусловного перехода микрокомандыМ 10 равен единице. По импульсу 64 навыходе блока 4 модификации адресаустанавливается адрес А 4 микрокоманды М 4.После выполнения микрокоманд М 9,М 1 О выполняют микрокоманды МЗ и М 4,В данном случае показано выполнение безусловного перехода из микрокоманды М 10 в микрокоманду МЗ,После выполнения микрокоманд М 5,М 6 выполняют микрокоманды М 7 условного перехода, На фиг. 1 ОГ показано выполнение микрокоманды М 7 дляслучая, когда реальное и предполагаемое значение условия не совпадают.Микрокоманда М 7 выполняется с нарушением естественного порядка следования адресов аналогично рассмотренному выполнению,микрокоманды М 4.Только теперь адрес следующей после условного перехода микрокоманды(М 11) формируется на выходе блока 4модификации адреса. Адрес А 12 микрокоманды М 12 формируется на выходеблока 3 модификации адреса,Выполнение безусловного переходаиз микрокоманды М 13 выполняется аналогично выполнению безусловного перехода из микрокоманды М 10,Формула изобретения1, Микропроцессор, содержащий опе" рационный блок, первый и второй блоки модификации адреса, первый и второй блоки памяти микрокоманд, мультиплексор, блок проверки условий, блок синхронизации, причем выход первого блока модификации адреса соединен с адресным входом первого блока памяти микрокоманд, выход поля адреса которого соединен с первым информационным входом первого блока модификации адреса и первым инфор;ационным входом второго блока модификации адреса, выход которого сое257657 16 5 10 15 20 25 элемента ИЛИ блока управления перехо"40 . дами соединен с первым входом третье 45 50 55 15. 1 динен с адресным входом второго блока памяти микрокоманд,. выход поля адреса которого соединен с вторым информационным входом второго блока модификации адреса и с вторым информационным входом первого блока модификации адреса, выходы поля операции первого и второго блоков памяти микрокоманд соединены соответственно с первым и вторым информационными вхо дами мультиплексора, первый, второй и третий информационные выходы которого соединены соответственно с управлением обращения к внешним устрой ствам микропроцессора, с входом кода управления операционного блока и с входам кода управления блока проверки условий, входы начальной установки первого и второго блоков модифика ции адреса соединены с входом начальной установки микропроцессора, информационный вход операционного блока соединен с информационным входом микропроцессора, выход признаков результата, первый и второй информационные выходы операционного блока соединены соответственно с информационным входом блока проверки условий, с первым и вторым информационными выходами микропроцессора, о т - 3 л и ч а ю щ и й с я тем, что, с целью повышения производительности, блок синхронизации содержит три 1 К- триггера, четыре элемента И и два элемента ИЛИ, в микропроцессор введен блок управления переходами, содержащий три элемента И и три элемента ИЛИ, причем входы синхронизации первого, второго и третьего 1 К-триггеров блока синхронизации соединены с первыми входами второго, третьего и четвертого элементов И блока синхронизации и с входом синхронизации микропроцессора, выход первого 1 К- триггера блока синхронизации соеди- нен с первым входом первого элемента ИЛИ блока синхронизации, с управляющим входом мультиплексора, с первым входом второго элемента И и с инверсным входом первого элемента И блока управления переходами, 1 и К- входы и вход сброса первого 1 К-триггера блока синхронизации соединены соответственно с входом логической. единицы микропроцессора и с входом начальной установки микропроцессора, инверсный выход первого 1 К-триггера блока синхронизации соединен с первым входом второго элемента ИЛИ блокасинхронизации, выходы первого и второго элементов ИЛИ блока синхронизации соединены с вторыми входами соответственно второго и третьего элементов И блока синхронизации, выходы второго и третьего элементов Иблока синхронизации соединены с входами синхронизации соответственновторого и первого блоков модификации адреса, выход признака условногоперехода и выход признака безусловного перехода поля перехода первогоблока памяти микрокоманд соединены свторыми входами соответственно второго элемента И и второго элементаИЛИ блока управления переходами, выход признака условного перехода и вы"ход признака безусловного переходаполя управления второго блока памятимикрокоманд соединены с вторыми входами соответственно первого элементаИ и третьего элемента ИЛИ блока управления переходами, выход первогоэлемента И блока управления переходами соединен с первыми входами первого и второго элементов ИЛИ блокауправления переходами, выход второгоэлемента И блока управления переходами соединен с первым входом третьего элемента ИЛИ и со вторым входом первого элемента ИЛИ блока управленияпереходами,. выход второго и третьегоэлементов ИЛИ блока управления переходами соединены с первым входом ун-. равления модификацией адреса соото ветственно первого и второго блоков модификации адреса, выход первого го элемента И блока управления переходами и с вторым входом управлениямодификацией адреса первого и второгоблоков модификации адреса, выход третьего элемента И блока управленияпереходами соединен с первым входомпервого элемента И блока синхронизации, выход первого элемента И блока синхронизации соединен с вторымивходами первого, второго элементов ИЛИ и с входами 1 второго и третьего1 К-триггеров блока синхронизации, инверсный выход второго 1 К-триггераблока синхронизации соединен с вторыми входами первого и четвертогоэлементов И блока синхронизации, инверсный выход третьего 1 К-триггера .блока синхронизации соединен с тре

СмотретьЗаявка

3814118, 19.11.1984

ОСОБОЕ КОНСТРУКТОРСКОЕ БЮРО "ЮГ" ГОЛОВНОГО МОНТАЖНО ТЕХНОЛОГИЧЕСКОГО УПРАВЛЕНИЯ "ЮГ" НАУЧНО-ПРОИЗВОДСТВЕННОГО ОБЪЕДИНЕНИЯ "КАСКАД"

ПУШКАРЕВ ЮРИЙ ЯКОВЛЕВИЧ, ПОЛОНСКИЙ ДМИТРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропроцессор

Опубликовано: 15.09.1986

Код ссылки

<a href="https://patents.su/13-1257657-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор</a>

Предыдущий патент: Устройство для сопряжения цифровой вычислительной машины с внешним устройством

Следующий патент: Устройство для реализации логических функций

Случайный патент: Преобразовательная подстанция электропередачи постоянного тока