Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 633021

Автор: Фридман

Текст

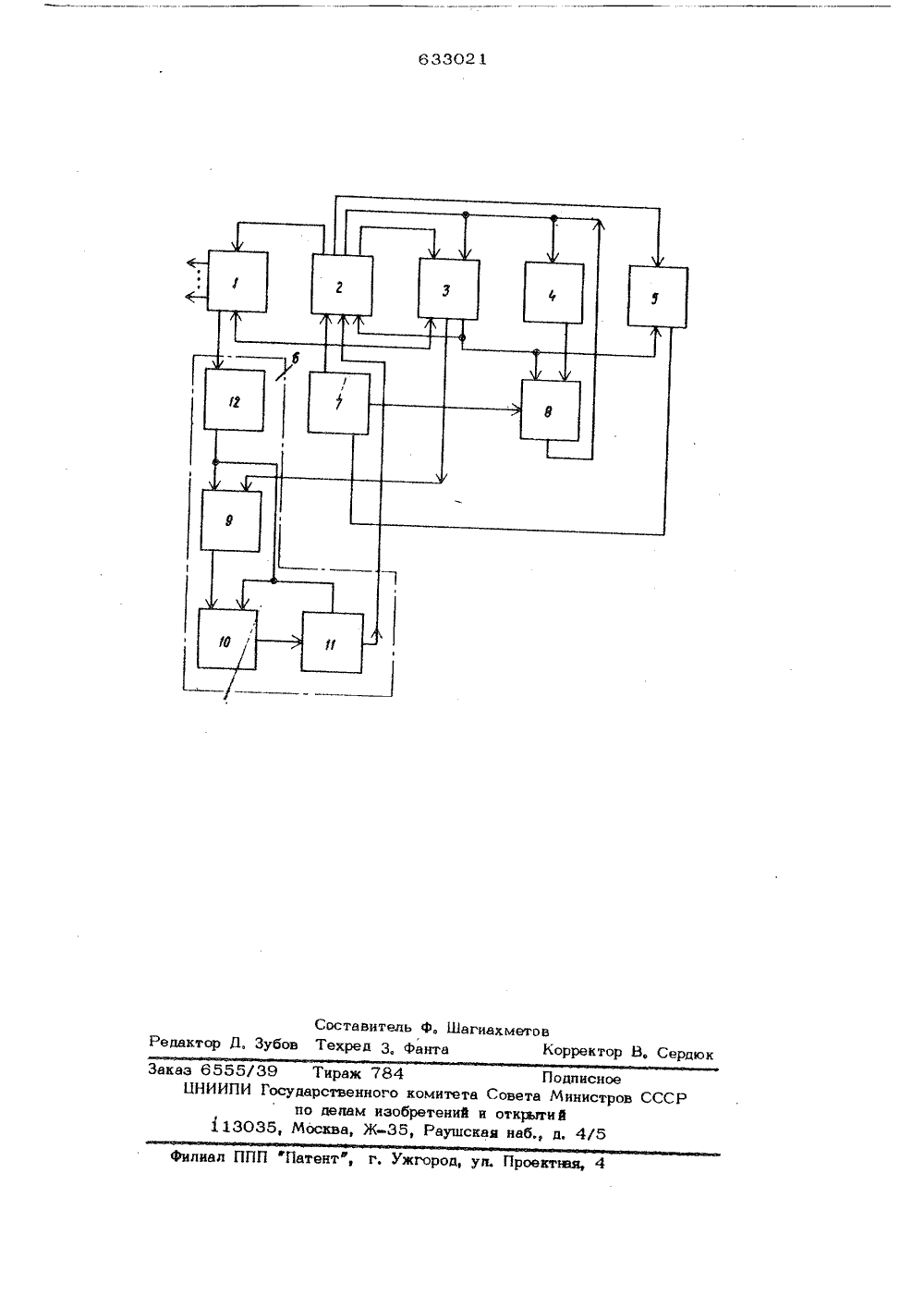

(61) Дополнительное к авт. свил-ву(22) Заявлено 08.07,76 (21) 2382180/18-24 06 Р 15/0006 Г 9/16 присоединением заявки сударстоеннын комнтетоавта Инннстроо СССРпо делам нзобретеннйн отнрмтнй норнтет -43) Опубликовано 15. 11,78 летень М. 53) УЛК 681.3 (088,8) исания 20,11.78 опубликован 2) Автор изобретения(71) Заявитель 54) МИКРОПРОГРАММНЫЙ ПРОЦЕССО Изобретение числительной тцессорам цифр и может быть вычислительно задач,требуюш тичных символ относится к области выехникн, в частности, к провых вычислительных машин использовано дпя ускорения о -процесса при решении их анализа и подсчета иде Известен микропрограммный процессор,содержащий арифметикологический блок,запоминвютпий блок, блок контроля, блок 10синхронизации, блок дешифрации микрокомвнд, блок управления диагностикой, узелконтроля четкости, блок запоминания 1микрокоманд, регистр микрокоманд, дешифраторы горизонтальных и вертикальных 1 Бшин, переключатель режимов, горизонтальные и вертикальные вентили блокировки,блок изменения длительности импульсов,триггеры переключения выборки, инверсииконтроля и инверсии выборки 1,20Недостатком известного процессоразаклинивается в сложности его построенияи в необходимости значительных затратоборудования. 2Наиболее близким к изобретению по технической сущности и достигаемому результату является микропрограммный процессор 121, содержащий врифметико-логический блок, первый выход которого соединен с первыми входами блока зашиты памяти, блока хранении служебной информации и блока управления памятью, блок синхронизации, блок микропрограммного управления, первый вход которого соединен с первым выходом блока управления служебной информации, блок памяти, выход которого соединен со вторым входом блока управления памятью, причем первый вход арифметико-логического блока и вход блока памяти соединены с выходами блока управления памятью, блока защиты памяти и со вторым выходом блока хранения служебной информации, третий и четвертый выходы которого соедине ны со вторыми входами соответственно арифметико-логнческого блока и блока зашиты памяти, вторые входы блока микропрограммного управления и блока хранения служебной информации, третий входарифметико -логического блока соединеныс первым выходом бпока синхронизации,второй и третий выходы которого соединены с третьими входами соответственно блока управпения памятью и блока за-щиты памяти, а группа выходов блокамикропрограммного управления явпяетсягруппой выходов процессора.В известном процессоре анализ и подсчет требуемых симвопов осуществпяется 3 фс помощью поспедоватепьности операций,включающих операцию выделения текущегосимвола, анапиэа выдепенного символа,занесения единицы в счетчиксимвоповпри условии, что текущий символ оказал- Ися искомым, операции сдвига поспедоватепьности машинных слов с цепью анапиза очередного символа и проверку наокончание цикла анапиза и подсчета симво нов. МОсуществление указанной последовательности операций усложняет программирование и увеличивает время вычисленийввиду циклического повторения ряда однотипных операций, что приводит к снижению быстродействия процессора,цепь изобретения - повышение быстродействия.Поставпенная цель достигается тем,что процессор содержит блок анапиза и Зфподсчета символов данных, выполненныйв виде узна формирования управляющихсигнапов, схемы сравнения, элемента И исчетчика, причем выход узла формированияуправпяющих сигнапов соединен с первы- Мми входами схемы сравнения, элементаИ и счетчика, выход схемы сравнения соединен со вторым входом элемента И,выход которого соединен со вторым входом счетчика, а вход узла формирования 4 фуправпяккцих сигналов, второй вход схемысравнения и выход счетчика соединенысоответственно с выходом блока микропрограммного управления, со вторым выхо,дом арифметико-логического бпока и стретьим входом бнока хранения спужебной информации.Структурная схема процессора приведена на чертеже,Процессор содержит блок микропрограм- ффмного управления 1, блок хранения служебной информации 2, арифметико-логический блок 3, блок 4 памяти, блок защитыпамяти 8, блок 6 анализа и подсчета симвоцов данных, блок синхронизации 7, ффбцок 8 управление памятью, а блок анапиза и подсчета символов содержит схемусравнения 9, эаемент И 10, счетчик 11,узел формирования управляющих сигнапов 12.Работает процессор следующим образом.Связанный с блоком микропрограммного управпения 1 узел 12 формирует все сигналы, необходимые для выполнения операции анализа и подсчета символов, Команда подсчета символов выполнена на базе команды сдвига и при выполнении испопьзует все управпяющие сигналы, вырабатываемые командой сдвига. При выпопнении команды подсчета символов, анализируемая информация находится в арифметикологическом блоке 3, а код искомого символа засылается в схему сравнения 9, Анализ символа осуществляется путем сравнения кода анализируемого символа с кодом искомого символа (эталона). В случае совпадения кодов символов через элемент И 10 в счетчик 11 заносится единица. Затем в арифметико-логическом блоке 3 выпопняется операция сдвига поспедова тепьности машинных слов на количество разрядов, определяемое принятым методом кодирования символа (дпя двоичного кода на 1 разряд, дпя восьмиричногона 3 разряда и т.п.), вновь производится сравнение кодов, занесения в спучае равенства кодов единицы в счетчик 11 и т,д, Этот процесс продолжается до тех. пор, пока не будут проверены все симвопы, что задается информацией в команде подсчета символов. В результате в счез- чике 1 1 находится константа, определяемая количеством символов требуемого типа в проверяемой последовательности машинных слов. Затем эта константа пересылается в блок 2 и далее используется по назначению.Использование изобретения существенно сокращает дпитепьность вычислений, что приводит к более эффективному использованию дорогостоящей вычислительной техники. Покажем это.Примем время выполнения стандартной команды равным. йпя анализа и подксчета требуемых символов требуется 5-6 операций, С учетом цикла повторения на анализ последовательности символов длиной О будет затрачено (5-6)пХ единиц времени, В изобретении на весь анапиз затрачивается две операции и время анапиза составпяет 2 к Ф 1 Игде Вовремя выпопнения одного эпементарного сдвига.Конкретно, при работе, например, со словами двойной длины (двоичная инфор6 ЗД 02 14 Микропрограммный процессор, содержащий врифметико-логический блок, пер вый выход которого соединен с первым входами блоха защиты памяти, блока хранения служебной информации и блока управления памятью, блок синхронизации, блок микропрограмного управления, первый вход которого соединен с первым выходом блока хранения служебной информации, блок памяти выход которого соедиУнен со вторым входом блока управления памятью, причем первый вход арифметико- Зу логического блока и вход блока памяти соединены с выходами блока управления, памятью, блока зашиты памяти и со вторым выходом блока хранения служебной информации, третий и четвертый выходы которого соединены со вторыми входами соответственно арифметико-логнчесхого блока и блока защиты памяти, вторые входы блока микропрограмного управления и блока хранения служебной информации, третий вход арифметико-логичесИсточники информации, принятые во34 внимание при экспертизе:1. Авторсхое свидетельство СССР% 474008, кп. Сф 06 х 9/12,б 06 х 11/00, 1972.2. Процессор ЭВМ ЕС,Под обИ шей редакцией А. М. Ларионова, М.,фСтатистика, 1975, с. 4, рис. 1.1. мания) п =64, С учетом того, чтокполучимЮ) к И (5 6)фк бфга+вЬ и - зх погВкТаким образом, изобретение позволяет повысить быстродействие процессора при решении задач анализа и подсчета символов примерно в 100 рвз,Формула изобретения кого блока соединены с первым выходомблока синхронизации, второй и третий выходы которого соединены с третьими ахи"дами соответственно блока управленияпамятью и блоха зашиты памяти, в группа выходов блока микропрограммного управления является группой выходов процессора, о т и и ч а ю ш и й с а тем,что, с целью повышенна быстродействия,он содержит блок анализа и подсчетасимволов данных, выполненный в виде узла формирования упрввпякхцих сигналов,схемы сравнения, элемента И и счетчика, причем выход узда формирования управляющих сигналов соединен с первымнвходами схемы сравнения, элемента И исчетчика, выход схемы сравнения соединен со вторым входом элемента И, выход которого соединен со вторым входомсчетчика, а вход узла формирования управпяюших сигналов, второй вход схемысравнения и выход счетчика соединенысоответственно с выходом блока микропрограммного управления, со вторым выходомарифметике-логического бпокв и с третьим входом блока хранения служебной информации.633021 Составитель Ф. Шагиахметовубов Техред 3, Фанта Корректор В, Серд акаэ 6555/3 ЦНИИПИ Г 113 О 35,лиад ППП "Патент", г. Ужгород, уп. Проектная, 4 Тираж 784дарственного комитета по дедам иэобретений и Москва, Ж, Раушск ПодписноеСовета Министров СССРоткити йа наб., д, 4/5

СмотретьЗаявка

2382180, 08.07.1976

ПРЕДПРИЯТИЕ ПЯ А-7306

ФРИДМАН ЗУСЬ ШИМОНОВИЧ

МПК / Метки

МПК: G06F 17/00, G06F 9/22

Метки: микропрограммный, процессор

Опубликовано: 15.11.1978

Код ссылки

<a href="https://patents.su/4-633021-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Устройство для контроля двух параллельно работающих счетчиков

Следующий патент: Устройство для коммутации процессоров многопроцессорной цифровой вычислительной машины

Случайный патент: Рабочая клеть трубопрокатного стана