Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

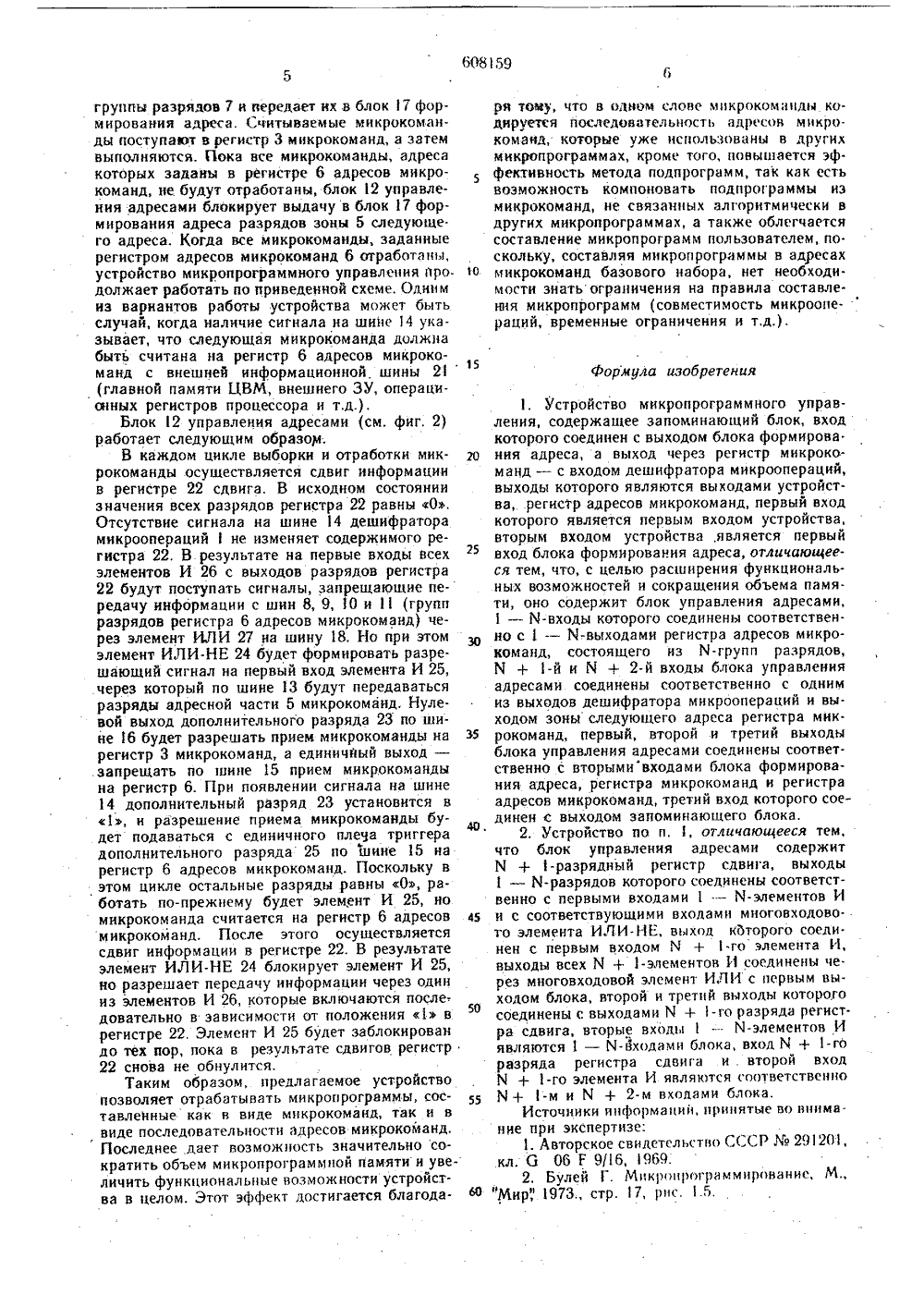

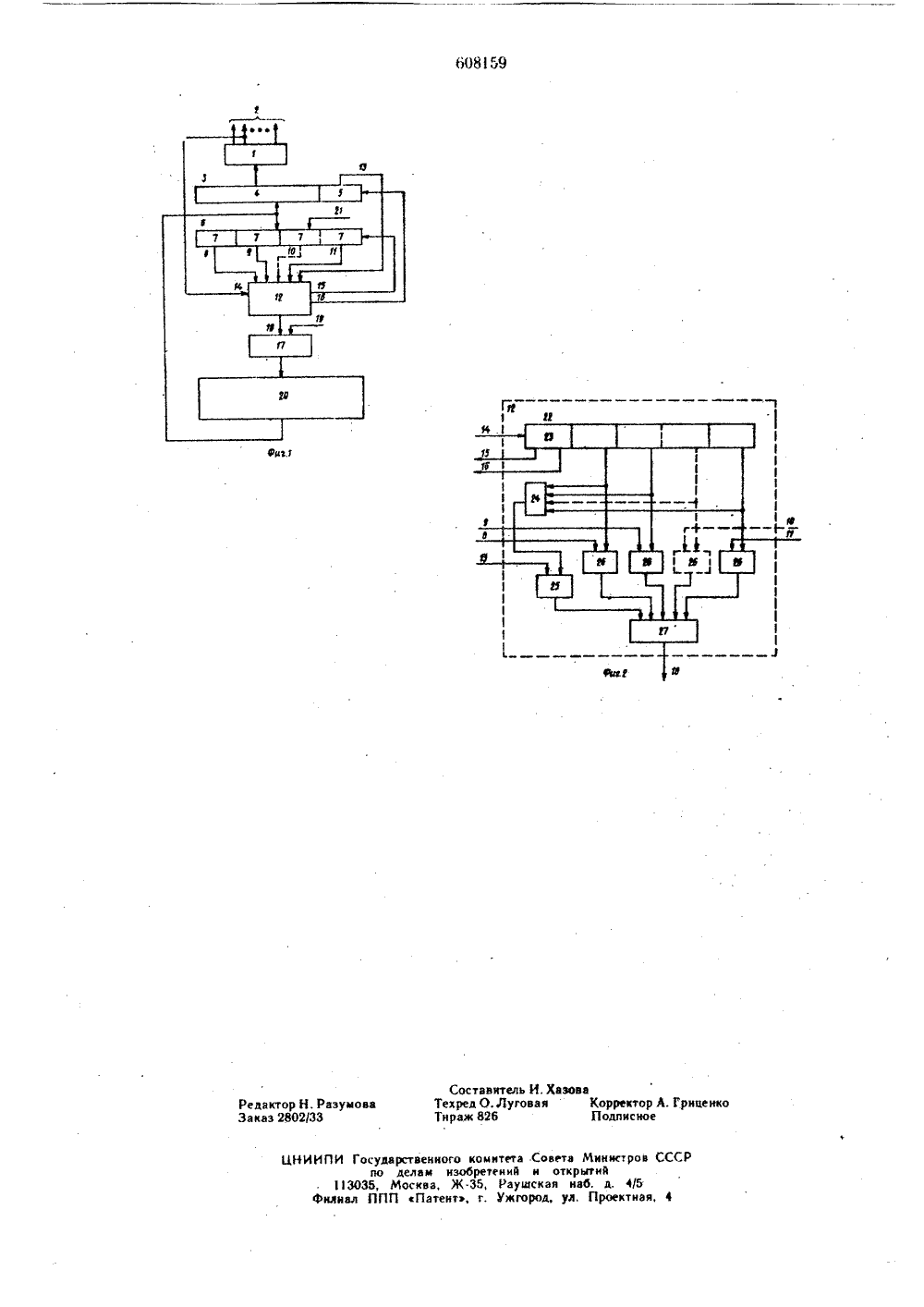

Сфез Советских Сфааиаюстмчеовх Рееаубяик(5 Ц И. Кл, 606 Р 9/16 некием заявки Итет и исо ГащдарстьаязВФ хамюат Саеатв аанаатраа С ае делам изебретаяхй в етхрытнй, Папагин и В. А. Иванов ена Ленина институт кибернетики Акапем наук Украинской ССР(54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕН Изо тельной нения ци ровторым входом устод блока формироъема функ- икробретение относится к области вычислитехиикн н предназначено для примев устройствах управления электронныхф ых вычислительных машин.Известно устройство микропрограммного управления, содержащее генератор тактовых импульсов, запоминающее устройство, вход которогс подключен к выходу схемы формирования адреса, а выход - к входу регистра микрокоманд; регистр микрокоманд состоит из операционной и адресной частей, причем выход операционной части подключен к входу дешифратора микроопераций, а выход адресной части - к входу схемы формирования адреса, которая также подключена к,шине условий переходов .Недостатками известного устройства являются большой объем памяти и низкие функциональные возможности.Наиболее близким к предложенному по тех. иической сущности является устройство микропрограммного управления, содержащее запо.мннающий блок, вход которого соединен с выходом блока формирования адресаа выход через регистр микрокоманд - с входом дешнфратора микрооперацнй, выходы которого являются выходами устройства, регистр адресов микрокоманд, первый вход которого является первым входом устронства, вройства является первый вхвания адреса 2.Известное устройство обладает большимобъемом микропрограммной памяти и низкимив функциональными возможностями при добавлении новых микропрограмм.Действительно, уменьшение объема микропрограммной памяти в таком устройстве дости.гается за счет объединения одинаковых участков микропрограмм, иначе говоря, зэ счет микропрограммных подпрограмм. Это требует при каждом переходе на подпрограмму запоминания адреса возврата и затем его восстанавливания. Кроме того, оказывается невозможной компоновка подпрограмм, объединяющих микЬ рокоманды, не являющиеся алгоритмнчески (содержательно) г.язанными последовательностями в других микропрограммах.Цель изобретения - уменьшение обмикропрограммной памяти и увеличение цнональных возможностей устройства м и рограммного управления.Зто достигается.тем, что устройство микро.программного управления содержит блок управления адресами, 1 - М-входы которого сое.динены соответственно с- Х-выходамн ре-гистра адресов мнкрокоманд, состоящего нзИ-групп разрядов, И + 1-й и И + 2-Р входыблока управления адресами соединены соответ.ственно с одним из вЫходов дешифратора микроопераций и выходом зоны следующего адре.са регистра мнкрокоманд, первый, второй итретий выходы блока управления адресами соединены соответственно с вторыми входами блока формирования адреса, регистра микрокоманд и регистра адресов микрокоманд, третийвход которого соединен с выходом запоминающего блока, а блок управления адресами содержит И + 1-разрядный регистр сдвига, выходы 1 - И.разрядов которого соединены соответственно с первыми входами 1 - И элементов И и с соответствующими входами многовходового элемента ИЛИ.НЕ, выход которогосоединен с первым входом И + 1.го элемента И,выходы всех И + 1 элементов И соединены через многовходовой элемент ИЛИ с первым выходом блока, второй н третий выходы которогосоединены с выходами И + 1-го разряда регистра сдвига, вторые входы 1 - 1 ФэлементовИ являются 1. - И-входами блока, входИ + 1-го разряда регистра сдвига и второйвход И + 1 го элемента И являются соответственно И + 1-м и И + 2-м входами блока.Устройство микропрограммного управленияпозволяет отрабатывать микропрограммы, сос. тавленные как в виде микрокоманд, так и ввиде последовательности адресов микрокоманд.Это дает возможность значительно сократитьобъем микропрограммной памяти и увеличитьфункциональные возможности устройства в целом за счет того, что в одном слове микрокоманды может коднроваться последователь-ность адресов нескольких микрокоманд, которые уже использованы в других микропрограммах.На фиг. 1 приведена принципиальная схемаустройства,на фиг, 2 - структурная схемаблока управления адресами,Устройство микропрограммного управлениясодержит дешифратор 1 микроопераций с выходами 2, регистр 3 мнкрокоманд с операцион ной зоной 4 и зоной 5 следующего адреса,регистр 6 адресов микрокоманд, содержащийИ-групп разрядов 7, которые по шинам 8, 9,10, 11.подключены к соответствующим входамблока 12 управления адресами, К блоку 2 пошине 13 подключены также разряды зоны 5следующего адреса регистра 3 микрокоманд,а по шине 14 - один из выходов 2 дешифратора 1 микроопераций, Выходы 15 и 16 блокауправления 12 адресами подключены к управляющим входам регистра 3 микрокоманд ирегистра 6 адресов микрокоманд соответственно. Выходы блока 17 формирования адреса(микрокоманды) по шине 18 подключены к выходу блока 12 управления адресами, а по шине19 - к схемам, вырабатывающим сигналы, которые должны вызвать ветвления в микропрограммах (на схеме не показаны), Выход блока17 подключен к входу запоминающего блока 20причем выход последнего подключен к входамрегистра 3 микрокоманд и регистра 6 адресовмикрокоманд. Цифрой 2 обозначена шина, покоторой регистр 6 адресов мнкрокоманд может соединяться с регистрами или главной памятьювычислительной машины. В качестве регистра 6адресов микрокоманд может использоватьсяодин из регистров операционного устройствацифровой вычислительной машины,5 блок 12 управления адресами (см. фнг. 2)содержит И + 1-разрядный регистр сдвига 22с И + 1-ым дополнительным разрядом 23, многовходовый элемент ИЛИ-НЕ 24, многоразрядный элемент И 25, .многоразрядные элементыИ 26 и многовходовый элемент ИЛИ 27,Вход И + 1-го разряда 23 подключен кшине 14, а прямой и инверсный выходы - кшинам 15 и 16 соответственно. Единичные выходы остальных И-разрядов подключены к входам элемента ИЛИ-НЕ 24 и к первым входам15 алементов И 26, к вторым входам которых подключены шины 8, 9, 10 и 1 соответственно.Выход элемента ИЛИ-НЕ 24 подключен к первому входу элемента И 25, к второму входукоторого подключена шина 3. Выходы всехэлементов И 25, 26 подключены к входам элемента ИЛИ 27, имеющего выход 18.Принцип работы устройства заключается вследующем.В первом такте на регистр 3 микрокомандиз запоминающего блока 20 считывается микро 2 з команда. Во втором такте в зависимости отзначений разрядов операционной зоны 4 (мнкрокоманды) дешифратор 1 микроопераций вырабатывает управляющие сигналы, которые пошинам 2 поступают в устройства и схемы цифровой вычислительной машины. В этом жетакте в блок 12 управления адресами по шине 13 из зоны 5 следующего адреса (микрокоманды) поступает код, определяющий адресследующей микрокоманды, который затем передается в блок 7 формирования адреса. Этотадрес модифицируется в зависимости от выполнения различных логических условий (сигналовна шинах 19) и поступает на адресный входзапоминающего блока 20. На этом цикл выборки и отработки микрокоманды заканчивается. Если в результате отработки микрокоманф ды на шине 14 не появляется сигнал, то вновом цикле в первом такте блок 12 управления адресами по шине 16 вырабатывает сигнал, разрешающий прием на регистр 3 микрокоманд новой микрокоманды, и устройство микропрограммного управления работает в дальнейшем по этой же схеме.Если же в результате отработки микрокоманды на шине 14 появляется сигнал, то впервом такте следующего цикла блока 12 управления адресами по шине 15 вырабатывает50 сигнал, разрешающий прием новой микрокоман.ды на регистр 6 адресов микрокоманд, На шине 16 при этом сигнал отсутствует.Микрокоманде принятая на регистр 6 адресов микрокоманд, рассматривается как микрокоманда; содержащая совокупность адресовмикрокоманд, Которые должны быть последовательно выполнены. Эти адреса располагаются в группах разрядов 7. Обработка микрокоманды, принятой на регистр 6 адресов микрокоманд; заключается в том, что блок 2 уп-,равлеиия адресами последовательно выбираетформула изобретения 15 20 25 30 35 45 нен с первым входом Я + 1-го элемента 11,выходы всех М + 1-элементов И соединены через многовходовой элемент ИЛИ с первым выходом блока, второй и третий выхолы которогосоединены с выходами М + 1-го разряда регистра сдвига, вторые входы 1И-элементов Иявляются 1 - Н-Йходами блока, вход И + 1-горазряда регистра сдви га и . второй входХ + 1-го элемента И являются еослветственно55 Н+ 1-м и М + 2-м входами блока.Источники информации, принятые во внимание при экспертизе:1. Авторское свидетельство СССР291201,.кл. б 06 Г 9/16, 1969.2. Булей Г. Мпкронрограммированис, М60 "Мир" ,1973., стр. 17, рис. 1.5,группы разрядов 7 и передает их в блок 17 формирования адреса. Считываемые микрокоманды поступают в регистр 3 микрокоманд, а затем выполняются. Йока все микрокоманды, адреса которых заданы в регистре 6 адресов микро- команд, не будут отработаны, блок 12 управления адресами блокирует выдачу в блок 17 формирования адреса разрядов зоны 5 следующе.го адреса. Когда все микрокоманды, заданные регистром адресов микрокоманд 6 отработаны, устройство микропрограммного управления продолжает работать по приведенной схеме. Одним из вариантов работы устройства может быть случай, котла наличие сигнала на шине 14 указывает, что следующая микрокоманда должна быть считана на регистр 6 адресов микрокоманд с внешней информационной, шины 21 (главной памяти ЦВМ, внешнего ЗУ, операционных регистров процессора и т.д.).Блок 12 управления адресами (см. фиг. 2) работает следующим образо)ю;В каждом цикле выборки и отработки микрокоманды осуществляется сдвиг информации в регистре 22 сдвига, В исходном состоянии значения всех разрядов регистра 22 равны О.Отсутствие сигнала на шине 4 дешифратора микроопераций 1 не изменяет содержимого регистра 22. В результате на первые входы всех элементов И 26 с выходов разрялов регистра 22 будут поступать сигналы, запрещающие передачу информации с шин 8, 9, 10 и1 (групп разрядов регистра 6 адресов микрокоманд) через элемент ИЛИ 27 на шину 18, Но при этом элемент ИЛИ-НЕ 24 будет формировать разрешающий сигнал на первый вход элемента И 25, через который по шине 13 будут передаваться разряды адресной части 5 микрокоманд. Нулевой выход дополнительного разряда 23 по шине 16 будет разрешать прием микрокоманлы на регистр 3 микрокоманд, а единнчйый выход - .запрещать по шине 15 прием микрокоманды на регистр 6. При появлении сигнала на шине 14 дополнительный разряд 23 установится в 1, и разрешение приема микрокоманды будет подаваться с единичного плеча триггера дополнительного разряда 25 по шине 15 на регистр 6 адресов микрокоманд, Поскольку в этом цикле остальные разряды равны О, работать по-прежнему будет элемент И 25, но микрокоманда считается иа регистр 6 адресов микрокоманд, После этого осуществляется сдвиг информации в регистре 22, В результате элемент ИЛИ-НЕ 24 блокирует элемент И 25, но разрешает передачу информации через один из элементов И 26, которые включаются после-. довательно в зависимости от положения 1 в регистре 22. Элемент И 25 булет заблокирован ло тех пор, пока в результате сдвигов регистр 22 снова не обнулится.Таким образом, предлагаемое устройство позволяет отрабатывать микропрограммы, составленные как в виде мнкрокоманд, так и в виде последовательности адресов микрокоманд, Последнее дает возможность значительно сократить объем микропрограммной памяти и увеличить функциональные возможности устройст. ва в целом, Этот эффект достигается благода. ря тому, что в одном слове мнкрокоманды кодируется последовательность адресов м и крокомэнл, которые уже использованы в лругих микропрограммах, кроме того, повышается эффективность метола полпрограмм, так как есть воэможность компоновать подпрограммы из микрокоманд, не связанных алгоритмически в других микропрограммах, а также облегчается составление микропрограмм пользователем, по. скольку, составляя микропрограммы в адресах микрокоманд базового набора, нет необходи. мости знать ограничения на правила составле. ння микропрограмм (совместимость микроопераций, временные ограничения и т.д.). 1. Устройство микропрограммного управления, содержащее запоминаюсций блок, вход которого соединен с выходом блока формирова. ния адреса, а выход через регистр микрокоманд - с входом дешифратора микроопераций, выходы которого являются выходами устройства, регистр адресов микрокоманд, первый вход которого является первым входом устройства, вторым входом устройства, является первый вход блока формирования адреса, отличающееся тем, что, с целью расширения функциональных возможностей и сокращения объема памя. ти, оно содержит блок управления адресами, 1 - М-входы которого соединены соответствен. но с 1 - Х-выходами регистра адресов микро- команд, состоящего из М-групп разрядов, Х + 1-й и И + 2-й входы блока управления адресами соединены соответственно с одним из выходов дешифратора микроопераций и вы. холом зоны следующего адреса регистра мик. рокоманд, первый, второй и третий выходы блока управления адресами соединены соответственно с вторымивходами блока формирования адреса, регистра микрокомаид и регистра адресов микрокоманд, третий вход которого соединен с выходом запоминающего блока.2. Устройство по и, 1, отличающееся тем, что блок управления адресами содержит Ы + 1-разрядный регистр сдвига, выходы 1 - И-разрядов которого соелинены соответственно с первыми входами 1 - И-элементов Р и с соответствующими входами многовхолово то элемента ИЛИ-НЕ, выход которого соелиИ ком 1или Государственногопо делам изоб 3035, Москва, Ж ал ППП Патент ета Совета Министров ССиА н открытнАаущская наб. д. 4/5жгород, ул, Проектная, 4

СмотретьЗаявка

2153602, 04.07.1975

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УКРАИНСКОЙ ССР

СЫРОВ ВИКТОР ВАЛЕНТИНОВИЧ, ПАЛАГИН АЛЕКСАНДР ВАСИЛЬЕВИЧ, ИВАНОВ ВЛАДИМИР АНДРЕЕВИЧ

МПК / Метки

МПК: G06F 9/16

Метки: микропрограммного

Опубликовано: 25.05.1978

Код ссылки

<a href="https://patents.su/4-608159-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Устройство для суммирования единиц

Следующий патент: Центральный процессор

Случайный патент: Машина для контактной точечной сварки