Способ исправления ошибок в системах связи

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 568177

Автор: Гордеев

Текст

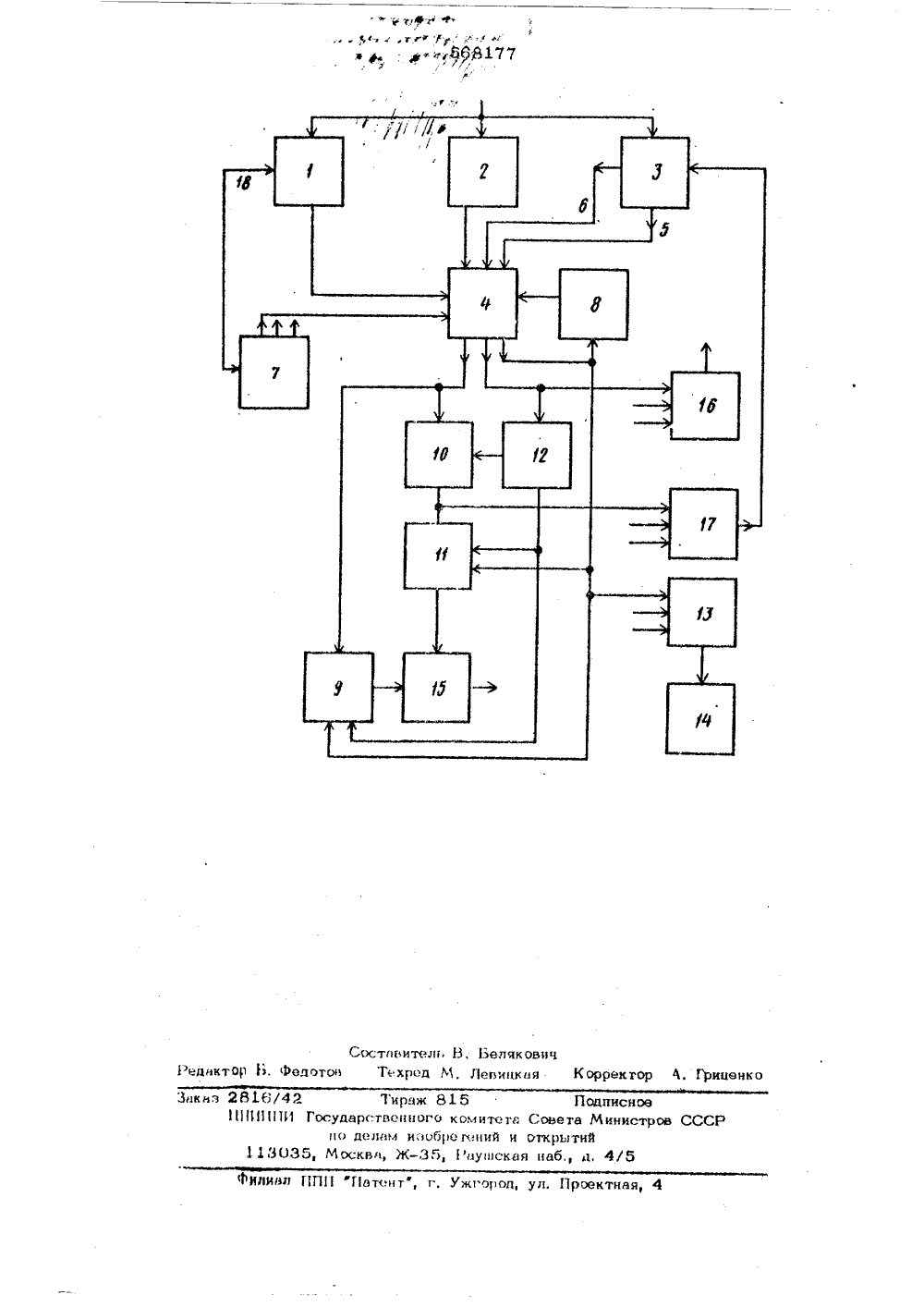

. 08,74 (21) 20554 38/О с присоединен заявк ооударотвенныи иоииСоввтв Министров СССна делам изоаретенини открытийОпублик 5) Дата опубликования описания 19.09.7 2) Автор изобретения В. Гордее Ц Заявитель 54) СПОСОБ ИСПРАВЛЕНИЯ ОШИБ В СИСТЕМАХ СВЯЗИте кодовые комбнаружены во редачи, и запомиринятые безИзобретение относится к радиотехнике,может использоваться в системах связис многократным повторением сообщенийИзвестен способ исправления ошибок всистемах связи, состоящий в замене иск 4 женных комбинаций комбннациямн, принятыми без ошибок, причем в случае подачисигнала запрос на приемной стороне анализируются СЧ кодовых комбинаций, и запрашнваемая кодовая комбинация принимаетсятолько в том случае, когда все тч комбинаций приняты без ошибок. В случае обнаружения ошибок хотя бы в одной из комбинаций все эти комбинации стираются 1),, Однако прн известном способе необходима передача сигнала "запрос на повторениесообщения,Наиболее близок к предлагаемому способисправления ошибок в системах связи с многократным повторением сообщений, состоящих нз кодовых комбинаций обнаруживающего кода, заключающийся в приеме кодовыхкомбинаций анализе н обнаружении в первом цикле перс,дачи ицибок в каждой кодэвой комбинации, В последующих циклах передачи анализируют толькобинации, в которых ошибки овсех предыдущих циклах пенают кодовые комбинации, пошибок2.Однако и при этом способе продолжательность обработки сигналов, необходимая дляприема всех кодовых комбинаций сообщения,весьма велика.Бель изобретения - ускорение обработкисигналов при исправлении ошибок в системахсвязи.Предлагаемый спосссб исправления ошибок в системах связи с многократным повторениемсообщений, состоящих из кодовых комбннаций обнаруживающего кода, заключающттйсяв приеме ходовых комбинаций, анализе и обнаруженист, в первом цикле передачи ошибокв каждой кодовой комбинации, анализе в щ последующих циклах передачи только тех кодовых комбинаций, и которых ошибки обнаружены во всех предыдуших циклах передачи,и запоминании кодовых комбинаций, принатых без ошибок, отличается тем, что допол- О ннтльно запоминают кодовые комбинациис ошибками за заданное число циклов передачи, для каждой иэ которых поэлемецгноисправляют ошибки по критерию большинства выделяют исправленные кодовые комбинации и запоминают их, а кодовые комбинапии, в которых обнаружены оцгибки послеисправления стирают,На чертеже представлена структурнаяэлектрическая схема для реализации способа исправления ошибок в системах связи 1 О;число кодовых комбинаций в сообщении равно четырем, а заданное число циклов, послекоторого исправляются ошибки, равно трем).Устройство содержит блок 1, выявляющий признак начало сообщения, блок памя- дти 2 емкостью ца одну кодовую комбинацию,блок обнаружения ошибок 3, входы которыхявляются входом устройства, блок сгробирования 4, информационные входы которогоподсоединены к выходу блока памяти 2 и вы-УОходам 5 и 6 блока обнаружения ошибок 3,а сгробирующие - к вцходу блока 1, к соответствующему выходу приемного распределителя 7 на четыре кодовые комбинациии выхолу триггера блокировки 8 ключ 9, 25один из управляющих и информационныйехэры кэгэрэгэ пэдсэедицецы к соэгвегствукщил еьхэлал блэка сгрэбирэеанця 4 блок10 цсираелеция ошибок е кодовых эиеллентах, информационный вход кэгорэгопэдсоецииец к соответствующему выходу блокасгрэбирэвация 4, а выход - к информационному входу кгцоча 11, счегчик 12 ца три,вход кэгэрэгэ иэдсэелииеи,к соответствующему выходу блока стрэбирования 4, а вы, З 5ход - к управляющим входам блока 10 иключей 9 и 11, элемент ИЛИ 13 ца тривхода, каждый цз которых соединен с соэтеагсгеуюшим выходом блока стробировация4, ц цыхэл - сэ счегчикэм 14 числа приня Огых комбинацийэлемент ИЛИ 15, входыкоторого соединены с выходами ключей Ои 11, а выход является выходом устройстваблэк 16 формирэваиия сигнала запрос,каждый из грех ехэлэв когорэпо соединенс соответствующим выходом блока стрэбирования 4, а выход - сэ вхэлэм обратного капала, алемецг ИЛИ 17, каждый изтрех ехэлоц которого сжлциеи с выходомблэка 10, а выход - с сэогветсгвующимзхэлэм блэка обнаружения э 1 ццбэк 3, Вход18 блэка 1 соединен с выходом приемногорасцрслэлителя 7,Усгрэйстео рабогаег следующим образомЗакэпирэеццэе соэбшецие, состоящее иэчетл 1 рех кодовых комбинаций, поступаетна вхэлы блэка 1 блока цамягц 2 и блокаобцаружс цця ошибок 3, В момецг окончания приама иервэй кодовой комбинации, вкэгэрэй сэпэржцгся признак начало сооб- ф щения", ца лругэй вход блока 1 поступ и.тсигнал с приемного распределителя 7 ипри отсутствии ошибок и кодовой комбицации на его выходе появляется сигнал, означающий начало приема сообцеция,Вторая кодовая комбинация записывается в блок памяти 2 и проверяется в блокеобнаружения ошибок 3 на отсутствие ошибок, Если оццгбки нег в момент окончания,ее приема разрешающий сигнал с выхода5 поступает через блок стробировация 4на управляюцие входы ключей 9 и 11, аинформация с блока памяти 2 через блокстробирования 4 поступает на информационный вход ключа 9. На другие управляющие входы ключей 9 и 11 поступаетсигнал со счетчика 12, который разрешаетпрохождение информации через ключ 9 иэлемент ИЛИ 15 ца выход устройстваи одновременно запрещает прохождениеинформации из блока ТО через ключ 11,Кроме входов ключей 9 и 11 сигнал свыхода 5 через блок стробирования 4 пь.дается на триггер 8 блокировки и черезэлемент ИЛИ 13 - на счетчик 14, Счетчик фиксирует факт приема одной кодовойкомбинации, а на выходе триггера 8 появляется сигнал, запрещающий дальнейшеепрохождение информации из блока памяти 2и сигналов из блока обнаружения ошибок3 через блок стробирэвания 4 иа ключи9 и 11, блок 10, счетчик 11, элементИЛИ 13 и блэк 16,В случае обнаружения ошибки в блокеобнаружения ошибок 3 ца выходе 6 вырабатывается сиг нал запрос, которыйпройдя через блок стробирэвация 4, фиксируется счетчиком 12 и через блок 16поступает на вход обратного канала. Одновременно с,этим информация из блокапамяти 2 поступает через блок стробцровация 4 в блок 10 исправления оиибок изапоминается в нем,Принятая повторно (во втором циклепередачи) вторая кодовая комбинация проверяется гак же, как и в первом цикле.Прц згэм, в случае обнаружения в нейошибок, она повторно запоминается бльком 10.При обнаружении ошибки во второйкодовой комбинации во всех трех циклах пэлрял и блоке 10 пэ сигналу счегчика12 поэлементно исправляются ошибки вискаженной информации кратности ( +1 )включительно, Исправленная кодовая комбинация поступает через алемецт ИЛИ 17е блэк обнаружения эшцбкк 3 для проверкиЕсли ошибки в ией иет, ца выхэлэ 5 пэявляется сигнал разрешения, который чер иблок стробировация 4 поступаег ца элиц цзуправляюних входов ключей 0 и 11. Сигналсо счетчика 12, поступающий на другиеуправляющие входы ключей 9,11, разрепаетпрохождение информации из блока 10 через ключ 11 на элемент ИЛИ 15 и далеена выход, одновременно запрещая прохож денне искаженной информации из блока памяти 2 через ключ 9,В случае обнаружения ошибки в исправленной кодовой комбинации информация,хранящаяся в блоке 10, по окончаниитретьего цикла стирается, и в следующем+цикле передачи вторая кодовая комбинацияпроверяется так же, как и в первом цикле.Блоки, принимающие две другие кодовыекомбинации, не изображенные, на чертеже,содержат каждый: блок стробирования 4,триггер 8, ключи 9 и 11, блок 10, счетчик12, элемент ИЛИ 15 и работают аналогично. После приема всех четырех кодовыхкомбинаций на выходе счетчика 14. числапринятых кодовых комбинаций появляетсясигнал, который обнуляет все схемы устройства и возвращает триггеры 8 в исходное состояние, Все схемы обнуляются блоком 16 в тех случаях, когда исчерпывается максимальйо допустимое число циклов це .редачи данного сообщении.Блок 16 формирования сигнала "запросфработает так, что за время приема одногоцикла сигнал запрос" вырабатывается только один раз, независимо от того, одинили несколько сигналов поступает на ее входыэа этот цикл.Совместное выполнение операций по ис-Мправлению ошибок в кодовых комбинацияхи кодовых элементах с последующей проверкой исправленных кодовых комбинаций помолает уменьшить затрачиваемое на исправленне опнбок времболее, чем нп 50 .л 1 п нию с известньм способом прн .полно.пппп избьточого коде и ( ) щ 42 (24) и ;- боте по Ъаналу с вероятностьо опбки в пем Р 2 10 без снижения достоверности прин- той информации:Формула изобре теинСпособ исправления ошибок в системах свэи с многократным повторением сообнениА,состоящих из кодовых комбинаций обнаруживеощего кода, заключающийся в приеме кодовыхкомбинаций, анализе и обнаружении в первомцикле передачи ошибок в каждой кодовой комбинации, анализе в последукмцих циклах передачи только тех кодовых комбинаций, в которых ошибки обнаружены во всех предыдушихциклах передачи, и запоминания кодовых комбинаций, принятых беэ ошибок, о т л и ч а ющ и й с я тем, что, с целью ускорения обработки сигналов, дополнительно запоминаюткодовые комбинации, принятые с ошибками,выявляют одноименные кодовые комбинациис ошибками эа заданное число пиклов перодачи, для каждой из которых поэлементноисправляют ошибки по критерию большинства, выделяют исправленные кодовые комбинации и запоминают нх, а кодовые комбинации, в которых обнаружены ошибки пооле исправления, стирают,Источники информации, принятые во внимание при экспертизе;1. Авторское свидетельство К 187395,С 06 . 11/08, 1966.2, Патент США М 3428944,кл, 340-1461 . 1969,

СмотретьЗаявка

2055438, 23.08.1974

ПРЕДПРИЯТИЕ ПЯ Г-4173

ГОРДЕЕВ НИКОЛАЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 11/08, H03M 13/51

Метки: исправления, ошибок, связи, системах

Опубликовано: 05.08.1977

Код ссылки

<a href="https://patents.su/4-568177-sposob-ispravleniya-oshibok-v-sistemakh-svyazi.html" target="_blank" rel="follow" title="База патентов СССР">Способ исправления ошибок в системах связи</a>

Предыдущий патент: Приемное устройство с циклической синхронизацией

Следующий патент: Устройство для разнесенного адаптивного приема сигналов частотной телеграфии

Случайный патент: Пневматический сортировочный стол для сыпучих смесей