Устройство для обнаружения многократных и исправления одиночных ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1718387

Авторы: Ашанин, Квелашвили, Коваленко, Малофей, Сапожников

Текст

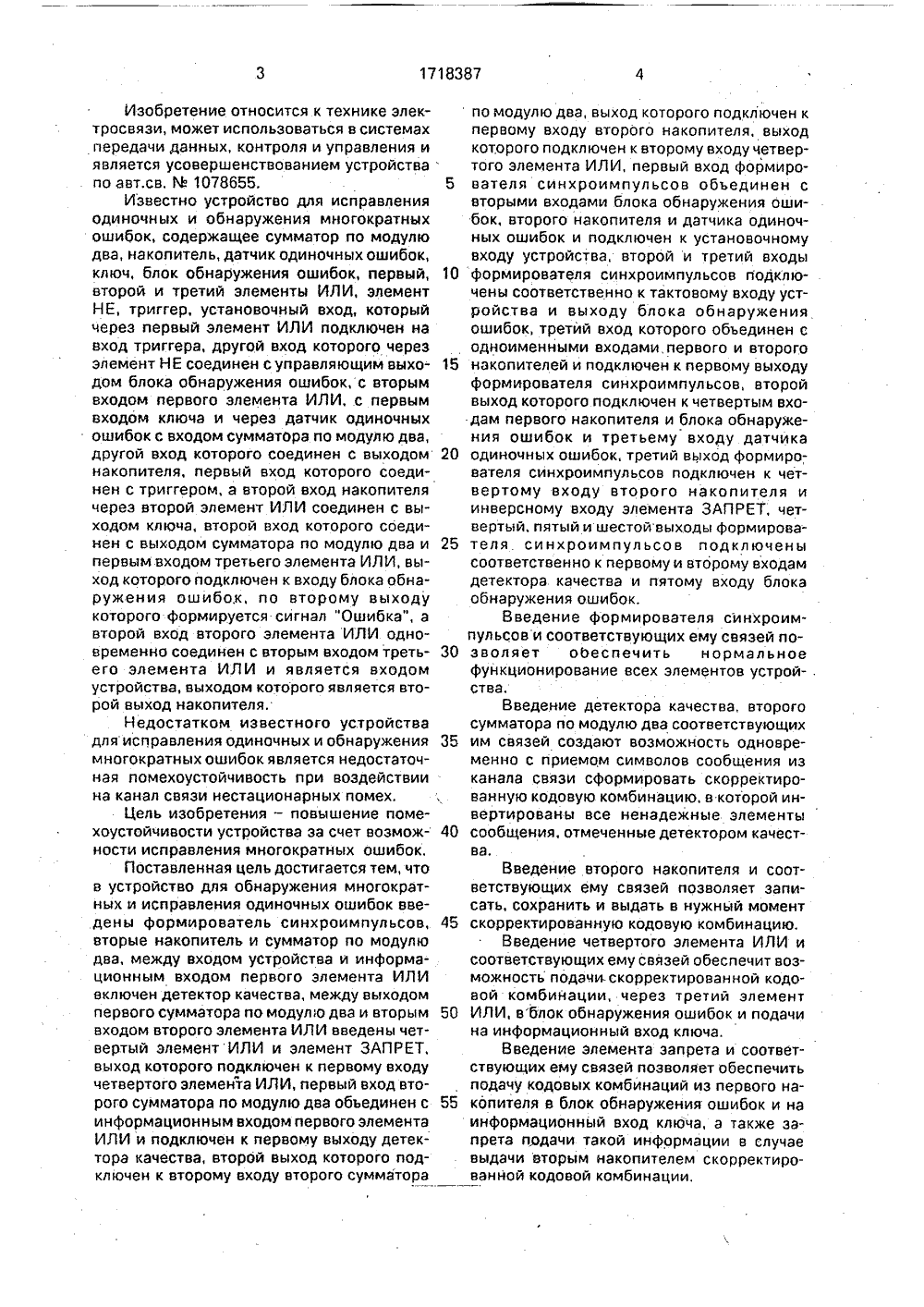

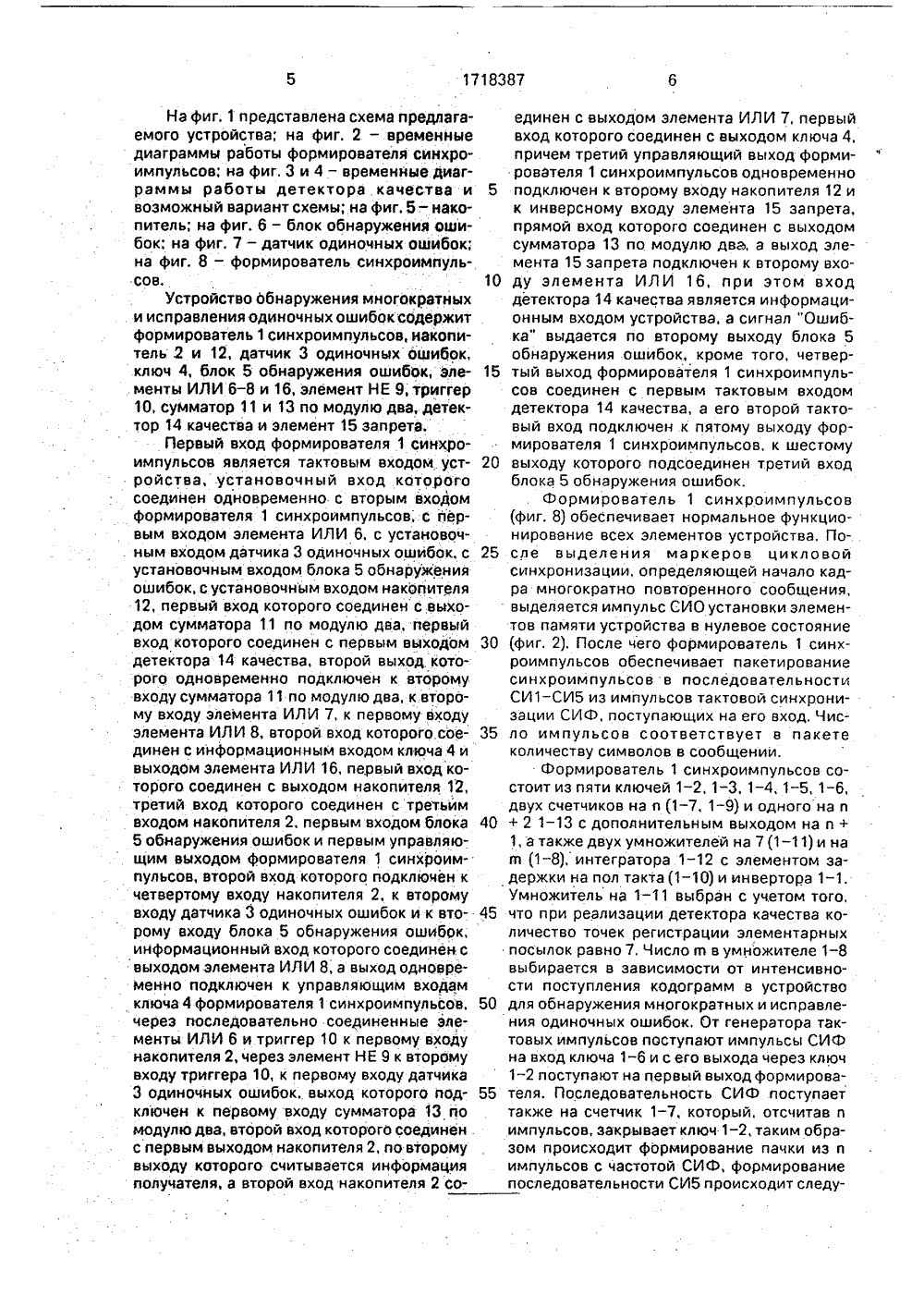

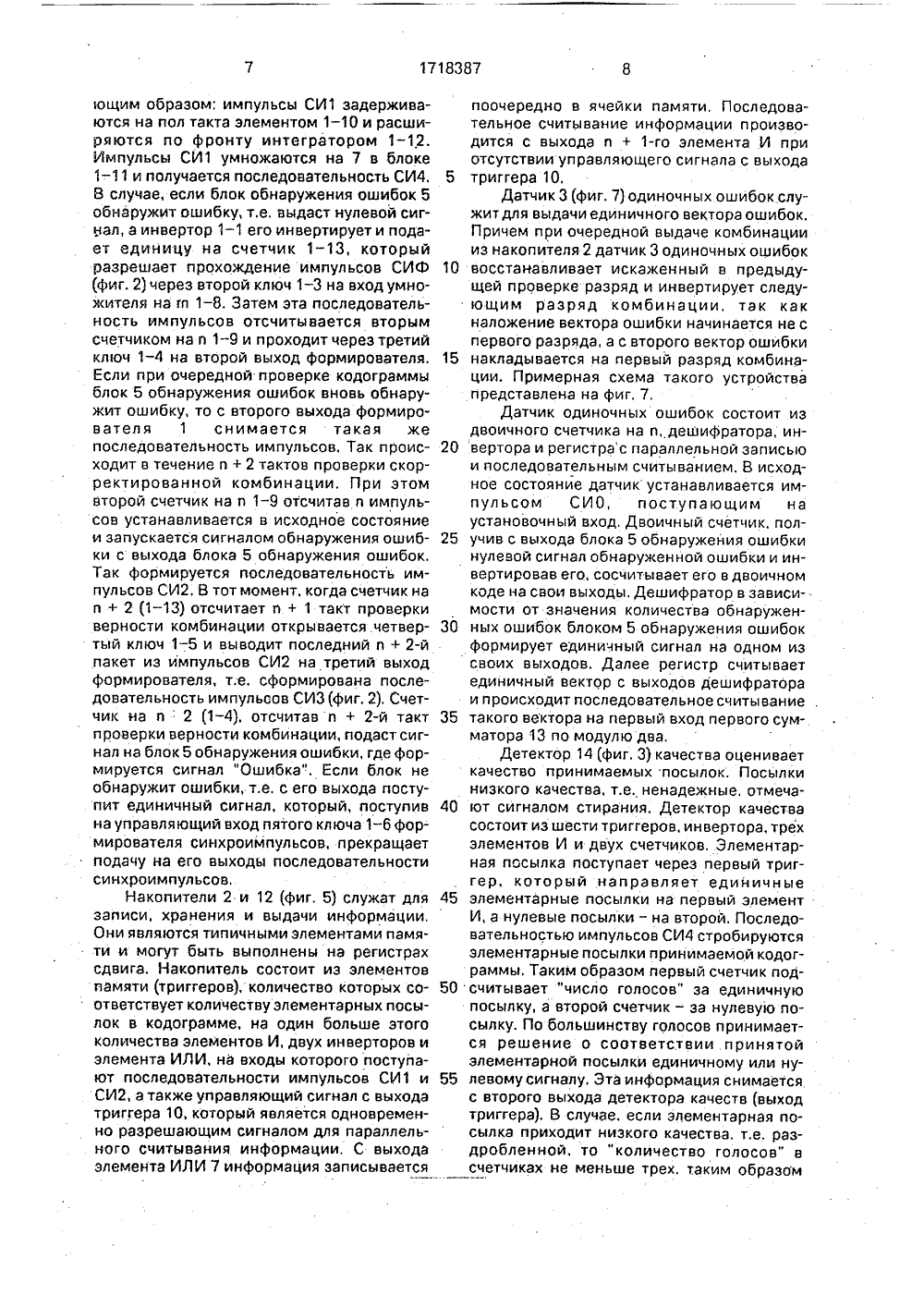

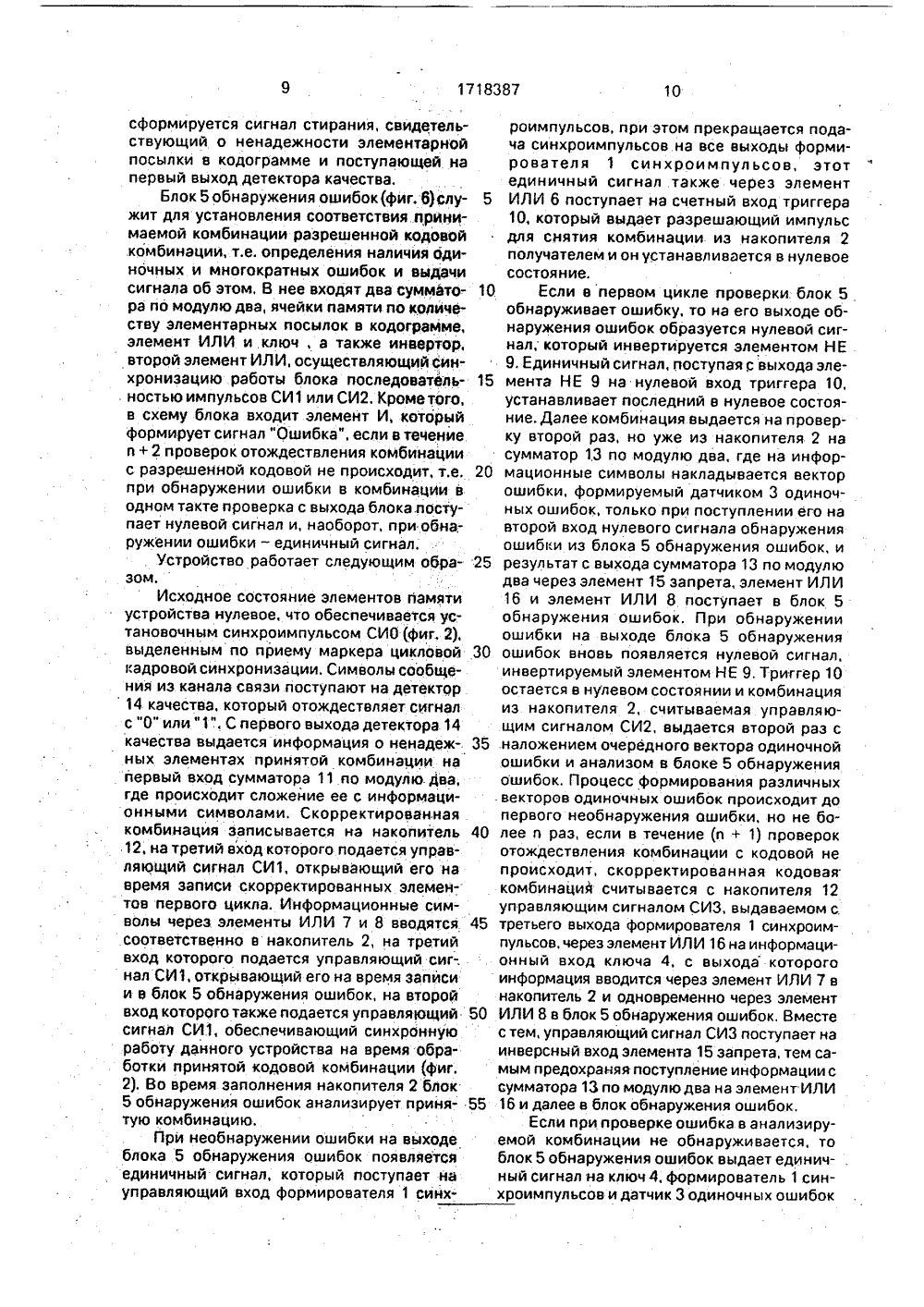

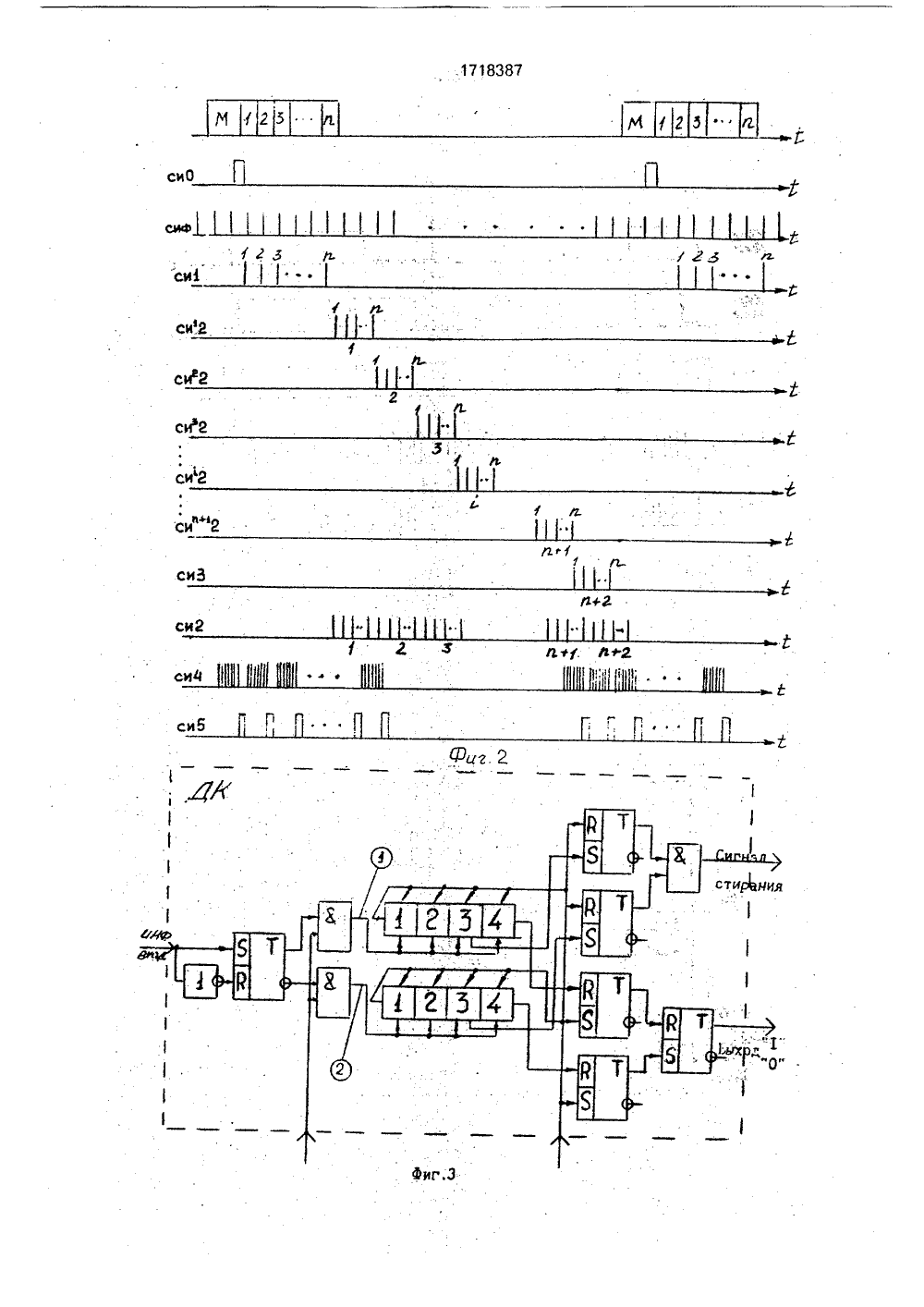

(19 3 М 13/ МИТЕТОТКР ЫТИ ГОСУДАРСТВЕННЫЙПО ИЗОБРЕТЕНИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) Авторское свидетельство СССРМ 1078655, кл. Н 03 М 13/02, 1982;(54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯМНОГОКРАТНЫХ И ИСПРАВЛЕНИЯ ОДИНОЧНЫХ ОШИБОК(57) Изобретение относится к технике электросвязи, может быть использовано в системах передачи данных, контроля иуправления и является усовершенствованием устройства по авт,св, М 1078655. Цель изобретения - повышение помехоустойчивости за счет обеспечения возможности исправления многократных ошибок, Устройство содержит формирователь 1 синхроимпульсов, накопители 2 и 12, датчик 3 одиночных ошибок, ключ 4, блок 5 обнаружения ошибок, элементы ИЛИ 6, 7, 8 и 16, элемент НЕ 9, триггер 10, сумматор 11 и 13 по модулю два, детектор 14 качества и элемент 15 запрета, Устройство позволяет наряду с коррекцией одиночных ошибок производить исправление многократных ошибок путем инвертирования ненадежных символов, выявленных детектором качества. 8 ил,1718387 2 Составитель О. МалофейТехред М,Моргентал Редакто ректор М. Демчик огули аказ 891 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при Г 113035, Москва, Ж, Раушская наб,. 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина. 1 Опо авт,св. В 1078655 10 20 25 30 35 40 45 50 55 Изобретение относится к технике электросвязи, может использоваться в системах передачи данных, контроля и управления и является усовершенствованием устройства Известно устройство для исправления одиночных и обнаружения многократных ошибок, содержащее сумматор по модулю два, накопитель, датчик одиночных ошибок,ключ, блок обнаружения ошибок, первый, второй и третий элементы ИЛИ, элемент НЕ, триггер, установочный вход, который через первый элемент ИЛИ подключен на вход триггера, другой вход которого через элемент НЕ соединен с управляющим выходом блока обнаружения ошибок, с вторым входом первого элемента ИЛИ, с первым входом ключа и через датчик одиночных ошибок с входом сумматора по модулю два,другой вход которого соединен с выходом накопителя, первый вход которого соединен с триггером, а второй вход накопителя через второй элемент ИЛИ соединен с выходом ключа, второй вход которого соединен с выходом сумматора по модулю два и первым входом третьего элемента ИЛИ, выход которого подключен к входу блока обнаружения ошибок, по второму выходу которого формируется сигнал "Ошибка", а второй вход второго элемента ИЛИ одновременно соединен с вторым входом третьего элемента ИЛИ и является входом устройства, выходом которого является второй выход накопителя.Недостатком известного устройства для исправления одиночных и обнаружения многократных ошибок является недостаточная помехоустойчивость при воздействии на канал связи нестационарных помех.Цель изобретения - повышение помехоустойчивости устройства за счет возможности исправления многократных ошибок,Поставленная цель достигается тем, что в устройство для обнаружения многократных и исправления одиночных ошибок введены формирователь синхроимпульсов, вторые накопитель и сумматор по модулю два, между входом устройства и информационным входом первого элемента ИЛИ включен детектор качества, между выходом первого сумматора по модул;о два и вторым входом второго элемента ИЛИ введены четвертый элемент ИЛИ и элемент ЗАПРЕТ, выход которого подключен к первому входу четвертого элемента ИЛИ, первый вход второго сумматора по модулю два объединен с информационным входом первого элемента ИЛИ и подключен к первому выходу детектора качества, второй выход которого подключен к второму входу второго сумматорапо модулю два, выход которого подключен кпервому входу второго накопителя, выходкоторого подключен к второму входу четвертого элемента ИЛИ, первый вход формирователя синхроимпульсов объединен свторыми входами блока обнаружения ошибок, второго накопителя и датчика одиночных ошибок и подключен к установочномувходу устройства, второй и третий входыформирователя синхроимпульсов подключены соответственно к тактовому входу устройства и выходу блока обнаруженияошибок, третий вход которого объединен содноименными входами, первого и второгонакопителей и подключен к первому выходуформирователя синхроимпульсов, второйвыход которого подключен к четвертым входам первого накопителя и блока обнаружения ошибок и третьему входу датчикаодиночных ошибок, третий выход формирователя синхроимпульсов подключен к четвертому входу второго накопителя иинверсному входу элемента ЗАПРЕТ, четвертый, пятый и шестой выходы формирователя синхроимпульсов подключенысоответственно к первому и второму входамдетектора качества и пятому входу блокаобнаружения ошибок.Введение формирователя синхроимпульсов и соответствующих ему связей позволяет оЬеспечить нормальноефункционирование всех элементов устрой- .ства.Введение детектора качества, второгосумматора по модулю два соответствующихим связей создают возможность одновременно с приемом символов сообщения изканала связи сформировать скорректированную кодовую комбинацию, в которой инвертированы все ненадежные элементысообщения, отмеченные детектором качества.Введение второго накопителя и соответствующих ему связей позволяет записать, сохранить и выдать в нужный моментскорректированную кодовую комбинацию,Введение четвертого элемента ИЛИ исоответствующих ему связей обеспечит возможность подачи-скорректированной кодовой комбинации, через третий элементИЛИ, вблок обнаружения ошибок и подачина информационный вход ключа.Введение элемента запрета и соответствующих ему связей позволяет обеспечитьподачу кодовых комбинаций из первого накопителя в блок обнаружения ошибок и наинформационный вход ключа, а также запрета подачи такой информации в случаевыдачи вторымнакопителем скорректированной кодовой комбинации, 171838710 15 20 25 30 35 40 45 50 55 На фиг. 1 представлена схема предлагаемого устройства; на фиг. 2 - временные диаграммы работы формирователя синхроимпульсов; на фиг, 3 и 4 - временные диаграммы работы детектора качества и возможный вариант схемы; на фиг. 5- накопитель; на фиг. 6 - блок обнаружения ошибок; на фиг. 7 - датчик одиночных ошибок; на фиг. 8 - формирователь синхроимпульсов.Устройство обнаружения многократных и исправления одиночных ошибок содержит формирователь 1 синхроимпульсов, накопитель 2 и 12, датчик 3 одиночных ошибок, ключ 4, блок 5 обнаружения ошибок, элементы ИЛИ 6-8 и 16, элемент НЕ 9; триггер 10, сумматор 11 и 13 по модулю два, детектор 14 качества и элемент 15 запрета,Первый вход формирователя 1 сйнхроимпульсов является тактовым входом устройства, установочный вход которого соединен одновременно с вторым входом формирователя 1 синхроимпульсов, с первым входом элемента ИЛИ 6, с установоч. ным входом датчика 3 одиночных ошибок, с установочным входом блока 5 обнаружения ошибок, с установочным входом накопителя 12, первый вход которого соединен с.выходом сумматора 11 по модулю два, первый вход которого соединен с первым выходом детектора 14 качества, второй выход. которого одновременно подключен к второму входу сумматора 11 по модулю два, к.второму входу элемента ИЛИ 7, к первому входу элемента ИЛИ 8, второй вход которого.соединен с информационным входом ключа 4 и выходом элемента ИЛИ 16, первый вход которого соединен с выходом накопителя 12, третий вход которого соединен с третьйм входом накопителя 2. первым входом блока 5 обнаружения ошибок и первым управляющим выходом формирователя 1 синхроимпульсов, второй вход которого подключен к четвертому входу накопителя 2, к второму входу датчика 3 одиночных ошибок и к второму входу блока 5 обнаружения ошибок, информационный вход которого соединен. с выходом элемента ИЛИ 8; а выход одновременно подключен к управляющим входам ключа 4 формирователя 1 синхроимпульсов, через последовательно соединенные элементы ИЛИ 6 и триггер 10 к первому входу накопителя 2, через элемент НЕ 9 к второму входу триггера 10, к первому входу датчика 3 одиночных ошибок, выход которого подключен к первому входу сумматора 13 по модулю два, второй вход которого соединен . с первым выходом накопителя 2, по второму выходу которого считывается информация получателя, а второй вход накопителя 2 соединен с выходом элемента ИЛИ 7, первый вход которого соединен с выходом ключа 4, причем третий управляющий выход формирователя 1 синхроимпульсов одновременно подключен к второму входу накопителя 12 и к инверсному входу элемента 15 запрета, прямой вход которого соединен с выходом сумматора 13 по модулю два, а выход элемента 15 запрета подключен к второму входу элемента ИЛИ 16, при этом вход детектора 14 качества является информационным входом устройства, а сигнал "Ошибка" выдается по второму выходу блока 5 обнаружения ошибок, кроме того, четвертый выход формирователя 1 синхроимпульсов соединен с первым тактовым входом детектора 14 качества, а его второй тактовый вход подключен к пятому выходу формирователя 1 синхроимпульсов, к шестому выходу которого подсоединен третий вход блока 5 обнаружения ошибок.Формирователь 1 синхроимпульсов (фиг. 8) обеспечивает нормальное функционирование всех элементов устройства, После выделения маркеров цикловой синхронизации, определяющей начало кадра многократно повторенного сообщения, выделяется импульс СИО установки элементов памяти устройства в нулевое состояние(фиг. 2), После чего формирователь 1 синхроимпульсов обеспечивает пакетирование синхроимпульсов в последовательности СИ 1 - СИ 5 из импульсов тактовой синхронизации СИФ. поступающих на его вход. Число импульсов соответствует в пакете количеству символов в сообщении.Формирователь 1 синхроимпульсов состоит из пяти ключей 1 - 2, 1-3, 1-4, 1 - 5, 1-6,двух счетчиков на и (1-7, 1 - 9) и одного на и + 2 1-13 с дополнительным выходом на и+ 1, а также двух умножителей на 7 (1 - 11) и на ги (1 - 8), интегратора 1-12 с элементом задержки на пол такта (1 - 10) и инвертора 1 - 1 Умножитель на 1-11 выбран с учетом того, что при реализации детектора качества количество точек регистрации элементарных посылок равно 7, Число ги в умножителе 1 - 8 выбирается в зависимости от интенсивности поступления кодограмм в устройство для обнаружения многократных и исправления одиночных ошибок. От генератора тактовых импульсов поступают импульсы СИФ на вход ключа 1-6 и с его выхода через ключ 1 - 2 поступают на первый выход формирователя. Последовательность СИФ поступает также на счетчик 1-7, который, отсчитав и импульсов, закрывает ключ 1 - 2, таким образом происходит формирование пачки из и импульсов с частотой СИФ, формирование последовательности СИ 5 происходит следу 1718387ющим образом; импульсы СИ 1 задерживаются на пол такта элементом 1-10 и расширяются по фронту интегратором 1-12. Импульсы СИ 1 умножаются на 7 в блоке 1-11 и получается последовательность СИ 4. В случае, если блок обнаружения ошибок 5 обнаружит ошибку, т.е. выдаст нулевой сигнал, а инвертор 1 - 1 его инвертирует и подает единицу на счетчик 1 - 13, который разрешает прохождение импульсов СИФ (фиг, 2) через второй ключ 1-3 на вход умно- жителя на гл 1 - 8. Затем эта последовательность импульсов отсчитывается вторым счетчиком на и 1 - 9 и проходит через третий ключ 1-4 на второй выход формирователя. Если при очередной проверке кодограммы блок 5 обнаружения ошибок вновь обнаружит ошибку, то с второго выхода формирователя 1 снимается такая же последовательность импульсов, Так происходит в течение и+ 2 тактов проверки скорректированной комбинации, При этом второй счетчик на и 1 - 9 отсчитав и импульсов устанавливается в исходное состояние и запускается сигналом обнаружения ошибки с выхода блока Б обнаружения ошибок. Так формируется последовательность импульсов СИ 2, В тот момент, когда счетчик на и + 2 (1 - 13) отсчитает и + 1 такт проверки верности комбинации открывается. четвертый ключ 1 - 5 и выводит последний и + 2-й пакет из импульсов СИ 2 на третий выход формирователя, т.е. сформирована последовательность импульсов СИЗ (фиг. 2). Счетчик на и2 (1 - 4), отсчитав и + 2-й такт проверки верности комбинации, подастсигнал на блок 5 обнаружения ошибки, где формируется сигнал "Ошибка". Если блок не обнаружит ошибки, т.е, с его выхода поступит единичный сигнал, который, поступив на управляющий вход пятого ключа 1 - 6 формирователя синхроимпульсов, прекращает подачу на его выходы последовательности синхроимпульсов,Накопители 2 и 12 (фиг. 5) служат для записи, хранения и выдачи информации, Они являются типичными элементами памяти и могут быть выполнены на регистрах сдвига, Накопитель состоит из элементов памяти (триггеров), количество которых соответствует количеству элементарных посылок в кодограмме, на один больше этого количества элементов И, двух инверторов и элемента ИЛИ, на входы которого поступают последовательности импульсов СИ 1 и СИ 2, а также управляющий сигнал с выхода триггера 10, который является одновременно разрешающим сигналом для параллельного считывания информации. С выхода элемента ИЛИ 7 информация записывается20 25 30 35 40 45 50 считывает "число голосов" за единичную 55 5 10 поочередно в ячейки памяти, Последовательное считывание информации производится с выхода и + 1-го элемента И при отсутствии управляющего сигнала с выхода триггера 10.Датчик 3 (фиг. 7) одиночных ошибок,служит для выдачи единичного вектора ошибок. Причем при очередной выдаче комбинации из накопителя 2 датчик 3 одиночных ошибок восстанавливает искаженный в предыдущей проверке разряд и инвертирует следующим разряд комбинации, так как наложение вектора ошибки начинается не с первого разряда, а с второго вектор ошибки накладывается на первый разряд комбинации, Примерная схема такого устройствапредставлена на фиг. 7.Датчик одиночных ошибок состоит издвоичного счетчика на и, дешифратора, инвертора и регистрас параллельной записью и последовательным считыванием, В исходное состояние датчик устанавливается импульсом СИО, поступающим на установочный вход, Двоичный счетчик, получив с выхода блока 5 обнаружения ошибки нулевой сигнал обнаруженной ошибки и инвертировав его, сосчитывает его в двоичном коде на свои выходы. Дешифратор в зависимости от значения количества обнаруженных ошибок блоком 5 обнаружения ошибок формирует единичный сигнал на одном из своих выходов. Далее регистр считывает единичный вектор с выходов дешифратора и происходит последовательное считывание такого вектора на первый вход первого сумматора 13 по модулю два Детектор 14 (фиг. 3) качества оценивает качество принимаемых посылок. Посылки низкого качества, т.е. ненадежные, отмечают сигналом стирания. Детектор качества состоит из шести триггеров, инвертора, трех элементов И и двух счетчиков, Элементарная посылка поступает через первый триггер, который направляет единичные элементарные посылки на первый элемент И, а нулевые посылки - на второй, Последовательностью импульсов СИ 4 стробируются элементарные посылки принимаемой кодограммы. Таким образом первый счетчик подпосылку, а второй счетчик - за нулевую посылку. По большинству голосов принимается решение о соответствии принятой элементарной посылки единичному или нулевому сигналу. Эта информация снимается с второго выхода детектора качеств (выход триггера). В случае, если элементарная посылка приходит низкого качества, т.е. раздробленной, то "количество голосов" в счетчиках не меньше трех, таким образом5 10 15 20 25 30 35 40 50 55 сформируется сигнал стирания, свидетельствующий о ненадежности элементарной посылки в кодограмме и поступающей на первый выход детектора качества.Блок 5 обнаружения ошибок(фиг, б)служит для установления соответствия .принимаемой комбинации разрешенной кодовой .комбинации, т,е. определения наличия одиночных и многократных ошибок и выдачи сигнала об этом, В нее входят два сумматора по модулю два, ячейки памяти по количеству элементарных посылок в кодограмме, элемент ИЛИ и ключ, а также инвертор, второй элемент ИЛИ, осуществляющий синхронизацию работы блока последователь. ностью импульсов СИ 1 или СИ 2, Кроме того, в схему блока входит элемент И, который формирует сигнал "Ошибка", если в течение и+ 2 проверок отождествления комбинации с разрешенной кодовой не происходит, т.е, при обнаружении ошибки в комбинации в одном такте проверка с выхода блока поступает нулевой сигнал и, наоборот, при обна; ружении ошибки - единичный сигнал.Устройство работает следующим образом,Исходное состояние элементов памяти устройства нулевое. что обеспечивается установочным синхроимпульсом СИО (фиг, 2), выделенным по приему маркера цикловой кадровой синхронизации, Символы сообщения из канала связи поступают на детектор 14 качества, который отождествляет сигнал с "0" или "1". С первого выхода детектора 14 качества выдается информация о ненадежных элементах принятой комбинации на первый вход сумматора 11 по модулю. два, где происходит сложение ее с информационными символами. Скорректированная комбинация записывается на накопитель 12, на третий вход которого подается управляющий сигнал СИ 1, открывающий его на время записи скорректированных элементов первого цикла, Информационные символы через элементы ИЛИ 7 и 8 вводятся соответственно в накопитель 2, на третий вход которого подается управляющий сиг-. нал СИ 1, открывающий его на время записи и в блок 5 обнаружения ошибок, на второй вход которого также подается управляющий сигнал СИ.1, обеспечивающий синхронную работу данного устройства на время обработки принятой кодовой комбинации (фиг, 2). Во время заполнения накопителя 2 блок 5 обнаружения ошибок анализирует принятую комбинацию.При необнаружении ошибки на выходе блока 5 обнаружения ошибок появляется единичный сигнал, который поступает на управляющий вход формирователя 1 синхроимпульсов, при этом прекращается подача синхроимпульсов на все выходы формирователя 1 синхроимпульсов, этот единичный сигнал также через элемент ИЛИ 6 поступает на счетный вход триггера 10, который выдает разрешающий импульс для снятия комбинации из накопителя 2 получателем и он устанавливается в нулевое состояние,Если в первом цикле проверки блок 5 обнаруживает ошибку, то на его выходе обнаружения ошибок образуется нулевой сигнал, который инвертируется элементом НЕ 9. Единичный сигнал, поступая с выхода элемента НЕ 9 на нулевой вход триггера 10, устанавливает последний в нулевое состояние, Далее комбинация выдается на проверку второй раз, но уже из накопителя 2 на сумматор 13 по модулю два, где на информационные символы накладывается вектор ошибки, формируемый датчиком 3 одиночных ошибок, только при поступлении его на второй вход нулевого сигнала обнаружения ошибки из блока 5 обнаружения ошибок, и результат с выхода сумматора 13 по модулю два через элемент 15 запрета, элемент ИЛИ 16 и элемент ИЛИ 8 поступает в блок 5 обнаружения ошибок, При обнаружении ошибки на выходе блока 5 обнаружения ошибок вновь появляется нулевой сигнал, инвертируемый элементом НЕ 9. Триггер 10 остается в нулевом состоянии и комбинация из накопителя 2, считываемая управляющим сигналом СИ 2, выдается второй раз с наложением очередного вектора одиночной ошибки и анализом в блоке 5 обнаружения ошибок. Процесс формирования различных векторов одиночных ошибок происходит до первого необнаружения ошибки, но не более и раз, если в течение (и + 1) проверок отождествления комбинации с кодовой не происходит, скорректированная кодовая комбинаций считывается с накопителя 12 управляющим сигналом СИЗ. выдаваемом с. третьего выхода формирователя 1 синхроимпульсов, через элемент ИЛИ 16 на информационный вход ключа 4, с выхода которого информация вводится через элемент ИЛИ 7 в накопитель 2 и одновременно через элемент ИЛИ 8 в блок 5 обнаружения ошибок, Вместе с тем, управляющий сигнал СИЗ поступает на инверсный вход элемента 15 запрета, тем самым предохраняя поступление информации с сумматора 13 по модулю два на элемент ИЛИ 16 и далее в блок обнаружения ошибок.Если при проверке ошибка в анализируемой комбинации не обнаруживается, то блок 5 обнаружения ошибок выдает единичный сигнал на ключ 4, формирователь 1 синхроимпульсов и датчик 3 одиночных ошибокнепосредственно, а на счетный вход триггера 10 - через элемент ИЛИ 6. При этом формирователь 1 синхроимпульсов прекращает подачу синхроимпульсов на свои выходы, ключ 4 отключается, триггер 10 переходит в единичное состояние, а датчик 3 одиночных ошибок выдает вектор ошибки, аналогичный предыдущему (в данном случае - нулевой). После выдачи триггером 10 единичного сигнала, происходит снятие исправленной комбинации из накопителя 2 получателем.Таким образом, предлагаемое устройство обладает более высокой технико-экономической эффективностью, чем известное; так как при исправлении одиночных ошибок путем инвертирования. единичных элементов создается возможйость исправления многократных ошибок, благодаря тому, что в устройстве учитывается сигнал о ненадежности принимаемых символов при действии в канале связи нестационарных помех, Следовательно, повышается помехоустойчивость всего устройства в целом. Формула изобр.етения Устройство для обнаружения многократных и исправления одиночных ошибок по авт,св. М 1078655, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости устройства путем обеспечения возможности исправления многократных ошибок, в него введены формирователь синхроимпульсов, вторые накопитель и сумматор,по модулю два, между входом устройства и информационным входом первого элемента ИЛИ включен детектор качества., между выходом первого сумматора по модулю два и вторым входом второго элемента ИЛИ введены четвертый элемент ИЛИ и элемент ЗАПРЕТ. выход которого подключен к первому входу четвертого эле мента ИЛИ, первый выход второго сумматора по модулю два обьединен с информационным входом первого элемента ИЛИ и подключен к первому выходу детектора качества, второй выход которого под ключен к второму входу второго сумматорапо модулю два, выход которого подключен к первому входу второго накопителя, выход которого подключен к второму входу четвертого элемента ИЛИ, первый вход формиро вателя синхроимпульсов объединен свторыми входами блока обнаружения ошибок, второго накопителя и датчика одиночных ошибок и подключен к установочному входу устройства, второй и третий входы 20 формирователя синхроимпульсов подключены соответственно к тактовому входу устройства и выходу блока-обнаружения ошибок, третий вход которого обьединен с одноименными входами первого и второго.25 накопителей и подключен к первому выходуформирователя синхроимпульсов, второй выход которого подключен к четвертым входам первого накопителя и блока обнаружения ошибок и третьему входу датчика 30 одиночных ошибок, третий выход формирователя синхроимпульсов подключен к четвертому входу второго накопителя и инверсному входу элемента ЗАПРЕТ, четвертый, пятый и шестой выходы формирова теля синхроимпульсов подключенысоответственно к первому и второму входам детектора качества и пятому входу блока обнаружения ошибок.

СмотретьЗаявка

4820146, 16.03.1990

СТАВРОПОЛЬСКОЕ ВЫСШЕЕ ВОЕННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ СВЯЗИ ИМ. 60-ЛЕТИЯ ВЕЛИКОГО ОКТЯБРЯ, ПРЕДПРИЯТИЕ ПЯ Г-4651

МАЛОФЕЙ ОЛЕГ ПАВЛОВИЧ, КВЕЛАШВИЛИ ТИМУР ГЕОРГИЕВИЧ, КОВАЛЕНКО АЛЕКСАНДР ПАВЛОВИЧ, АШАНИН ВЛАДИМИР СЕМЕНОВИЧ, САПОЖНИКОВ АЛЕКСАНДР ДМИТРИЕВИЧ

МПК / Метки

МПК: H03M 13/02

Метки: исправления, многократных, обнаружения, одиночных, ошибок

Опубликовано: 07.03.1992

Код ссылки

<a href="https://patents.su/10-1718387-ustrojjstvo-dlya-obnaruzheniya-mnogokratnykh-i-ispravleniya-odinochnykh-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения многократных и исправления одиночных ошибок</a>

Предыдущий патент: Декодирующее устройство линейного циклического кода

Следующий патент: Способ кодирования и передачи информации

Случайный патент: Устройство для контроля работы фрикционного тормоза