Устройство для исправления ошибок в информации, закодированной циклическим кодом

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 512589

Авторы: Номоконов, Соболевский, Толстяков, Яковлев

Текст

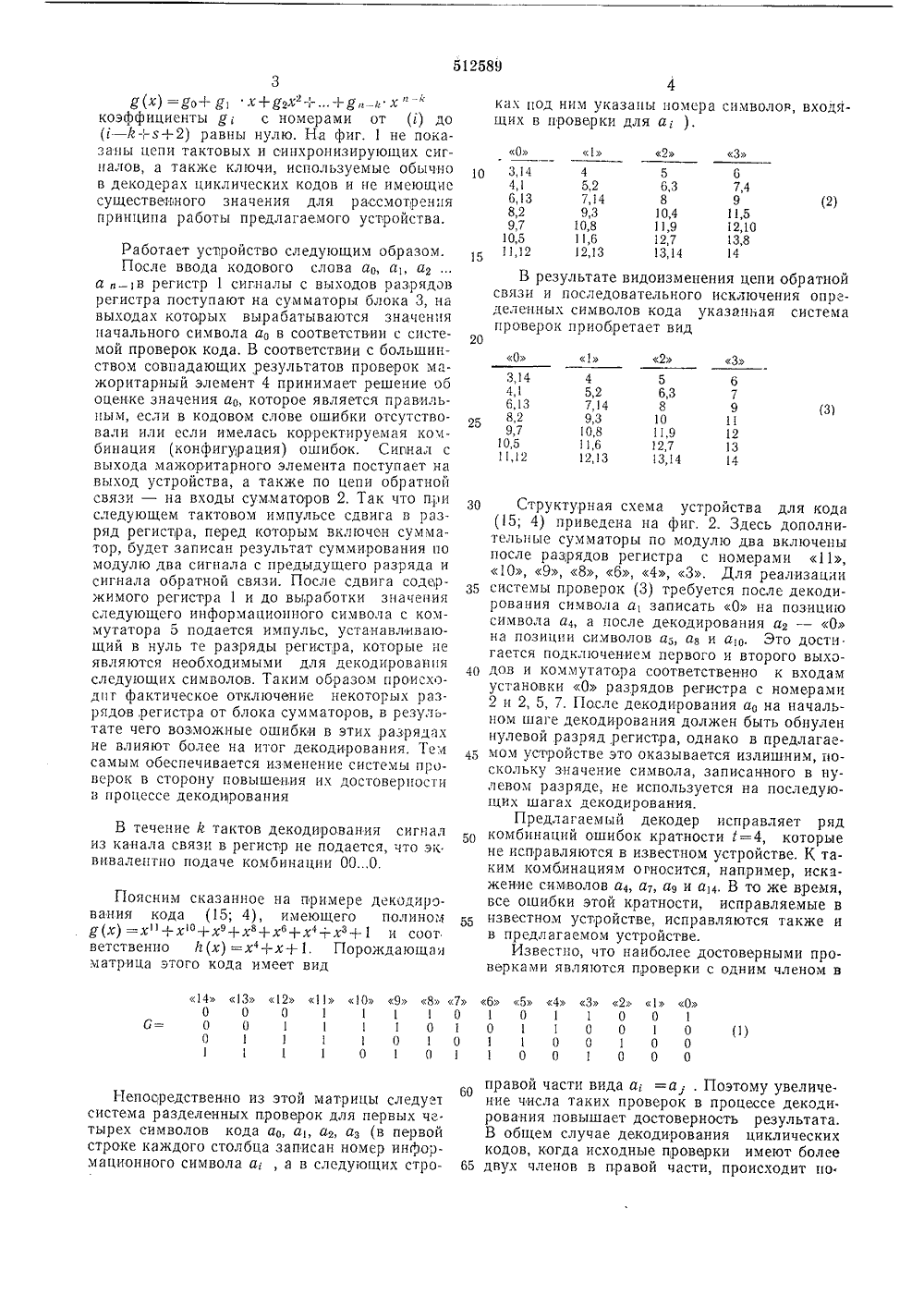

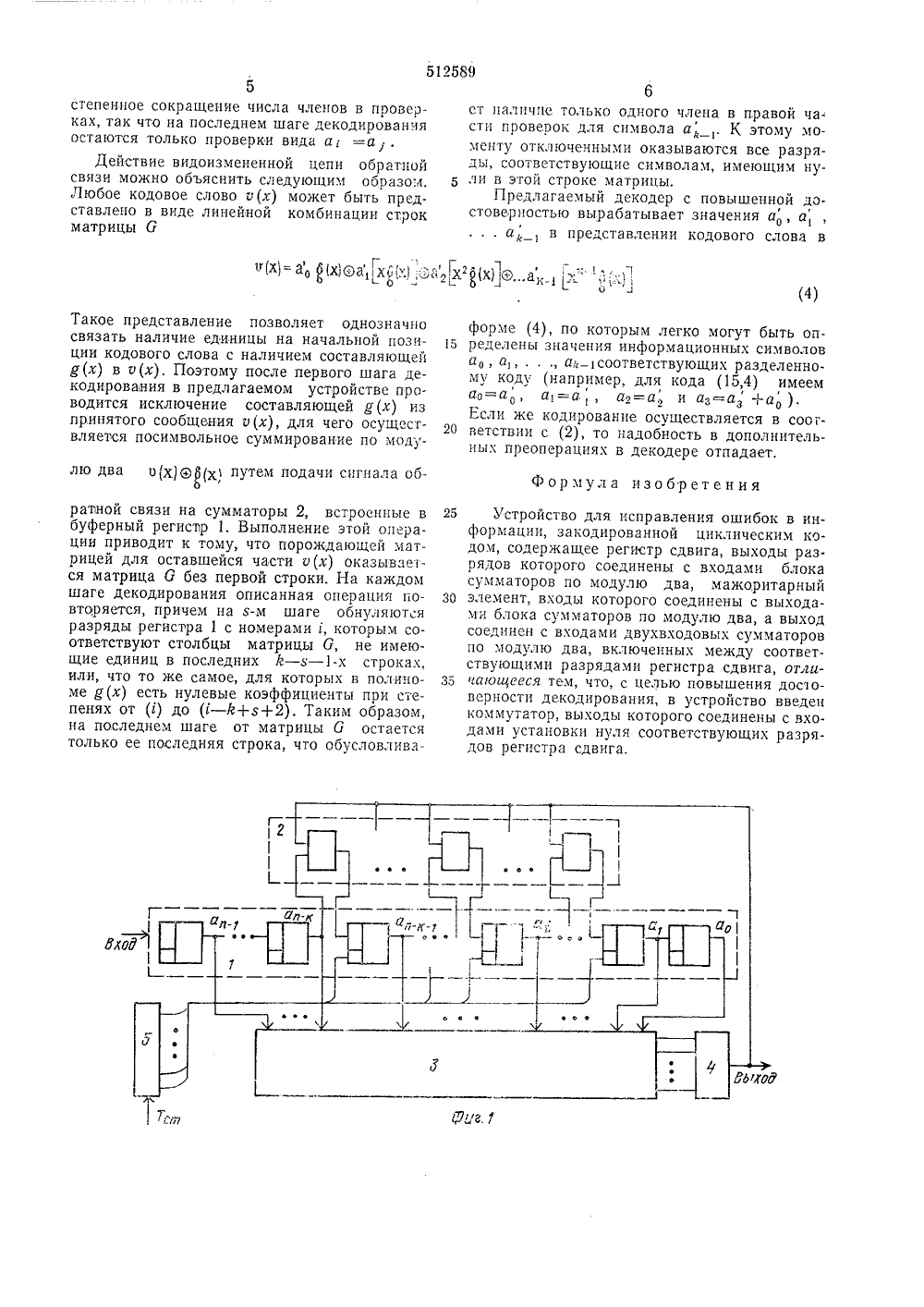

ОЛИСАНИЕИЗОБРЕТЕН ИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветакикСоциалистическихРеспублик 11 512589 олнитсльное к авт. си 1 д-ву 1) М Ка 2 Н 04 Ь 1/10 6 06 Г/О22) Заявлено 04.04.7 21) 2011917/18-24 с присоединением заявки-осударствеиныи комите 1Совета Министров СССРаа делам изобретенийи открытий(23 орнтет убликовано 30.04.7 та опубликования юллетень(088.8) 1 сання 27.01 2) Авторы изобретсшгя В. С, Толстяков, В. Н. Номоконов Соболевский овлев Ленинградский ордена Ленина имени В, И. Улья1 Заявител ектротехнический институва (Ленина)(54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В ИНФОРМАЦИИ, ЗАКОДИРОВАННОЙ ЦИКЛИЧЕСК КОДОМга.ОДНЯКОисправляещей кратношибок, онедостаточдированиясвязано сосуществлверок. устройстве доля реально ок кратности, превышаютированно исправляемых о невелика, что дела т тность правильного декоях сильных помех. Это сь процесс декодирования неизменной системе пров таком 1 ых ошиб ость гаран тносительн нои верояв услови тем, что ве яется при Цель изобретения ности устройства для рования циклических увеличении доли испр- повышение эффекгивмажоритарного декоднкодов, выражающееся в вляемых ошибок и в со 1Изобретение относится к области обраоотки сложных сигналов, в частности к реализации помехоустойчивого кодирования, и может быть использовано в системах передачи цифровой информации.Известно устройство для исправления ошибок в информации, закодированнон ш;клнчсским кодом, содержащее регистр сдвига, выходы разрядов которого подключены к входам блока сумматоров по модулю два, межоритарный элемент, входы которого соединены с выходами блока сумматоров по модул;о два, а выход - с входами двухвходовых сумматоров по модулю два, включенных между соответствующими разрядами регистра сдвиответствующем повышсн 1 ш вероятности правильного декодирования,;-.1 то достнегается тем, что в устройство введен коммутатор, выходы которого соединены с5 входамн установки нуля соответствующихразрядов регистра сдвига.Та фиГ. 1 пзооражен 2 ст 1 уктурная схемаустройства для нсправле 1 п 1 я ошибок в инфорз 12 ц "1 н, закодированной цн 1"лнческнм кодох 1,1 О на фиГ, 2 - схез 12 устройства для кода(15; 4),Устройство содержит гг-разрядный сдвнга 10 щнп реГ 11 стр 1, между разрядаъ 1 н которОГОимеются дополнительно встроенные двухвходовые сумматоры 2 по модулю два, олок 3сумматоров по модулю два, мажоритарныйэлемент 4 н коммутатор 5 с к - 1 выходамн.Выходы разрядов регистрасоединены с входами блока 3 сумматоров по модулю два, которьш строится в соответствии с системой проверок кода. Выходь 1 олока сумматоров подкл 10 чсн 1 ь 1 к входам мажоритарного элез 1 ента 4,выход которого соединяется с вторыми входамн встроенных сумматоров 2. Вход коммутатора 5 связан с шиной Тначала декодирования, а его выходы - с входамп установкинуля определенных разрядов регистра так, чтоэ-й выход коммутатора подключен к входуЛ разрядов с номерами 1, для которых в поЗО рождающем пол 1 шоме1 00 11 00 00 0 60 65 3Я(х) =ИО+ Д 1+Я 2 х -1-+Да - / х коэффициенты д; с номерами отдо ( - г+з+2) равны нулю. На фиг. 1 не показаны цепи тактовых и синхронизирующих сигналов, а также ключи, используемые обычно в декодерах циклических кодов и не имеющие существенного значения для рассмотрения принципа работы предлагаемого устройства. Работает устройство следующим образом.После ввода кодового слова ао, а а 2ав регистр 1 сигналы с выходов разрядов регистра поступают на сумматоры блока 3, на выходах которых вырабатываются значения начального символа ао в соответствии с системой проверок кода. В соответствии с большинством совпадающих результатов проверок мажоритарный элемент 4 принимает решение об оценке значения ао, которое является правильным, если в кодовом слове ошибки отсутствовали или если имелась корректируемая комбинация (конфигурация) ошибок. Сигнал с выхода мажоритарного элемента поступает на выход устройства, а также по цепи обратной связи - на входы сумматоров 2. Так что при следующем тактовом импульсе сдвига в разряд регистра, перед которым включен сумматор, будет записан результат суммирования по модулю два сигнала с предыдущего разряда и сигнала обратной связи. После сдвига содержимого регистра 1 и до выработки значения следующего информационного символа с коммутатора 5 подается импульс, устанавливающий в нуль те разряды регистра, которые не являются необходимыми для декодирования следующих символов. Таким образом происходит фактическое отключение некоторых разрядов, регистра от блока сумматоров, в резултате чего возможные ошибки в этих разрядах не влияют более на итог декодирования. Тем самым обеспечивается изменение системы проверок в сторону повышения их достоверности в процессе декодирования В течение й тактов декодирования сигнал из канала связи в регистр не подается, что эк вивалентпо подаче комбинации 000. Поясним сказанное на примере декодиро. вания кода (15; 4), имеющего полином д(х) =х" +хо+х +х+х+х+х+1 и соот ветственно й(х) =х 4+х+1, Порождающая матрица этого кода имеет вид 14 13 12 11 100 0 0 1 10 0 1 1 10 1111 1 0 Непосредственно из этой матрицы следует система разделенных проверок для первых четырех символов кода ао, а, а, а, (в первой строке каждого столбца записан номер информационного символа а а в следующих строках под ним указаны номера символов, входящих в проверки для а; ). В результате видоизменения цепи обратной связи и последовательного исключения определенных символов кода указанная система проверок приобретает вид 30 35 40 45 50 55 Структурная схема устройства для кода (15; 4) приведена на фиг, 2. Здесь дополнительные сумматоры по модулю два включены после разрядов регистра с номерами 11, 10, 9, 8, 6, 4, 3. Для реализации системы проверок (3) требуется после декодирования символа а, записать О на позицию символа а 4, а после декодирования а 2 - О на позиции символов аь а, и а,о. Это дости гается подк;почением первого и второго выходов и коммутатора соответственно к входам установки О разрядов регистра с номерами 2 и 2, 5, 7. После декодирования а, на начальном шаге декодирования должен быть обнулен нулевой разряд регистра, однако в предлагаемом устройстве это оказывается излишним, поскольку значение символа, записанного в нулевом разряде, не используется на последующих шагах декодирования.Предлагаемый декодер исправляет ряд комбинаций ошибок кратности 1=4, которые не исправляются в известном устройстве. К таким комбинациям относится, например, искажение символов а 4, а 7, а 9 и а,4. В то же время, все ошибки этой кратности, исправляемые в известном устройстве, исправляются также и в предлагаемом устройстве.Известно, что наиболее достоверными проверками являются проверки с одним членом в правой части вида а, =а, . Поэтому увеличе. ние числа таких проверок в процессе декоди. рования повышает достоверность результата. В общем случае декодирования циклических кодов, когда исходные проверки имеют более двух членов в правой части, происходит но.(4) степенное сокращение числа членов в проверках, так что на последнем шаге декодирования остаются только проверки вида а; =а 1Действие видоизмененной цепи обратной связи можно объяснить следующим образом, Любое кодовое слово о(х) может быть представлено в виде линейной комбинации строк матрицы 6 Такое представление позволяет однозначно связать наличие единицы на начальной позиции кодового слова с наличием составляющей д(х) в о(х). Поэтому после первого шага декодирования в предлагаемом устройстве проводится исключение составляющей д(х) из принятого сообщения о(х), для чего осуществляется посимвольное суммирование по модулю два и,х)О(х путем подачи сигнала ооратной связи на сумматоры 2, встроенные в буферный регистр 1. Выполнение этой операции приводит к тому, что порождающей матрицей для оставшейся части о(х) оказывается матрица 6 без первой строки. На каждом шаге декодирования описанная операция повторяется, причем на з-м шаге обнуляются разряды регистра 1 с номерами г, которым соответствуют столбцы матрицы 6, не имеющие единиц в последних Й - ь - 1-х строках, или, что то же самое, для которых в поличоме д(х) есть нулевые коэффициенты при степенях от (г) до (г - А+в+2). Таким образом, на последнем шаге от матрицы 6 остается только ее последняя строка, что обусловливает наличие только одного члена в правой части проверок для символа а ,. К этому моменту отключенными оказываются все разряды, соответствующие символам, имеющим нули в этой строке матрицы.Предлагаемый декодер с повышенной достоверностью вырабатывает значения а, а,а в представлении кодового слова в форме (4), по которым легко могут быть оп ределены значения информационных символова а, а г соответствующих разделенному коду (например, для кода (15,4) имеем 00= ио, гг=гг , и 2=сг и сгз гг,гио )Если же кодирование осуществляется в соог ветствии с (2), то надобность в дополнительных преоперациях в декодере отпадает. Формула изобретения 25 Устройство для исправления ошибок в информации, закодированной циклическим юдом, содержащее регистр сдвига, выходы разрядов которого соединены с входами блока сумматоров по модулю два, мажоритарный ЗО элемент, входы которого соединены с выходами блока сумматоров по модулю два, а выход соединен с входами двухвходовых сумматоров по модулю два, включенных между соответствующими разрядами регистра сдвига, отяиЗ 5 чаюигееся тем, что, с целью повышения дос 1 оверности декодирования, в устройство введен коммутатор, выходы которого соединены с вхо дами установки нуля соответствующих разрядов регистра сдвига.512589 Фиг. зова едакто Тираж 864Совета Министи открытийскан наб д. 4/5 Подписи в СС ОТ, Загорский филиал аказ 5199цНИИП Составитель В, Крыловахред А, Камышникова Изд,1370 Государственного комитет по делам изобретений 3035, Москва, Ж, Рауш

СмотретьЗаявка

2011917, 04.04.1974

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

ТОЛСТЯКОВ ВЛАДИМИР СЕРГЕЕВИЧ, НОМОКОНОВ ВАДИМ НИКОЛАЕВИЧ, ЯКОВЛЕВ ДМИТРИЙ ОЛЕГОВИЧ, СОБОЛЕВСКИЙ ВЛАДИМИР ИВАНОВИЧ

МПК / Метки

МПК: G06F 11/10, H03M 13/51

Метки: закодированной, информации, исправления, кодом, ошибок, циклическим

Опубликовано: 30.04.1976

Код ссылки

<a href="https://patents.su/4-512589-ustrojjstvo-dlya-ispravleniya-oshibok-v-informacii-zakodirovannojj-ciklicheskim-kodom.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок в информации, закодированной циклическим кодом</a>

Предыдущий патент: Устройство обнаружения пауз в телефонном сигнале

Следующий патент: Способ синхронизации линии связи

Случайный патент: Устройство для контроля отклонений положений объектов от прямолинейности