Табличный сумматор по модулю три с коррекцией ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1010626

Автор: Изосимов

Текст

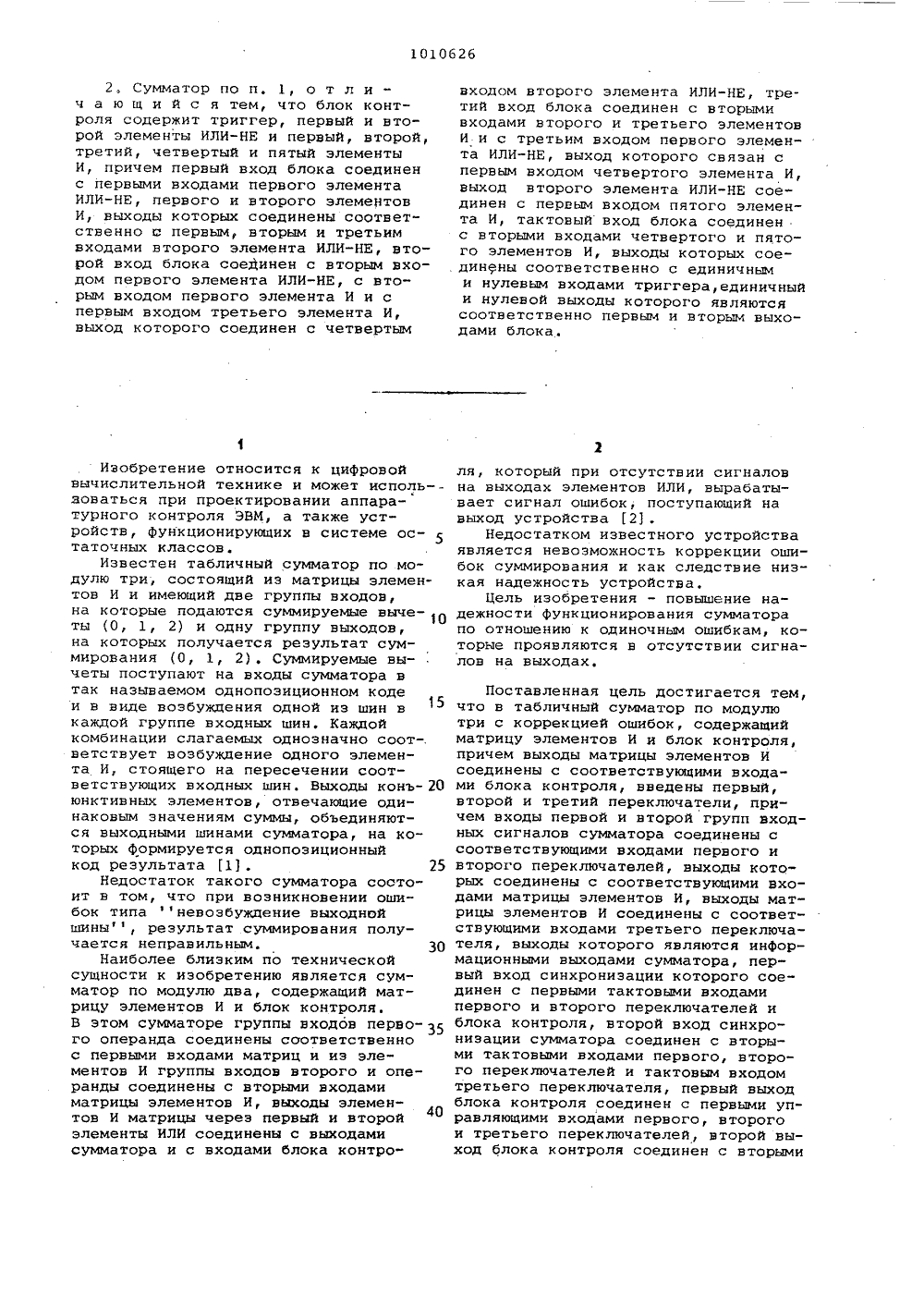

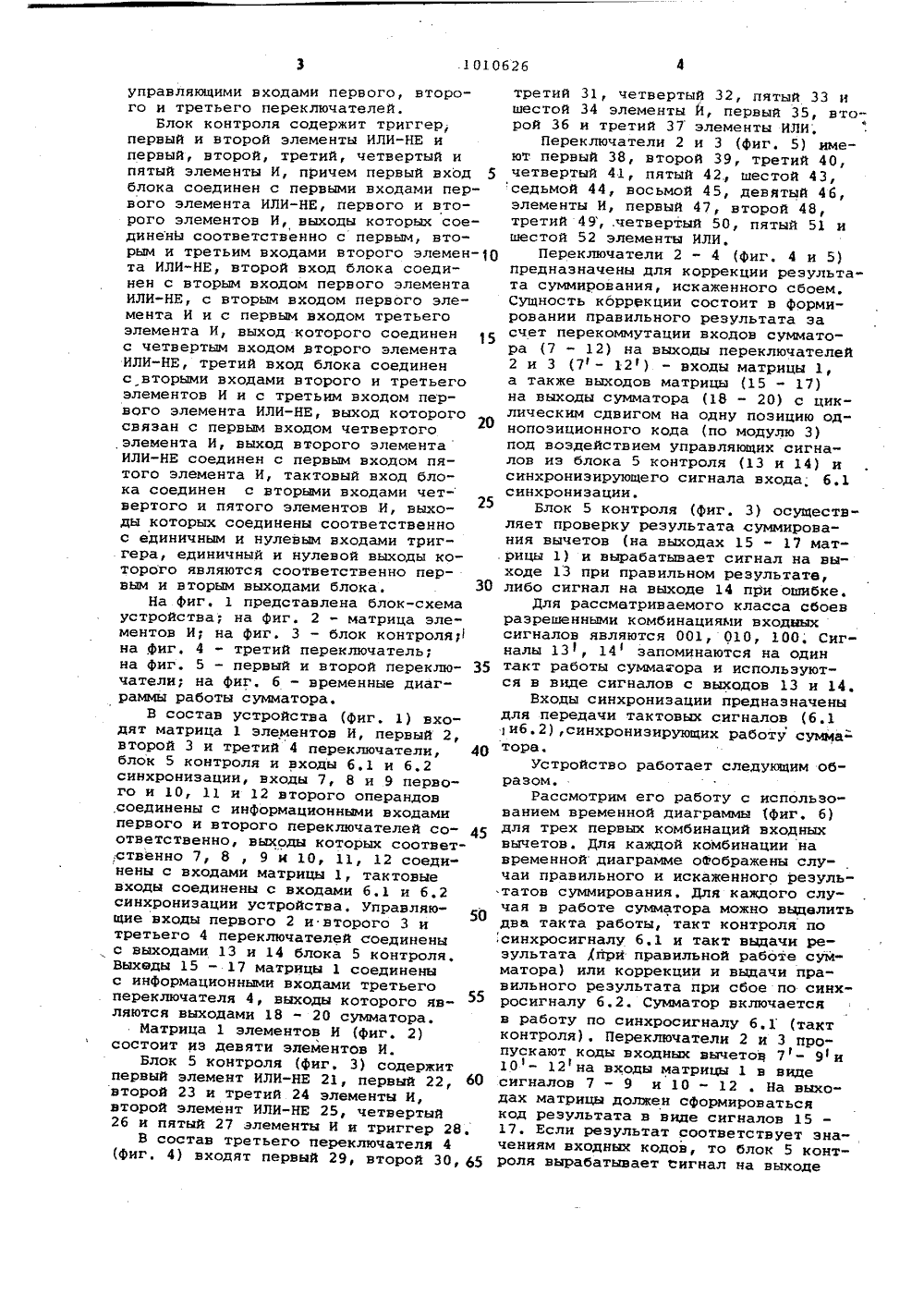

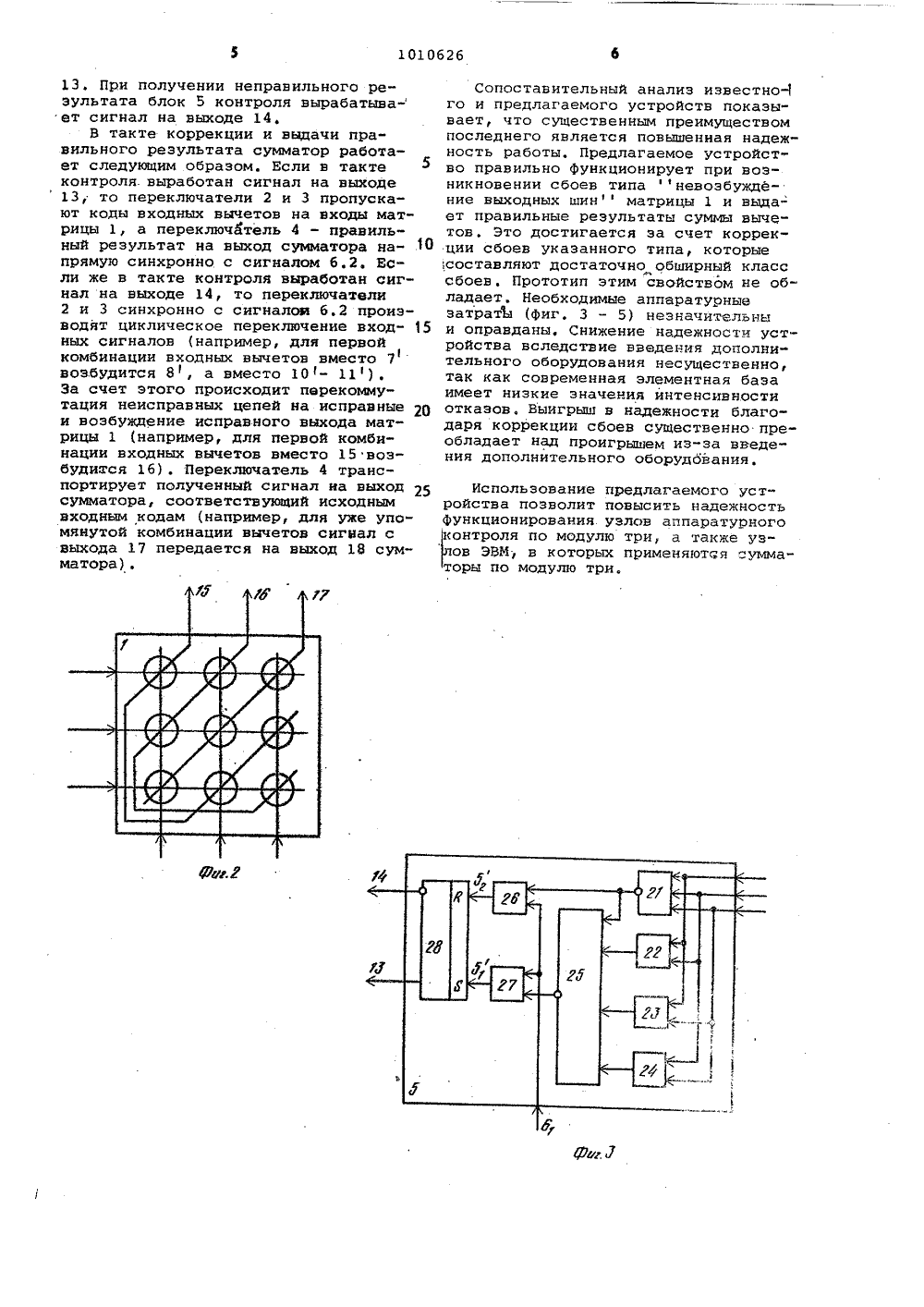

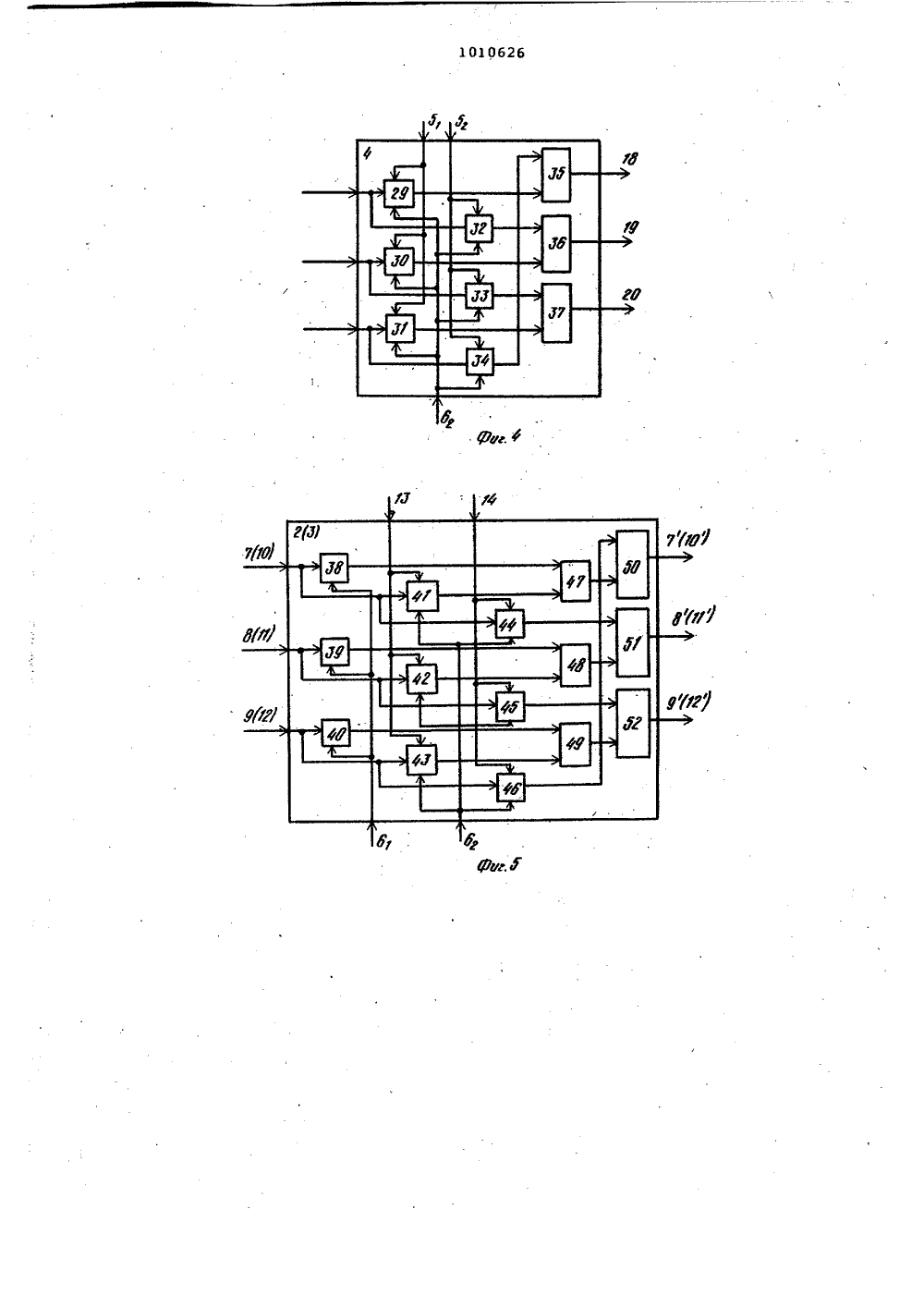

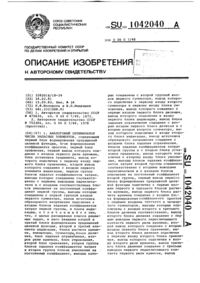

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК ССУД АРС ПО ДЕЛАМ НИ 2(54 вышения н первый, в ли, приче групп вхо ЕННЫЙ КОМИТЕТ ССС ИЗОБРЕТЕНИЙ И ОТКРЫТИ(56). 1. Селлерс Ф. Методы обнаружения оынбок в работе ЭЦВИ. М., фМир, 1972, с.892. Журавлев Ю.П., Котелюк Л.А.,инский Н.И. Надежйасть и конть ВВМ. М., ффСоветское радио 1 ф.,8, с. 116, рис. 3.13 (прототип),) 57) 1. ТАБЛИЧНЫЙ СУММАТОР ПО МОДУЙО ТРИ С КОРРЕКЦИЕЯ ОШИБОК, содержащий матрицу элементов И и блок контроля, причем выходы матрицы элементов И соединенЫ с соответствующими входами блока контроля, о т л ич а ю щ н й с я тем, что, с целью поадежности, в него введеныторой и третий переключатем входы первой и второйдных сигналов сумматора сое 801010626 А динены с аоответствущими входами первого и второго переключателей, вы-, хоцы которых соединены с соответству ецнми входами матрицы элементов И, выходы матрицы элементов И соединены с соответствующими входами третьего переключателя, выходы которого являются ин 4 ормационнйвщ выходами сумматора, первый выход синхронизации которого соединен с первыми тактовыми входами первого и второго переключателей и блока контроля, второй вход синхронизации сумматора соединен с вторыми тактовыми входами первого, второго переключателей и тактовым входом третьего перекзаачатвля, первый выход блока контроля соединен с первыми Дщравлякаимивходами первого, второ и третьего переключате лей, второй выход блока контроля.сое финен с.вторыми управляющими входами первого, второго и третьего .пере:ключателей.1010626 30 2, Сумматор по и. 1, о т л и ч а ю щ и й с я тем, что блок контроля содержит триггер, первый и второй элементы ИЛИ-НЕ и первый, второй, третий, четвертый и пятый элементы И, причем первый вход блока соединен с первыми входами первого элемента ИЛИ-НЕ, первого и второго элементов И, выходы которых соединены соответственно с первым, вторым и третьим входами второго элемента ИЛИ-НЕ, второй вход блока соединен с вторым входом первого элемента ИЛИ-НЕ, с вторым входом первого элемента И и с первым входом третьего элемента И, выход которого соединен с четвертым Изобретение относится к цифровойвычислительной технике и может исполь сзоваться при проектировании аппаратурного контроля ЭВМ, а также устройств, функционирующих в системе остаточных классовИзвестен табличный сумматор по модулю три, состоящий из матрицы элементов И и имеющий две группы входов,на которые подаются суммируемые вычеты (О, 1, 2) и одну группу выходов,на которых получается результат суммирования (О, 1, 2), Суммируемые вычеты поступают на входы сумматора втак называемом однопозиционном кодеи в виде возбуждения одной из шин вкаждой группе входных шин, Каждойкомбинации слагаемых однозначно соот-.ветствует возбуждение одного элемента И, стоящего на пересечении соответствующих входных шин, Выходы коньюнктивных элементов, отвечающие одинаковым значениям суммы, объединяются выходными шинами сумматора, на которых формируется однопозиционныйкод результата 1 . 25Недостаток такого сумматора состоит в том, что при возникновении ошибок типа невозбуждение выходнойшины, результат суммирования получается неправильным,Наиболее близким по техническойсущности к изобретению является сумматор по модулю два, содержащий матрицу элементов И и блок контроля,В этом сумматоре группы входов перво- З 5го операнда соединены соответственнос первыми входами матриц и из элементов И группы входов второго и операнды соединены с вторыми входамиматрицы элементов И, выходы элементов И матрицы через первый и второйэлементы ИЛИ соединены с выходамисумматора и с входами блока контровходом второго элемента ИЛИ-НЕ, третий вход блока соединен с вторымивходами второго и третьего элементовИ и с третьим входом первого элемента ИЛИ-НЕ, выход которого связан спервым входом четвертого элемента И,выход второго элемента ИЛИ-НЕ соединен с первым входом пятого элемента И, тактовый вход блока соединенс вторыми входами четвертого и пятого элементов И, выходы которых соединены соответственно с единичными нулевым входами триггера, единичныйи нулевой выходы которого являютсясоответственно первым и вторым выходами блока. ля, который при отсутствии сигналов на выходах элементов ИЛИ, вырабатывает сигнал ошибок, поступающий на выход устройства 2) .Недостатком известного устройства является невозможность коррекции ошибок суммирования и как следствие низкая надежность устройства,Цель изобретения - повышение надежности функционирования сумматора по отношению к одиночным ошибкам, которые проявляются в отсутствии сигналов на выходах. Поставленная цель достигается тем, что в табличный сумматор по модулю три с коррекцией ошибок, содержащий матрицу элементов И и блок контроля, причем выходы матрицы элементов И соединены с соответствующими входами блока контроля, введены первый, второй и третий переключатели, причем входы первой и второй групп входных сигналов сумматора соединены с соответствующими входами первого и второго переключателей, выходы которых соединены с соответствующими входами матрицы элементов И, выходы матрицы элементов И соединены с соответствующими входами третьего переключателя, выходы которого являются информационными выходами сумматора, первый вход синхронизации которого сое" динен с первыми тактовыми входами первого и второго переключателей и блока контроля, второй вход синхронизации сумматора соединен с вторыми тактовыми входами первого, второго переключателей и тактовым входом третьего переключателя, первый выход блока контроля соединен с первыми управляющими входами первого, второго и третьего переключателей, второй выход блока контроля соединен с вторымиуправляющими входами первого, второго и третьего переключателей.Блок контроля содержит триггер, первый и второй элементы ИЛИ-НЕ и первый, второй, третий, четвертый и пятый элементы И, причем первый вход 5 блока соединен с первыми входами первого элемента ИЛИ-НЕ, первого и второго элементов И, выходы которых сое- диненМ соответственно с первым, вторым и третьим входами второго элемента ИЛИ-НЕ, второй вход блока соединен с вторым входом первого элемента ИЛИ-НЕ, с вторым входом первого элемента И и с первым входом третьего элемента И, выход которого соединен с четвертым входом второго элемента ИЛИ-НЕ, третий вход блока соединен с вторыми входами второго и третьего элементов И и с третьим входом первого элемента ИЛИ-НЕ, выход которого связан с первым входом четвертого элемента И, выход второго элемента ИЛИ-НЕ соединен с первым входом пятого элемента И, тактовый вход блока соединен с вторыми входами чет- вертого и пятого элементов И, выходы которых соединены соответственно с единичным и нулевым входами триггера, единичный и нулевой выходы которого являются соответственно первым и вторым выходами блока. 30На Фиг, 1 представлена блок-схема устройства, на фиг. 2 - матрица элементов И; на фиг, 3 - блок контроля на фиг. 4 - третий переключатель; на фиг. 5 - первый и второй переклю чатели; на Фиг. б - временные диаграммы работы сумматора.В состав устройства (фиг, 1) входят матрица 1 элементов И, первый 2, второй 3 и третий 4 переключатели, 40 блок 5 контроля и входы 6,1 и 6.2 синхронизации, входы 7, 8 и 9 первого и 10, 11 и 12 второго операндов соединены с информационными входами первого и второго переключателей со ответственно, выходы которых соответ,.ственно 7, 8 , 9 и 10, 11, 12 соединены с входами матрицы 1, тактовые входы соединены с входами 6.1 и 6.2 синхронизации устройства. Управляющие входы первого 2 и второго 3 и третьего 4 переключателей соединены , с выходами 13 и 14 блока 5 контроля. Выходы 15 - 17 матрицы 1 соединены с информационными входами третьего переключателя 4, выходы которого являются выходами 18 - 20 сумматора.Матрица 1 элементов И (фиг, 2) состоит из девяти элементов И.Блок 5 контроля (Фиг. 3) содержит первый элемент ИЛИ-НЕ 21, первый 22, 60 второй 23 и третий 24 элементы И, второй элемент ИЛИ-НЕ 25, четвертый26 и пятый 27 элементы И и триггер 28.В состав третьего переключателя 4(фиг, 4) входят первый 29, второй 30, 65 третий 31, четвертый 32, пятый 33 ишестой 34 элементы Й, первый 35, второй 36 и третий 37 элементы ИЛИ,Переключатели 2 и 3 (Фиг. 5) имеют первый 38, второй 39, третий 40,четвертый 41, пятый 42, шестой 43,седьмой 44, восьмой 45, девятый 46,элементы И, первый 47, второй 48,третий 49, .четвертый 50, пятый 51 ишестой 52 элементы ИЛИ,Переключатели 2 " 4 (фиг. 4 и 5)предназначены для коррекции результата суммирования, искаженного сбоем,Сущность коррекции состоит в Формировании правильного результата засчет перекоммутации входов сумматора (7 - 12) на выходы переключателей2 и 3 (7 - 12) - входы матрицы 1,а также выходов матрицы (15 - 17)на выходы сумматора (18 - 20) с циклическим сдвигом на одну позицию од"нопозиционного кода (по модулю 3)под воздействием управляющих сигналов из блока 5 контроля (13 и 14) исинхронизирующего сигнала входа, 6,1синхронизации.Блок 5 контроля (фиг, 3) осуществляет проверку результата суммирования вычетов (на выходах 15 - 17 матрицы 1) и вырабатывает сигнал на выходе 13 при правильном результате,либо сигнал на выходе 14 п 1 и ошибке.Для рассматриваемого класса сбоевразрешенными комбинациями входыыхсигналов являются 001, 010, 100, Сигналы 13 , 14 запоминаются на одинФтакт работы сумматора и используются в виде сигналов с выходов 13 и 14.Входы синхронизации предназначеныдля передачи тактовых сигналов (611 иб.2),синхронизирующих работу сумматора.Устройство работает следующим образом.Рассмотрим его работу с использованием временной диаграммы (Фиг, 6)для трех первых комбинаций входныхвычетов. Для каждой комбинации навременной диаграмме офображены случаи правильного и искаженного результатов суммирования. Для каждого случая в работе сумматора можно выделитьдва такта работы, такт контроля посинхросигналу 6.1 и такт выдачи результата (при правильной работе сумматора) или коррекции и выдачи правильного результата при сбое по синхросигналу 6,2. Сумматор включаетсяв работу по синхросигналу 6.1 (тактконтроля). Переключатели 2 и 3 пропускают коды входных вычетов 7- 9 и10 - 12 на входы матрицы 1 в видесигналов 7 - 9 и 10 - 12 . На выходах матрицы должен сформироватьсякод результата в виде сигналов 1517. Если результат соответствует значениям входных кодов, то блок 5 контроля вырабатывает сигнал на выходе13. При получении неправильного ре" зультата блок 5 контроля вырабатыва- ет сигнал на выходе 14.В такте коррекции и выдачи правильного результата сумматор работает следующим образом. Если в такте контроля. выработан сигнал на выходе13, то переключатели 2 и 3 пропускают коды входных вычетов на входы матрицы 1, а переключатель 4 - правильный результат на выход сумматора на прямую синхронно.с сигналом б.2. Если же в такте контроля выработан сигнал на выходе 14, то переключатели 2 и 3 синхронно с сигналом 6.2 производят циклическое переключение вход ных сигналов (например, для первой комбинации входных вычетов вместо 7 возбудится 8, а вместо 10 ф ф). За счет этого происходит перекоммутация неисправных цепей на исправные 2 О и возбуждение исправного выхода матрицы 1 (например, для первой комбинации входных вычетов вместо 15 возбудится 1 б). Переключатель 4 транспортирует полученный сигнал на выход 25 сумматора, соответствующий исходным входным кодам (например, для уже упомянутой комбинации вычетов сигнал с выхода 17 передается на выход 18 сумматора),Сопоставительный анализ известно-( го и предлагаемого устройств показывает, что существенным преимуществом последнего является повышенная надежность работы. Предлагаемое устройство правильно функционирует при возникновении сбоев типа невозбуждение выходных шин матрицы 1 и выдает правильные результаты суммы вычЕ- тов. Это достигается эа счет коррекции сбоев указанного типа, которые ,составляют достаточно обширный класс сбоев, Прототип этим свойством не обладает. Необходимые аппаратурные затраты (фиг. 3 - 5) незначительны и оправданы. Снижение надежности устройства вследствие введения дополнительного оборудования несущественно, так как современная элементная база имеет низкие значения интенсивности отказов, Выигрыш в надежности благодаря коррекции сбоев существенно преобладает над проигрышем из"за введения дополнительного оборудования,Использование предлагаемого устройства позволит повысить надежность функционирования. узлов аппаратурного контроля по модулю три, а также узов ЭВМ; в которых применяются "умма- торы по модулю три.1010626 г =1 уг =1 4=1 %=11йм а ИроМеьно Юоо ЙЬй Щи д оставитель И,Сигало ехред Ж,Касителевич едактор П.Макаревич Е. орре исн комит и откр аушска ПП ФПатентф, г.ужгород, ул.Проектная,или 1=11 Уг й ФраФыьийЮюй4 2490/38 Тираж 704 ВНИИПИ Государственного по делам изобретений 113035, Москва, Ж, Подла СССРийнаб д, 4/

СмотретьЗаявка

3354123, 18.11.1981

ПУШКИНСКОЕ ВЫСШЕЕ ОРДЕНА КРАСНОЙ ЗВЕЗДЫ УЧИЛИЩЕ РАДИОЭЛЕКТРОНИКИ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

ИЗОСИМОВ ВИКТОР АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H03M 13/51

Метки: коррекцией, модулю, ошибок, сумматор, табличный, три

Опубликовано: 07.04.1983

Код ссылки

<a href="https://patents.su/6-1010626-tablichnyjj-summator-po-modulyu-tri-s-korrekciejj-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Табличный сумматор по модулю три с коррекцией ошибок</a>

Предыдущий патент: Многоканальное устройство для обслуживания запросов

Следующий патент: Устройство выбора диапазона измерения для статистического анализа

Случайный патент: Способ изготовления жгутов из проводов