Табличный сумматор по модулю три с коррекцией ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

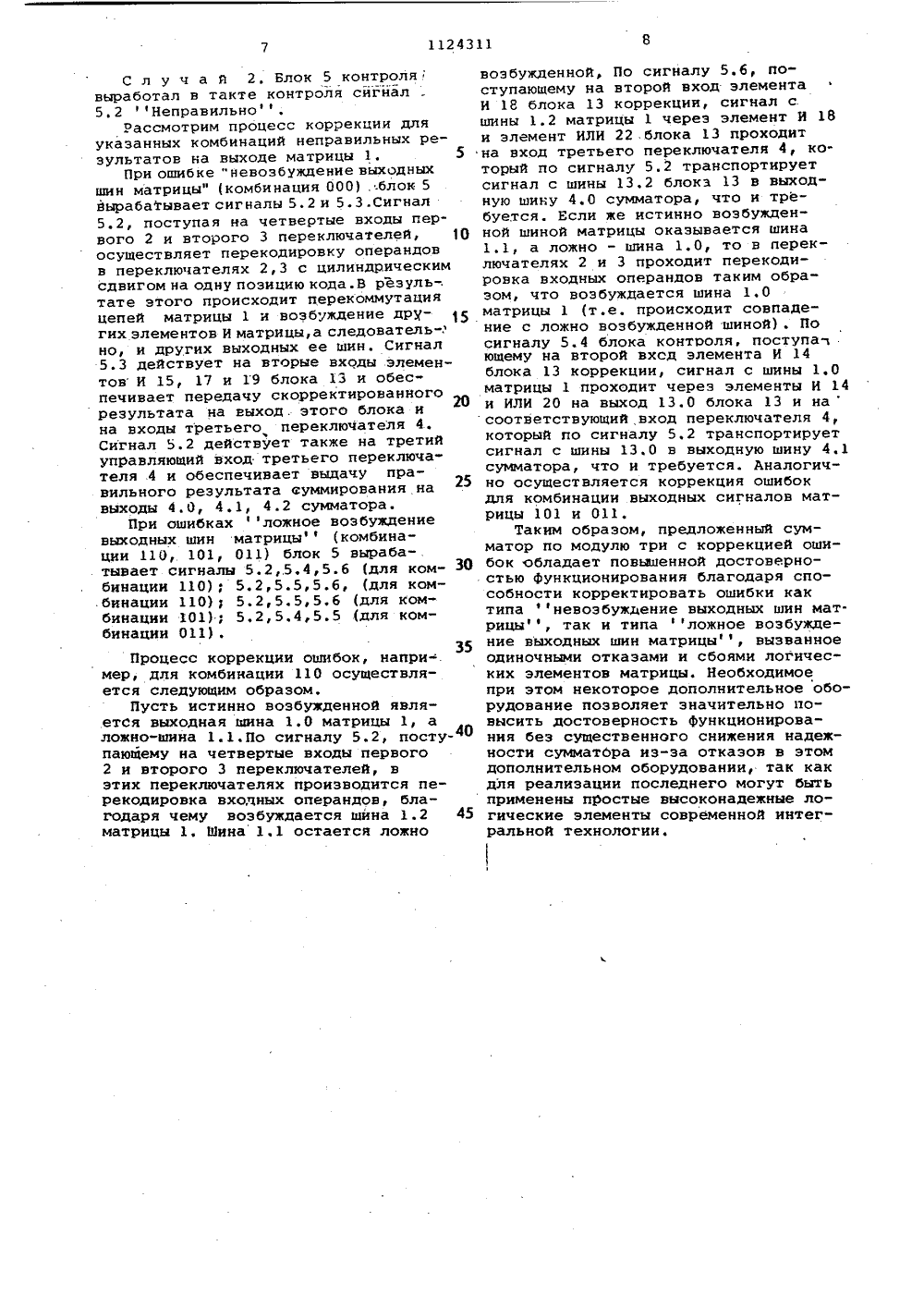

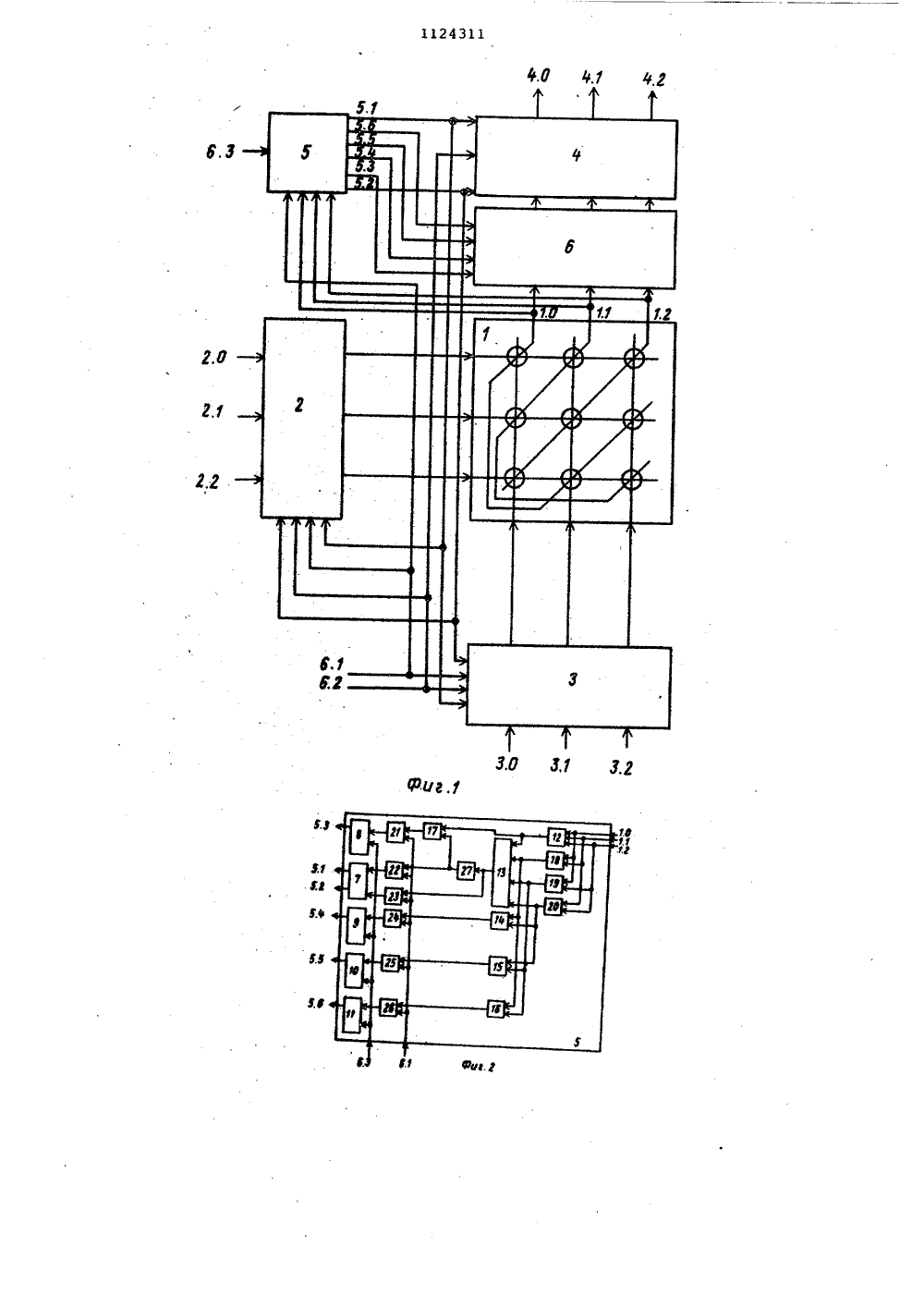

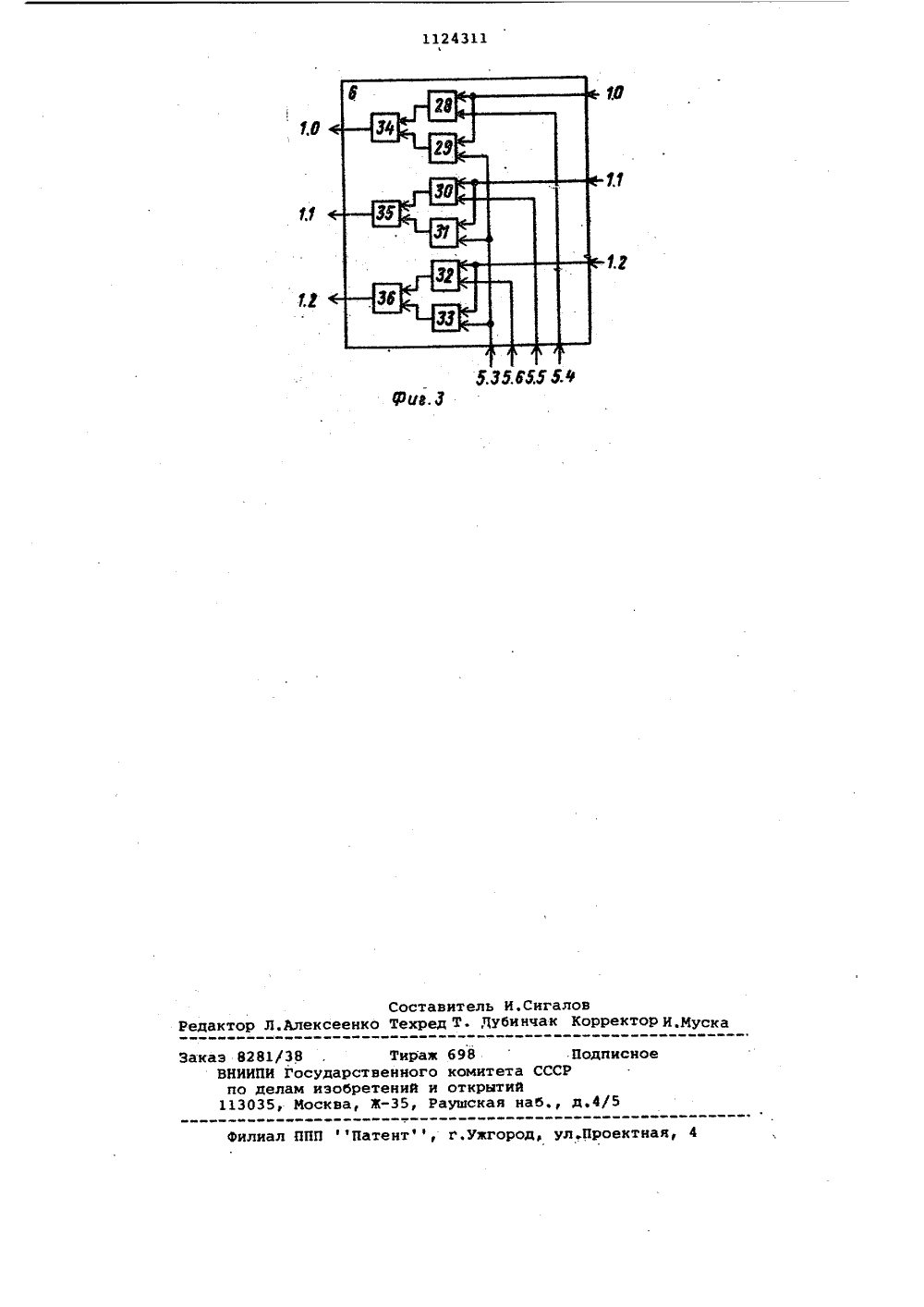

(59 С 06 Г ЕТЕНУ Ивет ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ ИЗОБ Н АВТОРСКОМУ СВИДЕТЕЛЬСТ(54)(57) ТАБЛИЧНЫЙ СУММАТОР ПО МОДУЛЮ ТРИ СКОРРЕКЦИЕЙ ОШИБОК, содержащий матрицу элементов И, первый,второй, третий переключатели и блокконтроля, содержащий первый триггер,пять элементов И и элемент ИЛИ-НЕ,причем первый, второй и третий контролирующие выходы элементов И матрицысоединены соответственно с первым,вторым и третьим входами элемента ИЛИНЕ блока контроля, первый вход элемента ИЛИ-НЕ блока контроля соединен спервыми входами первого и второгоэлементов И, второй вход элементаИЛИ-НЕ блока контроля соединен свторым входом первого элемента И ипервым входом третьего элемента Иблока контроля, третий вход элемента ИЛИ-НЕ блока контроля соединен свторыми входами второго и третьегоэлементов И блока контроля, выходычетвертого и пятого элементов И блока контроля соединены соответственно с единичным и нулевым входами первого триггера блока контроля, первыйтактовый вход устройства соединен спервыми входами четвертого и пятогоэлементов И блока контроля, с первыми управляющими входами первого ивторого переключателей, второй тактовый вход устройства соединен свторыми управляющими входами первого,второго и первым управляющим входомтретьего переключателя, входы перво- .го и второго операндов сумматора соединены соответственно с информационными входами первого и второго переключателей, выходы первого и второго переключателей соединены соответствен. но с первыми и вторыми входами элементов И, входами матрицы, единичный выход первого триггера блока контроля соединен с третьими управляющими входами первого, второго и вторым управляющим входом третьего переключателей, нулевой выход первого триггера блока контроля соединен с четвертыми управляющими входами .первого, второго и третьим управляющим входом третьего переключателей, о т л и чающий с я тем, что, с целью повышения достоверности, в него ввеР ден блок коррекции, содержащий шесть элементов И и три элемента ИЛИ, причем каждый 1-й выход матрицы элементов И (где=1,2,3) соединен с первыми входами (2 - 1) -го и 2 1-го элементов И блока коррекции, выходы (21 в 1)-го Я и 21-го элементов И блока коррекции соединены соответственно с первым и вторым входами 1-го элемента ИЛИ блока коррекции, выходы элемен гов ИЛИ блока коррекции соединены с информационными входами третьего переключателя, выходы которого являются выходами результата сумматора, причем в блок контроля введены элемент НЕ, пять элементов ИЛИ, шестой,седьмой,восьмой, девятый элементы И,выход первого элемента ИЛИ соединен с вторым входом пятого элемента И и через элемент НЕ с вторьм входом четвертого элемента И и первым входом второго элемента .ИЛИ, выход которого соединен с первым входом шестого элемента И блока контроля, выход элемента ИЛИ-НЕ соединен с вторым входом второго элемента ИЛИ и первым входом первого элемента ИЛИ блока контроля, выходы третьего, четвертого и пятого элементов ИЛ соединены с первыми входами соот1124311 ственно седьмого, восьмого и девятого элементов И, выход первого элемента И соединен с вторым входом пер"ного элемента ИЛИ и первыми входамитретьего и пятого элементов ИЛИ блока контроля, ныход второго элементаИ соединен с вторым входом первогоэлемента ИЛИ и первым входом четвертого и вторым входом пятого элементов ИЛИ блока контроля, выход третьего элемента И соединен с третьимвходом первого элемента ИЛИ и вторыминходами третьего и четвертого элементов ИЛИ блока контроля, первый тактовый вход блока контроля соединенс вторыми входами шестого, седьмого,1Изобретение относится к цифровой вычислительной технике и может исполь. зоваться в системах аппаратного контроля ЭВМ и устройств, функционирующих н системе остаточных классов:Известен табличный сумматор по модулю три, содержащий две группы . элементов И, ИЛИ, узел контроля ошибки и имеющий две группы входных шин, на которые подаются слагаемые, и одну о группу выходныхшин, на которых получается результат суммирования, причем выходные шины соединены с входами узла контроля ошибок, на выходе которого формируется сигнал ошибки при возникновении неправильного результата суммирования 1 .Недостатком такого сумматора является невозможность корректировать ошибкиНаиболее близким к предлагаемому 20 по техниче .кой сущности является табличный сумматор по модулю три с коррекцией ошибок, содержащий матрицу элементов И, блок контроля, первый, второй, третий переключатели, причем 25 входы блока контроля соединены с соответствующими ныходами матрицы, входы первой и второй групп входных сигналов сумматора соединены с соответствующими входами первого и вто- Зр рого переключателей, выходы которых соединены с соответствующими входами матрицы элементов И, выходыматрицы элементов И соединены с соответствующими входами третьего переключателя, выходы которого являются информационными выходами сумматора, первый вход синхронизации которого соединен с первыми тактовыми входами первого и второго переключателей и блока контроля, вто рой вход синхронизации сумматора соединен с вторыми тактовыми входами восьмого и денятого элементов И, выходы которых соединены с единичнымивходами соответственно второго, третьего, четвертого и пятого триггерон,третий тактовый вход блока контролясоединен с нулевыми входами второго,третьего, четвертого и пятого триггеров блока контроля, единичныйвыход второго триггера блока контроля соединен с вторыми входами вто"рого, четвертого и шестого элементов И блока коррекции, единичныевыходы третьего, четвертого и пятоготриггеров блока контроля соединеныс вторыми входами соответственно первого, третьего И пятого элементов Иблока коррекции,2первого, второго переключателей итактовыми входами третьего переключателя, первый выход блока контролясоединен с первыми управляющими входами первого, второго и третьегопереключателей, второй выход блокаконтроля соединен с вторыми управляющими входами первого, второго итретьего переключателей 23,Недостатком этого устройства является то, что оно не способно корректировать ошибки типа ложноевозбуждение выходных шин матрицыпри возникновении одиночных отказови сбоев в матрице.Цель изобретения повышение достоверности функционирования табличного сумматора по модулю три путемрасширения его возможностей по коррекции ошибок типа ложное возбуждение выходных шин матрицы вызванных одиночными отказами и сбоямив матрице элементов И,Поставленная цель достигаетсятем, что в сумматор по модулю трис коррекцией ошибок, содержащий матрицу элементов И, первый, второй,третий переключатели и блок контроля, содержащий первый триггер, пятьэлементов И и элемент ИЛИ-НЕ, причемпервый, второй и третий контролируемые выходы элементов И матрицысоединены соответственно с первым,вторым и третьим входами элементаИЛИ-НЕ блока контроля, первый входэлемента ИЛИ-НЕ блока контроля соединен с первыми входами первого ивторого элементов И,второй вход элемента ИЛИ-НЕ блока контроля соединенс вторым входом первого элемента Ии первым входом третьего элемента Иблока контроля, третий вход элементаИЛИ-НЕ блока контроля соединен с вторыми входами второго и третьего эле5 10 15 20 ментов И блока контроля, выходы четвертого и пятого элементов И блокаконтроля соединены соответственно сединичным и нулевым входами первоготриггера блока контроля, первый тактовый вход устройства соединен с первыми входами четвертого и пятого элементов И блока контроля, с первымиуправляющими входами первого и второго переключателей, второй тактовыйвход устройства соединен с вторымиуправляющими входами первого, второго и первым управляющим входом третьего переключателя, входы первогои второго операндов сумматора соединены соответственно с информационными входами первого и второго переключателей, выходы первого и второго переключателей соединены соответственно с первыми и вторыми входами элементов И, входами матрицы,единичный выход первого триггераблока контроля соединен с третьимуправляющими входами первого, второго и вторым управляющим входомтретьего переключателей, нулевойвыход первого триггера блока контроля соединен с четвертыми управляющими входами первого, второго и третьимуправляющим входом третьего переклйчаталей, введен блок коррекции,содержащий шесть элементов И и три 30элемента ИЛИ, причем каждый -йвыход матрицы элементов И (где =1,2,3) соединен с первыми входами,коррекции, выходы (2- 1) -го и2 1-го элементов И блока коррекциисоединены соответственно с первыми вторым входами -го элемента ИЛИблока коррекции, выходы элементовИЛИ блока коррекции соединены"0с информационными входами третьего,переключателя, выходы которого являются выходами результата сумматора, причем в блок контроля введеныэлемент НЕ, пять элементов ИЛИ,ыестой, седьмой, восьмой, девятый эле менты Й, выход первого элемента ИЛИсоединен с вторым входом пятого элемента И и через элемент НЕ с вторымвходом четвертого элемента И и первымвходом второго элемента ИЛИ, выход50которого соединен с первым входом шестого элемента И блока контроля, выход элемента ИЛИ-НЕ соединен с вторым входом второго элемента ИЛИ ипервым входом первого элемента ИЛИ 55блока контроля, выходы третьего, четвертого и пятого элементов ИЛИ соединены с первыми входами соответственно седьмого, восьмого и девятогоэлементов И, выход первого элемента И соединен с вторым входам первого элемента ИЛИ и первыми входамитретьего и пятого элементов ИЛИ блока контроля, выход второго элементаИ соединен с вторым входом первогоэлемента ИЛИ и первым входом четвер того и вторым входом пятого элементов ИЛИ блока контроля, выход третьего элемента И соединен с третьимвходом первого элемента ИЛИ и вторы"ми входами третьего и четвертого элементов ИЛИ блока контроля, первыйтактовый вход блока контроля соединенс вторыми входами шестого, седьмого,восьмого и девятого элементов И, выходы которых соединены с единичнымивходами соответственно второго,третьего, четвертого и пятого триггеров,третий тактовый вход блока контролясоединен с нулевыми входами второготретьего, четвертого и пятого триггеров блока контроля, единичный выход второго триггера блока контролясоединен с вторыми вхрдами второго,четвертого и шестого элементов Иблока коррекции, единичные выходытретьего, четвертого и пятого триггеров блока контроля соединены свторыми входами соответственно первого, третьего и пятого элементов Иблока коррекцииНа фиг.1, 2 и 3 изображена схема предлагаемого табличного сумматора по модулю три с коррекцией ошибок.Табличный сумматор по модулю три с коррекцией ошибок (фиг,1) содер" жит матрицу 1 элементов И, первый 2, второй 3, третий 4 переключатели, блок 5 контроля, содержащий первый триггер 6, первый 7, второй 8, третий 9, четвертый 10, пятый 11 элементы И, элемент ИЛИ-НЕ 12, блок 13 коррекции ошибок, содержащий первый 14, второй 15, третий 16, четвертый 17, пятый 18, шестой 19 элементы И, первый 20, второй 21, третий 22 элементы ИЛИ, при этом блок контроля дополнительно содержит элемент НЕ 23, первый 24, второй 25 элементы ИЛИ, шестой элемент И 26, третий 27, четвертый 28, пятый 29 элементы ИЛИ, седьмой 30, восьмой 31, девятый 32 элементы И, второй 33, . третий 34, четвертый 35, пятый 36 триггеры.Устройство работает следующим образом.В работе устройства целесообразно выделитьь два такта и рассмотреть их раздельно: такт контроля ( в момент поступления сигнала на первый тактовый вход 6,1 сумматора) и такт выдачи результата (при правильной работе матрицы 1) или коррекции ( при ошибке в работе матрицы 1) и выдачи правильного результата ( в момент поступления сигнала на второй тактовый вход 6.2 сумматора) .В такте контроля исходные операнды в однопозиционном коде подаются на входы 2.0, 2,1,2,2,3.0, 3.1, 3.2 сумматора и далее через первый 2 и второй 3 переключатели напрямую по45 С л у ч а й 2, Блок 5 контроля выработал в такте контроля сйгнал 5,2 Неправильно.Рассмотрим процесс коррекции для указанных комбинаций неправильных результатов на выходе матрицы 1, 5При ошибке "невоебуждение выходных шин матрицыф (комбинация 000) блок 5 вырабатывает сиг налы 5. 2 и 5. 3 . Сигнал 5.2, поступая на четвертые входы первого 2 и второго 3 переключателей 10 осуществляет перекодировку операндов в переключателях 2,3 с цилиндрическим сдвигом на одну поеицию кода. В резуль-. тате этого происходит перекоммутация цепей матрицы 1 и возбуждение других элементов И матрицы,а следователь-. но, и других выходных ее шин. Сигнал 5.3 действует на вторые входы .элементов И 15, 17 и 19 блока 13 и обеспечивает передачу скорректированного результата на выход. этого блока и на входы третьего переключателя 4. Сигнал 5.2 действует также на третий управляющий вход третьего переключателя 4 и обеспечивает выдачу правильного результата суммирования на выходы 4.0, 4,1, 4.2 сумматора.При ошибках ложное возбуждение выходных шин матрицы (комбинации 110,. 101, 011) блок 5 выраба-. тывает сигналы 5.2,.5,4,5.6 (для ком- ЗО бинации 110); 5,2,5.5,5,6, (для ком.бинации 110) 5.2,5.5,5,6 (для комбинации 101); 5.2,5.4,5.5 (для комбинации 011) .35Процесс коррекции ошибок, напри-. мер, для комбинации 110 осуществляется следующим образом.Пусть истинно возбужденной является выходная шина 1.0 матрицы 1, а ложно-шина 1.1,По сигналу 5.2, постуО пающему на четвертые входы первого 2 и второго 3 переключателей, в этих переключателях производится перекодировка входных операндов, благодаря чему возбуждается шина 12 матрицы 1, Шина 1,1 остается ложно воебужденной, По сигналу 5.6, поступающему на второй вход элемента И 18 блока 13 коррекции, сигнал с.шины 1.2 матрицы 1 черее элемент И 1 В и элемент ИЛИ 22.блока 13 проходит на вход третьего переключателя 4, который по сигналу 5,2 транспортирует сигнал с шины 13,2 блоке 13 в выходную шику 4.0 сумматора, что и требуетсяЕсли же истинно возбужденной шиной матрицы оказывается шина 1.1, а ложно - шина 1.0, то в переключателях 2 и 3 проходит перекодировка входных операндов таким образом, что воебуждается шина 1.0матрицы 1 (т.е. происходит совпадение с ложно возбужденной шиной) . По сигналу 5,4 блока контроля, поступа ющему на второй вход элемента И 14 блока 13 коррекции, сигнал с шины 1.0 матрицы 1 проходит черее элементы И 14 и ИЛИ 20 на выход 13.0 блока 13 и насоответствующий, вход переключателя 4, который по сигналу 5,2 транспортирует сигнал с шины 13.0 в выходную шину 4,1 сумматора, что и требуется. Аналогично осуществляется коррекция ошибок для комбинации выходных сигналов матрицы 101 и 011.Таким образом, предложенный сумматор по модулю три с коррекцией ошибок обладает повышенной достоверностью функционирования благодаря способности корректировать ошибки как типа фневоебуждение выходных шин матрицы, так и типа ложное возбуждение выходных шин матрицыф, вызванное одиночными отказами и сбоями логических элементов матрицы. Необходимое при этом некоторое дополнительное оборудование поеволяет эначительно повысить достоверность функционирования бее существенного снижения надежности сумматбра ие-еа отказов в этом дополнительном оборудовании, так как для реализации последнего могут быть применены простые высоконадежные логические элементы современной интегральной технологии..4 л ППП ффПатентф, г,ужгород, ул.Проектная,каэ 8281/38 ТираВНИИПИ Государственногпо делам иэобретений 113035, Москва, 3-35,698комитета открытийаушская н

СмотретьЗаявка

3608041, 20.06.1983

ПУШКИНСКОЕ ВЫСШЕЕ ОРДЕНА КРАСНОЙ ЗВЕЗДЫ УЧИЛИЩЕ РАДИОЭЛЕКТРОНИКИ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

ИЗОСИМОВ ВИКТОР АЛЕКСАНДРОВИЧ, ТЕРЕХОВ ВЛАДИМИР ГЕОРГИЕВИЧ, КУЛДЫКИН ВЛАДИМИР АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H03M 13/51

Метки: коррекцией, модулю, ошибок, сумматор, табличный, три

Опубликовано: 15.11.1984

Код ссылки

<a href="https://patents.su/7-1124311-tablichnyjj-summator-po-modulyu-tri-s-korrekciejj-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Табличный сумматор по модулю три с коррекцией ошибок</a>

Предыдущий патент: Устройство для свертки по модулю

Следующий патент: Устройство для контроля цифровых узлов

Случайный патент: Гидросистема управления трансмиссией ходовой части лесозаготовительной машины