Цифровой интегратор для однородных цифровых интегрирующих структур (оцис) с плавающей запятой

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 510727

Авторы: Виневская, Гиляровская, Недостоева, Станишевский

Текст

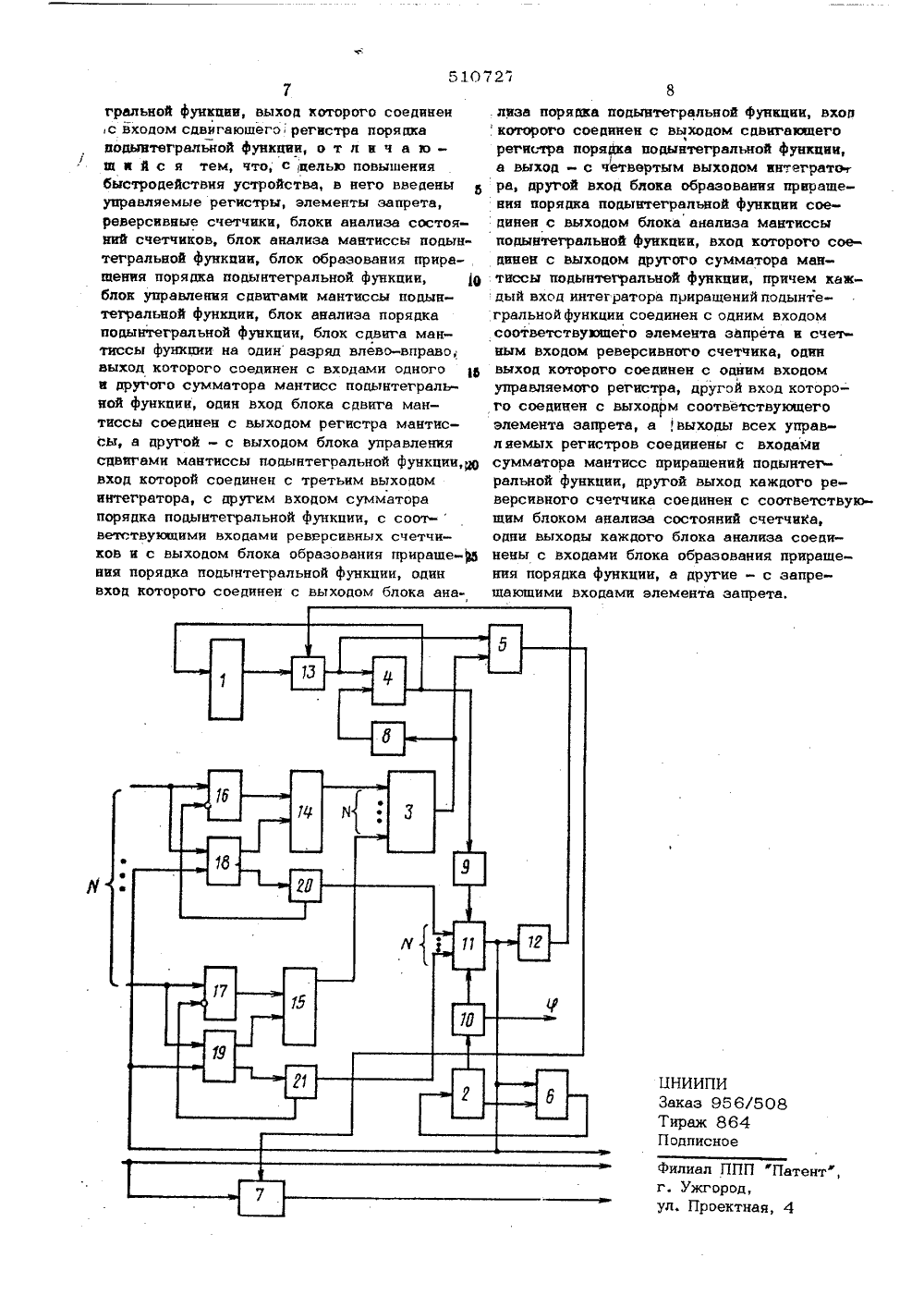

(ц) 510727 ОПИСАНИЕИЗОБРЕТЕН ИЯК АВТОР СКО 4 йУ СВИДЕТЕЛЬСТВУ Союз Советскии Социалистические Республик(51) М. Кл506 3 1/О с присоедине осударстоеииый комет Совета Миииотроа ССС по делам изооретеиий и открытий(ФЗ) Опубликовано 15,04,76 Бюллетень14 (45) Дата опубликования описания 30.06.77) Заявител иотехничес инст ганрогск ГРИРУЮЩИ лагаем тройство относиной техники иециализированнь к области вычислите спользоваться в с овых вычислитель может х цифых машинах. женки пр ком и операц жение После О нап ма мантис екци пим их и(54) ЦИФРОВОЙ ИНТЕГРАТОР ДЛСТРУКТУ Известен цифровой интегратор пля однородных цифровых интегрирующих структур с плавающей запятой, работающий в последовательном коде по формуле трапеций и содержащий сдвигающий регистр мантиссы подынтегральной функции, сдвигающий регистр пор"дка подынтегральной ФУнкции, сум матор порядка подынтегральной функции, сумматор мантисс приращений подынтеграль ной функции, множительный блок, блок задержки, сумматоры мантисс- подынтеграль ной функции, выход одного сумматора мантиссы попынтегральной функции соединен с одним входом множительного блока, другой вход которого соединен с одним входом и с первым выхопом интегратора, а выход - с вторым выходом интегратора, причем выход сумматора мантисс приращений подынтегральнэй функции соединен с одним входом одного сумматора подынтегральной функции ДНОРОДНЫХ ЦИФРОВЫХ ИПЛАВАЮЩЕЙ ЗАПЯТОЙ и с входом блэка задержки, выход кэтэрэго сэединен с одним вхэдэм другэгэ сумматора пэдынтегральнэй функции, выход кэторэгэ соединен свходом сдвигаюшегэ регистра мантиссы пэдын тегральнэй функции, а выхэд сдвигающегэрегистра порядка попынтегральной функциисоединен с одним входом сумматора порядка подынтегральной функции, выход которогосоединен с входом сдвигающегэ регистра и порядка подынтегральной функции. днако известный интегратор имеет маскорость вычислений, так как при слоприращений число с меньшим порядиводится к числу с большим поряд- только после этого производится ия сложения над мантиссами. Умно- сопровождается сложением порядков. выполнения арифметических операций нтиссами произ во питс я нормализация сы результата с опнэвременной корй порядка. Кроме того, усложняется ча информации между блоками: необперепавать помимо мантисс еше и янки.С целью повышения быстродействия цщррового интегратора; с плавающей запятой впредлагаемое устройство введены управляемые. регистры, элементы запрета, реверсивные счетчики, блоки анализа состояний счеч 5чиков, блок анализа мантиссы подынтегральной функции, блок образования приращенияпорядка подынтегральной функции, блок уп.равления сдвигами мантиссы подынтеграль-ной функции, блок анализа порядка подын- фтегральной функции, блоксдвига мантиссы функции на один разряд влево-вправо, выход которого соединен с входами одного и другого сумматора мантисс подынтегральной функции, один вход блока сдвига ман тиссы соединен с выходом регистра мантиссы, а другой - с выходом блока управления сдвигами мантиссы подынтенгральной функции, вход которого соединен с третьим выходом интегратора, с другим вхо- яО дом сумматора порядка подынтегральной функции, с соответствующими входами ре 1версивных счетчикоь и с выходом блока образования приращения порядка подынтегральной функции, один вход которого соединен,25 с выходом блока анализа порядка подынтегральной функц, вход которого соединен с выходом сдвигающего регистра порядка падынтегральной функции, а выход - с четвертым выходом интегратора, другой вход Ю блока образования приращения порядка подынтегральной функции соединен с выходом блока анализа мантиссы подынтегральной функции, вход котооого соединен с выходом другого сумматора мантиссы подынтегральной 3 функции, причем каждый вход приращений подынтегральной функции интегратора соединен с одним входом соответствующего элемента запрета и счетным входом реверснврого счетчика, один выход которого сое 40динен с одним входом управляемого регистра, другой вход, которого соединен с выходом соответствующего элемента запрета, а выходы всех управляемых регистров соединены с входами сумматора мантисс при- ф 5ращений подынтегральной функции другой выход каждого реверсивного счетчика соединен с соответствующим блоком анализасостояний счетчика, одни выходы каждогоблока анализа соединены с входами блокаобразования приращения порядка функции, а другие - с запрещающими входами элемента запрета.На чертеже показана блок-схема предлагаемого устройства. М Интегратор содержит регистр 1 мантиссы подынтегральной функции длиной и разрядов, регистр 2 порядка функции длиной Ц разрядов, сумматор 3 мантисс приращений, 60 сумматоры 4 и 5 мантисс подынтегральнойфункции, сумматор б порядка функции, множительной блок 7, блок 8 задержки, блоИОанализа мантиссы подынтегралъной фунюян,блок 10 анализа порядка функции, блок 11образования приращения порядка функции,блок 12 управления сдвигами мантиссыфункции, блок 13 сдвига мантиссы функциина один разряд влево-вправо, управляемыерегистры 14 и 15, элементы запрета 16и 17, реверсиьные счетчики 18 и 19, блоки 20 и 21 анализа состояний счетчиков.Вычисления в цифровом интеграторе цро;изводятся по формуламнУР(ф)С УР ф 2УР(ф)нУРн 4) = УРА+Я. 7 УРФ(1+4),ЧЕХ) = УР(4) .Р 7 Ус (юХ)где Ур(фью)- среднее значение функции на данном шаге интегрирования;ЯУр 0 (+1) - квантованное приращениеподынтегральной функции,7 У ( 1) - квантованное прираще-ние переменной интегрирования,ЧЪ (11) - приращение интегралана данном шаге интегрирования,Ю - число входов приращений подыптегральной функции.В данном цифровом интеграторе подВтнтегральная функция ) "представлена в виде мантиссы в дополнительйом модибицированном коде и порядка., прирашенияЧУрф 1),ФУ(1) - в виде мантисс и одноразрядныхприращений,порядка.Работает интегратор следующим образом,На входы интегратора на (1 )-омшаге интегрирования поступают приращенияподынтегральной функции в виде одноразрядных приращений порядков 7 П(1 1) и 7 ПР 0( 1 ф 4 ) и квантованных мантиссЧМ с (Ц и 7 Мр 0(+1),д =4,2 И).Приращения порядков 7 П)3 1) (+ 1 ) приращений подынтегральной функции поступают на счетчики 18 и 19, где образуются новые значения разностей порядковДв результате чего перестраиваются управ ляемые регистры 14 и 15, на выходе бл ков анализа состояний счетчиков 18 и 19 появляются потенциалы, соответствующие новым состояниям счетчиков, которые подготавливают элементы запрета 16 и 17.При прохождении мантисс приращений 7 Мр 91) через управляемые регистры 14 и 15 мантиссы задерживаются в них на величинуи - Ь д ( )) определяемую510727 ГТПР(1+1) равный +1, - 1 илн О. Этисигналы поступают на вход блока 12 управления сдвигами мантиссы функции, нц сумматор 6, на выход интегратора в качествевыходного приращения порядка функцияЧПР ( 1 ф 1 ) н на реверсивные счетчаки18 и 19,Блок 12 управления сдвнгами вырабатывает сигналы сдвига мантнссы подынтеграл1 а ной фунции вправо при ЧПр 1 +1)=ф 1 иливлево прнЧПр1) = - 1 . Этн сигналыпоступают на блок 13 сдвига на один разряд влево-вправо мантиссы функции, кромеого, по ним происходит сдвит (нормалнза)ф ция), В данном шаге происходит сдвиг мантиссы по сигналам, выработанным в предыдущем шаге интегрирования.Прнращение порядка ЧПр ( ( 4 1 ) поступает на сумматор 6, где складывается сМ порядком функции, находящимся в регистре2. На выходе сумматора 6 формируется новое значение порядка П р (+ 1 ) функции,которое записывается в регистр 2.. Сигнал ЧПр (1 ф с выхода блока 11И поступает на реверсивные счетчики 18 н19 и на один выход интегратора.Приращение порядка Ч и(1) переменной интегрирования поступает непосредственно на другой выход интегратора,ЭО На третий выход интегратора с выходамножнтельного блока выдается мантиссаприращения интеграла. Пр -2Лр2.Первый поступает на вход блока 11 образования приращения порядка функции в качестве одного из управляющих сигналов при формировании Ч П р ( 1 1 1 ) - 1 , второйна выход интегратора как сигнал переполненияБлок 11 образов-яия приращения порядка функции по результатам анализа поступающих сигналов вырабатывает сигнал Ч ПрО 5состоянием счетчиков 18 и 19, а мантисса подынтегральной функции Мр ( 1 + 4 ) в это время задерживается на И разрядов в регистре 1, В результате мантиссы прира щений сдВигаются вправо отнэсительнэмантнссы функции на величину разностей порядковь 9 41) = Пр -ПрФ ( 1( ).Величина Ь д (11), с помощью блока образования приращений порядка функции всегда поддерживается положительной.Если величина,Ь (Й 1) больше длины рравляемого регистра, то с помощью эле ментов запрета 16 и 17 прохождение мантиссЧМру (141) на регистры 14 и 15 запрещается посредством подачи на запрешаюшне входы элементов запрета 16 и 17 сигналов с выходов блоков 20 и 21, соответствующих значениям разностей норядкдЬ Ь 9 ( 1 ф 1 ), большим длины управляемого регнстра.На выходе управляемых регистров 14 и 15 приращения подынтегральной функции имеют порядок функции Пр. Следовательно, все слагаемые поступают на входы сумматоров 3, и 5 и через блок 8 на входы сумматора 4 в одном порядке.Блоки 20 н 21 вырабатывают также сигналы о состояниях счетчиков 18 и 19, при одном из которых в блоке 11 образования приращения порядка ЧПр ( 1+ 1 ) формируется Чпр ( 1+ 3, ) = + , а при другом в том же блоке 11 - отрицательное приращение ЧП р ( 1 1 ) = -1.Блок 9 анализа мантиссы подынтегральной функции вырабатывает сигналыЮр(1)1 Ч Мр(1) с-и2 мр-2 ..Первый поступает на вход блока 11 образования приращения порядка функции и качестве одного из управляющих сигналов при формировании Ч Л р (1 4 3 ) =+ 1, второй - при формировании Ч П р ( 4+ М )= -1.Блок 10 анализа порядка подынтегральной функции вырабатывает сигналы Формула изобретения Цифровой интегратор для однородных цифровых интегрирующих структур с плавающей запятой, содержаший сдвигавший регистр мантиссы подынтегральной функции, сдвигающий регистр порядка подынтегральной функции, сумматор порядка подынтегральной функции, сумматор мантисс приращенийподынтегральной функции, множительный блок, блок задержки, сумматоры мантисс подынтегральной функции, выход одного сум матора мантиссы подынтегральной функция соединен с одним входом множительного блока, другой вход которого соединен с одним, входом и с первым выходом интегратора, а выход - с вторым выходом интегратора, причем выход сумматора мантисс приращений подынтегральной функции сое динен с одним входом одного сумматора подынтегральной функции и с входом блока задержкя, выход кэтэрэго сэединен с одним вхэдэм другэго сумматора пэдынтегральнэй функции, выход кэтэрэгэ сэедияен с вхэдэм сдвкгдющего регистра мантиссы подынтегральной функции, а выход сдвигаю 1 цего регкстра порядка подынтегральцой функции соединен с одним входом сумматора порядка подынте51072 " Заказ 956/508Тираж 864Подписное гральной функции, выход которого соединенс входом сдвигаюшего регистра порядкаподывтегральной функции, о т л и ч а ющ и й с я тем, что; с целью повышениябыстродействия усгройства, в него введеныуправляемые регистры, элементы запрета,реверсивные счетчики, блоки анализа состояний счетчиков, блок анализа мантиссы подынтегральной функции, блок образования приращения порядка подынтегральной функции, рблок управления сдвигами мантиссы подынтегральной функции, блок анализа порядкаподынтегральной функции, блок сдвига мантиссы функции на один разряд влево-вправо,выход которого соединен с входами одного ри другого сумматора мантисс подынтегральной функции, один вход блока сдвига мантиссы соединен с выходом регистра мантиссы, а другой - с выходом блока управлениясдвигами мантиссы подынтегральной функции,дрвход которой соединен с третьим выходоминтегратора, с другим входом сумматорапорядка подынтегральной функции, с соот-ветствующими входами реверсивных счетчиков и с выходом блока образования прираще-фния порядка одынтегральной функции, одинвход которого соединен с выходом блока ана 8лиза порядка подынтегральной функции, входкоторого соединен с выходом сдвигающего регистра поряха подынтегральной функции, а выход - с четвертым выходом интегратор ра, другой вход блока образования приращения порядка подынтегральной функции соединен с выходом блока анализа мантиссы подынтегральной функции, вход которого соединен с выходом другого сумматора мантиссы подынтегральной функции, причем каждый вход интегратора приращений подынтегральнойфункцин соединен с одним входом соответствующего элемента запрета и счетным входом реверсивного счетчика, один выход которого соединен с одним входом управляемого регистра, другой вход которого соединен с выходом соответствующего элемента запрета, а ,выходы всех управляемых регистров соединены с входами сумматора мантисс приращений подынтет- ральной функции, другой выход каждого реверсивного счетчика соединен с соответствующим блоком анализа состояний счетчика, одни выходы каждого блока анализа соединены с входами блока образования приращения порядка функции, а другие - с запрещающими входами элемента запрета. филиал ЛПП Патент", г. Ужгород,ул. Проектная, 4

СмотретьЗаявка

1945469, 17.07.1973

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

СТАНИШЕВСКИЙ ОЛЕГ БОРИСОВИЧ, ВИНЕВСКАЯ ЛИДИЯ ИВАНОВНА, ГИЛЯРОВСКАЯ ЕВГЕНИЯ БОРИСОВНА, НЕДОСТОЕВА ЛЮДМИЛА МИХАЙЛОВНА

МПК / Метки

МПК: G06J 1/02

Метки: запятой, интегратор, интегрирующих, однородных, оцис, плавающей, структур, цифровой, цифровых

Опубликовано: 15.04.1976

Код ссылки

<a href="https://patents.su/4-510727-cifrovojj-integrator-dlya-odnorodnykh-cifrovykh-integriruyushhikh-struktur-ocis-s-plavayushhejj-zapyatojj.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой интегратор для однородных цифровых интегрирующих структур (оцис) с плавающей запятой</a>

Предыдущий патент: Устройство для моделирования канала связи

Следующий патент: Пневматическо е печатающее устройство

Случайный патент: Способ импульсного измерения расхода электропроводящей жидкости в трубопроводе