Запоминающее устройство с блокировкой неисправных запоминающих ячеек

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

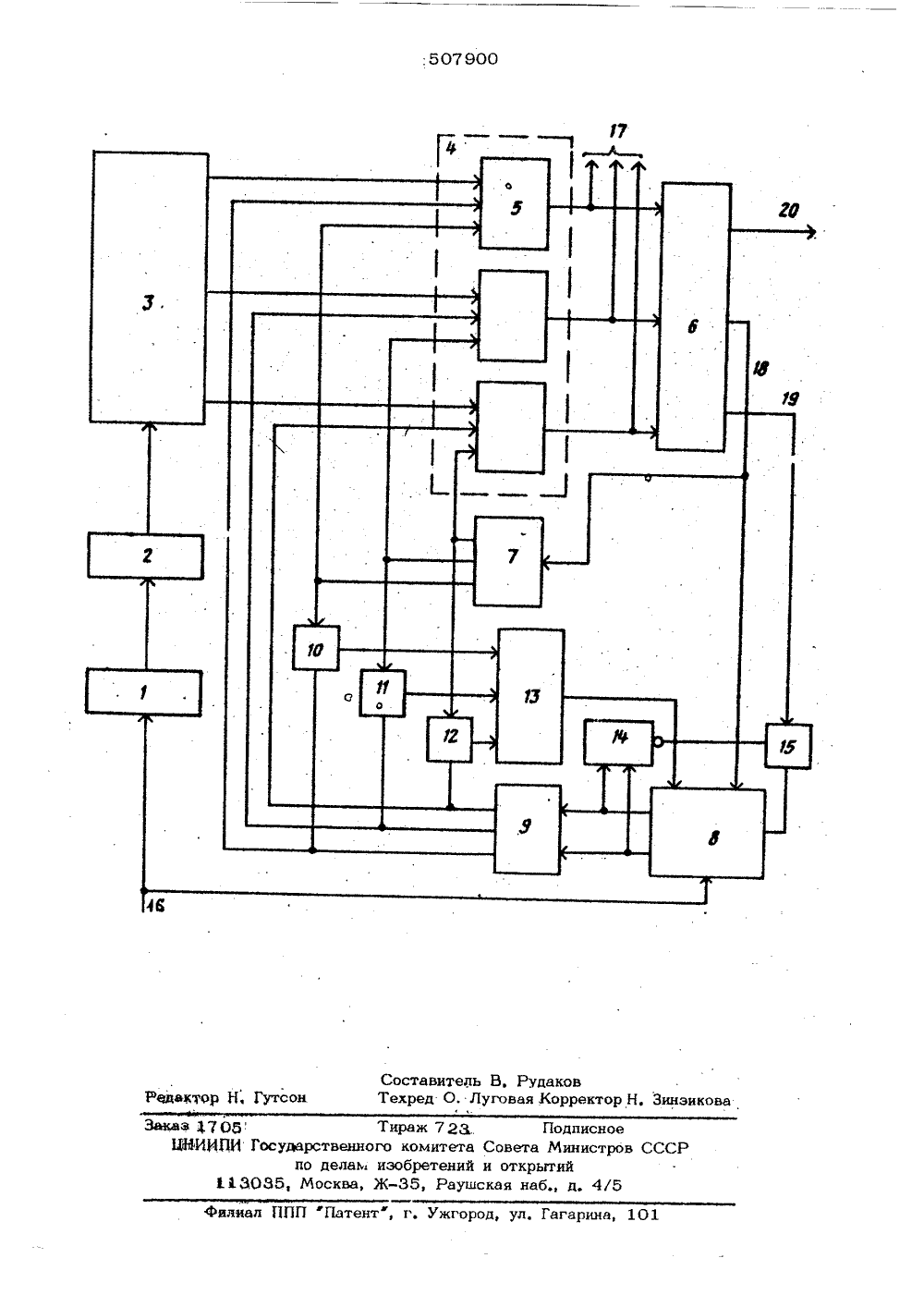

фратор 9, элементы И 0-12, первый и второй элементы ИЛИ13 и 14 и.дополнительный элемент И;, 15, Накопитель 8 может быть реализовав как в виде ассоциативного запоминающего устройства, так и в виде полноадресного оперативного запоминающего устройства.Входы регистра адреса 1 и адресные входы накопителя 8 соединены с шинами кода адреса 16. Выходы регистра адреса 1 соединены через дешифратор адреса 2 с накопителем 3, выходы которого подключены ко входам регистра 4. Выходы регистра 4 подключены ко входам блока 6, а также к выходным информационным шинам 17, Информационные выходы 18 блока 6 подключены к информационным входам накопителя 8 и входам дешифратора 7, выходы которого соединены со входами регистра 4, Информационные выходы накопителя 8 соединены со входами дополнительного дешифратора 9, а выходы последнего подключены ко входам регистра 4. Соответствующие одним и тем же-информационным разрядам выходы дешифраторов 7 и 9 соединены со входами элементов И 10-12, выходы которых соединены со входами первого элемента 49 ЛИ 13, а его выход подключен к управляющему входу накопителя 8. Входы второго элемента ИЛИ14 подключены к информационным выходам накопителя 8, его выход соединен с одним входом дополнительного элемента И 15, другой вход которого соединен с выходом 19 блока 6, а выход подключен к управляющему входу накопителя 8. Сигнал многократной (двойной) ошибки выдается по ш 1 ше 20. Работает устройство следующим обраЗОМ.Код адреса одноврцменно подается на,регистр адреса 1 и адресные. входы накопителя 8, При обращении по исправномуадресу. работа устройства происходит какобычно; выбранное с помощью дешифратора адреса 2 слово из накопителя 3 поступает па регистр 4, а затем на выходныешины 17 и входы блока 6, В этом случаеокорректирующая информация на выходахдешифраторов 7 и 9 отсутствует,При возникнорении в процессе опросасбоя или повреждения в .запоминающейячейке, приводящих к искажению информации в одном разряде слова, блок 6 выдает корректирую 1 цую инфорлац 111 О, которая,пройдя дешифратор 7, исправляет информацию в регистре 4. Одноврел 1 енно с эт 1 лкоя)ектируъ:цая 1 иИ)р 5 аци 5 От Олока 6ПООтун 1 ет 1 я вход Окоште;51 Ь н О О 11 б 10 15 20 И 30 35 40 55 4налу одиночной ошибки по шине 20 от блока 6 заносится в него, На выходе решифратора 9 при этом отсутствует какая- либо информация (все нули). Если накопитель 8 представляет собой ассоциативное запоминающее устройство, то в прианаковой части его запоминается, кроме того, и адрес слова, в ъотором обнаружена ошибка; в случае оперативного запоминающего устройства корректирующая информация записывается по адресу, соответствующему коду адреса на шинах 16. При вторичном обращении по этому же адресу возможны два случая в зависимости от того, что было исправлено перед этим - сбой или отказ запоминающей ячейки, Пусть был исправлен отказ. Тогда при вторичном обращении по тому же адресу (при отсутствии новыхщ отказов или сбоев) та же неисправная ячей- ка опять выдает неверную информацию в регистр 4. Однако, при этом накопитель 8 выдает записанную в него по этому адресу корректирующую информацию и дешифратор 9 исправит информацию в регистре 4, Так как сигнал дешифрато 9 поступает на регистр 4 не позже слова из накопителя 3, то блок 6 не обнаруживает ошибки, на выходе дешифратора 7 сигналы отсутствуют и на выходные шины 17 поступает исправная информация. При появлении в этом случае сбоя или неисправности в другом разряде савва (т.е. второй ошибки), она исправляетсяблоком б,тогда как первая .исправляетсяЪакопителем 8, Информация от блока 6 о второй ошибке не заносится в накопитель 8, чтобы не испортить хранимую в нем информацию о первой ошибке.Итак устройство имеет возможность исправить уже одновременно две ошибки в слове ( при последовательном их появлении)1 тогда как код Хемминга может исправить лишь одну. При появлении третьей ошибки или одновременно двух и более ошибок, данное устройство не может их корректировать и выдает по шине 20 сигнал многократной ошибки. Пусть по данному адресу первоначально была исправлена ошибка от сбоя, тогда при вторичном Обрашейии по этому адресу (при отсутствии других новых ошибок вытом слове) на регистр 4 из накопителя 3 поступит исправная информация, однако Она сразу же исказится в тол 5 разряде, в которол 1 был сбой в первый раз, так как инвентируОшая информация об эты 1 разряде была занесена по этому адре у в накопитель 8, Вследствие этого блок 6 также выд.ст корректируО 1 уи нпфо)01511 О 11 О ттлу я. р 15 Цу н 1 О 11;Фчтн 1,ходУОО .з;" 1, .ОЦ . , 111,50 этом на выходах дешифраторов 7 и 9, от,носяшихся к этому разряду, возникнут одинаковые состояния, которые поступят на один из алементов И: 10,11,12 и далеена алемент: ИЛИ3, сигнал от которого , осуществляет стирание корректируюшей информации по данному адресу, Таким образом накопитель 8 освобождается от случайной информации сбоев и в нем хранит; ся только информация об отказах. Если же после первого исправления информации от сбоя при вторичном обращении по этому . адресу возникает еше одна ошибка, то , блок 6 реагирует как и в случае многократной (двойной) ошибки и выдает сиг: йал об атом по шине 20,Итак, данное устройство дает возможность одновременно автоматически исправлять до двух ошибок в слове. В случае необходимости увеличения корректирующей способности устройства в него нужно вве сти несколько накопителей (типа накопителя 8) со своими дешифраторами, обеспе чив схемным путем поочередную запись корректируюшей информации в них от блока 6, а также необходимо построить соответствуюшую схему стирания случайной информации от сбоев,В случае применения предложенного устройства в составе оперативного запоминаюшего устройства приведенную на чертеже блок - схему необходимо дополнить соответствующими схемами записи; длина 7 900о 61 1.слов в блоке 6 должна быть увеличена кзодин разряд для хранения информации, за носимой при оперативной записи в испор, ченный разряд слова,5,Ф.ормула изобретенияЗапоминающее устройство с блокиров, кой неисправных запоминающих ячеек, со: держащее адресный олок, соединенный со накопителем, регистр, выходы которогоподключены к блоку кодирования, соедп ненному с дешифратором, элементы И и, что, с целью повышения надежности рабо ты устройства, оно содержит дополнительный дешифратор и дополнительный накопи, тель, адресные входы которогб подключе, ны ко входам адресного блока, информа 20ционные входы - к выходам блока кодиро; вания, а информационные выходы - ко входам дополнительного дешифратора, выходы; которого соединены со входами регистра,выходы дешифраторов соединены со входа 5, ми элементов И, выходы которых черезпервый элементИЛИ подключены к одному управляющему входу дополнительного, накопителя, информационные выходы кото рого через второй элемент ИЛИ соединены с одним входом дополнительного эле,мента И, другой вход которого подклю; чен к выходу блока кодирования, а выходсоединен с другим управляющим входом дополнительного .накопителя,, 507900 Составитель В, РудаковТехред О. Луговая Корректор Н. Зинзиков Рада%жр сон лиал ППП Патент", г. Ужгород, ул, Гагарина, 1 4705 Тираж 72ИИПИ Государственного комитета Советпо делаь изобретений и откр3.3.3035, Москва, Ж, Раушская н ПодписноеМинистровггийб., д. 4/5

СмотретьЗаявка

2053142, 13.08.1974

ПРЕДПРИЯТИЕ ПЯ А-7390

ТЕРЗЯН ОНИК АРТЕМОВИЧ, ЧАХОЯН ЛЕОНИД МИКАЕЛОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: блокировкой, запоминающее, запоминающих, неисправных, ячеек

Опубликовано: 25.03.1976

Код ссылки

<a href="https://patents.su/4-507900-zapominayushhee-ustrojjstvo-s-blokirovkojj-neispravnykh-zapominayushhikh-yacheek.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с блокировкой неисправных запоминающих ячеек</a>

Предыдущий патент: Логическое запоминающее устройство

Следующий патент: Электромагнитный привод

Случайный патент: Раствор для травления печатных плат