Устройство для преобразования чисел из кода системы остаточных классов в позиционный код с контролем ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

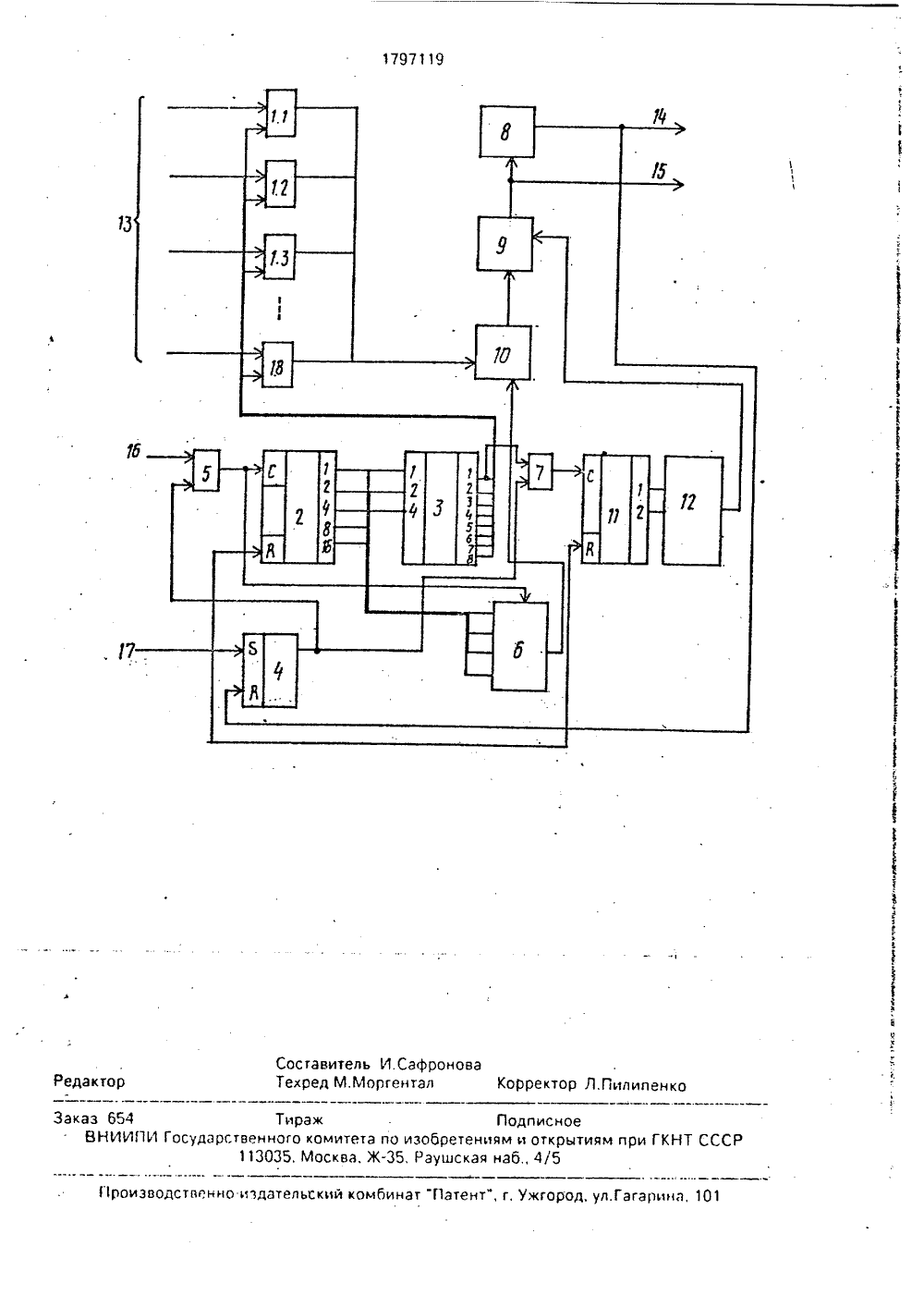

;, .:м. К АВТОР 4тк ОСТА- ННЫЙ вычислитель- использовано ункционирую- ССОВ С ПОЗИЦИ- я, а также для ляется увеличеащение аппарасвоеи работе обнаружения рмации, предчных классов контрольных пример, СОК ых основания,(1) (2) Рр = Р 1, Р 2. РЗ. Р 4, Р лный Рп = Рр.Р 7.Р Р 1 Р 2РЗ Р 4Число в СОК пред А = (а(, а 2.о. 4. 5.Рб,8, причемР 5 с Рбс Р 7 с Р 8ставится в виде.", ав. ат. ав) условия.в ПСС исгг 2 В 2+ГПООРЗ 4 ГОСУДАРСТВЕ ННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(56) Авторское свидетельство СССРМ 1238078, кл. 0 06 Е 11/08, 1984.Авторское свидетельство СССР3 Ф 1488968, кл, 6 06 Р 11/08, 1987,(54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОНИЯ ЧИСЕЛ ИЗ КОДА СИСТЕМЫТОЧНЫХ КЛАССОВ В ПОЗИЦИОКОД С КОНТРОЛЕМ ОШИБОК Изобретение относится к ной технике и может быть для сопряжения устройств, ф. щих в системе остаточных кла онными системами счислени контроля информации. Целью изобретения яв ние быстродействия и сокр турных затрат. Устройство использует в следующее. Известно, что для и исправления ошибок в инфо ставленной в системе остато(избыточных) оснований, На имеет б рабочих и 2 контрольн тогда рабочий диапазон(57) Изобретение относится к вычислительной технике и может быть использовано для сопряжения устройств, функционирующих в системе остаточных классов с позиционными системами счисления, а также для контроля информации, Цель изобретения - увеличение быстродействия и сокращение объема оборудования, Для этого изменяют алгоритм работы, сокращают объем блоков памяти, вводят первый и второй счетчики и образуют между ними блоки связи, что дает возможность увеличить быстродействие и сократить объем оборудования. 1 ил. Основываясь на методе проекций, есликодовое слово правильно, то все проекциичисла А будут равны самому числу, в случаеошибки по одному из оснований правильной будет лишь одна проекция по этому жеОснован и ю.В устройстве с целью увеличения быстродействия предлагается вычисление проекций по двум основаниям, но с учетом того,чтобы при исключении двух оснований диапазон представления проекции превышалбы рабочий диапазон, то есть РрР;(.Например, имеем те же восемь оснований Р 1.Р 2.РЗ.Р 4.Р 5,Рб,Р 7,Р 8, Рабочий диапазон Рр. Исключая два основанияР 1.2 - РЗ.Р 4.Р 5.Рб.Р 7.Р 8РрР 3.4- Р 1.Р 2.Р 5.Рб,Р 7,Р 8РрР 5.6 Р 1.Р 2.РЗ,Р 4.Р 7.Р 8РрР 7.8- Р 1.Р 2,РЗ.Р 4.Р 5.Р 6 = Рр,получаем выполнение указанногоДля перевода проекций числа р,пользуется выражение А- (а( В ( +Пример блоков памятиПервый блок памяти для и =8.Второй блокпамятиР 5,бРз,4Р еР 7,8 81 Вг Вз 840 О Вт 81 гВг 0 0 ВбгВгВтгВ зВ зВ."зВ зВ.з 81 Вг 81 81 В" Вл 0 ВцВбгВв0 аналогично для проекций по другим двум основаниям Р 1,2; Р 5.6: Р 7,8.После вычисления проекции по двум основаниям резуль 1 ат сравнивается с рабочим диапазоном Рр, При попадании результата в рабочий диапазон результат считается правильным и вычисления на этом заканчиваются. 8 случае выхода результата эа пределы диапазона Рр производится вычисление следующих проекций по двум основаниям до тех пор, пока результат не будет меньше или равен Рр. Если же такого не происходит, делается вывод о том, что ошибка произошла более чем по одному основанию и исправление ее невозможно.На чертеже представлена функциональная схема предлагаемого устройства,Устройство для преобразования чисел из кода СОК в позиционный код с контролем ошибок содержит группу блоков элементов И 1, первый счетчик 2, дешифратор 3. триггер 4, первый элемент И 5, первый блок памяти 6, второй элемент И 7. схему 8 сравнения с константой, сумматор 9 по модулю,блок умножения 10. второй счетчик 11, второй блок памяти 12, информационные входы устройства 13, выход 14 окончания преобразования, выход 15 результата устройства, тактовый вход 16, вход 17 запуска.Группа блоков элементов И 1 состоит из и блоков элементов И, где и - количество модулей СОК, блок состоит из ги элементов И, где ги =)о 9 гР , где Р; - основание СОК. Обьединение выходов блоков 1,1-1.8 элементов И выполняет функцию логического ИЛИ, Счетчики 2 и 11 - известные функциональные элементы, Коэффициент счета дервого счетчика должен быть Кч 1К 1, где М 1 = "и /2 - количество ячеек памяти первогогблока памяти. Коэффициент счета второго счетчика К,.2Иг, где юг = и/2 - количество ячеек памяти второго элемента памяти. Дешифратор 3 - известный функциональный элемент с числом выходов, равным и, а входов, соответственно )одгп, В качестве триггера 4 выбран ВЯ-триггер. Первый 6 и второй 12 блоки памяти представляют собой ПЗУ с информационной емкостью М 1 = =иг/2 хги и Мг = и/2 хМ соответственно. где М - разрядность представления модулей сумматора по модулю. Схема 8 сравнения с констан 1 ой пред.ставляет собой комбинационную схему. количество разрядов которой определяетсявеличиной Рр, Сумматор по модулю 9-накап 5 ливающего типа, количество разрядов соразмерно с величиной Рл. Блок умножения10 выполняет операцию арифметическогоумножения величин остатка по модулю отчисла а; на 81 - ортогональный базис.Устройство работает следующим образом.На вход 17 запуска подается импульс,который устанавливает триггер 4 в единичное состояние и одновременно устанавливает первый 2 и второй 11 счетчики внулевое состояние, Единичный уровень свыхода триггера 4 подается на вторые входыпервого 5 и второго 7 элементов И, что раз-решает прохождение тактовых импульсов с20 тактового входа 16 на счетный вход первогосчетчика 2,При поступлении первого тактового импульса на счетный вход первого счетчика 2на.его выходе формируется число 1 в двоичном коде, которое служит адресом для первого блока памяти, а также поступает навход дешифратора 3 и формирует "1" напервом его выходе, которая, проходя черезвторой элемент И 7, поступает на счетный30 вход второго счетчика 11 и формирует на еговыходах адрес первой ячейки для второгоблока памяти 12, с выхода которого на входзадания величины модуля поступает значение первого модуля и сумматор 9 готов суммировать по модулю Р 5 б. Единичный сигналс первого выхода поступает на блок 1,1 группы блоков элементов И 1 и тем самым пропускает на блок умножения 10 значениепервого остатка от числа А. Таким образом,на вхоцы блока умножения 10 поступаюта 1 и 81. С его выхода произведение поступает на сумматор 9 по модулю и записывается в его регистр, После этого с тактовоговхода 1 б второй импульс поступает на счетный вход первого счетчика 2, на выходе которого формируется число 2 в двоичномкоде, по:которому из первого блока памяти6 выдается следующее значение ортогонального базиса Вг и открывается блок 1.2группы блоков элементов И 1, На блок умножения 1 О поступят следующие операндыаг и Вг, а в регистр сумматора 9 запишетсясумма Й 1 81 + сг Вг и т,п, С приходом1восьмого тактового импульса с выхода сумматора 9 на вход схемы 8 сравнения с константой поступит проекция числа А помодУлЯм Р 5 и Рб. Если АРр, то на выходЕсхемы 8 сравнения с константой останетсянулевой уровень, который не изменит состо 1797119ячия триггера 4. Следующий тактовый импульс с входа 16 проидет на счетный вход первого счетчика 2, который сформирует ад, рес следующей ячейки блока памяти б, а гаккак к-входам дешифратора 3 подключены три выхода первого счетчика 2, соответствующие младшим разрядам, что соответствует коэффициенту счета КСЧ 1= 8, то нг первом выходе дешифратора опять будет единичный сигнал, который откроет блок 1.1 группы блоков элементов И 1 и одновременно поступит через второй элемент И 7 на счетный вход второго счетчика 11, на выходе . которого. будет сформирован адрес второго ;модуля для сумматора 9. Таким образом, на входы блока умножения 10 поступят а 1 и В 1, т;е, будет вычисляться вторая проекция2числа И, после вычисления которой производится сравнение с константой. Если АРр, то на выходе схемы 8 сравнения с константой появится единичный сигнал, который перекинет в нулевое состояние триггер 4, что закроет первый 5 и второй 8 элементы И, на выходе 15 результата устройства будет выдан правильный результат и преобразование числа А из СОК в ПСС закончится,.Ф о р мул а из обре те ни я Устройство для преобразования чисел из кода системы остаточных классов а пози, ционный код с контролем ошибок, содержащее группу блоков элементов И, блок умноженля, сумматор по модулю, первый блок памяти, схему сравнения с константой, триггер, первый элемент И, причем информационные входы устройства соединены с первыми входами соответствующих блоков элементов И, выходы которых соединены с входол первого сомножителя блока умножения, вход второго сомножителя которого соединен с выходом первого блока памяти, выход блока умножения соединен с входом 5 сумматора по лодулю, выход которого является выходом результага устройства и подключен к входу схемы сравнения с константой, выход которой является выходом окончания преобразования и подклю чен к входу сброса триггера, выход которогоподключен к первому входу первого элемента И, второй вход которого псдключен к тактовому входу устройства. единичный вход триггера подключен к входу запуска устрой ства, о т л и ч а ю щ е е с я тем, что, с цельюувеличения быстродействия и сокращения объема оборудования, устройство содержит первый и второй счетчики, дешифратор, второй блок памяти и второй элемент И, причем 20 выход первого элемента И подкл очен к входу разрешения чтения первого блока памяти и счетному входу первого счетчика, выходы которого соединены с адресными входами первого блока памяти и входами 25 дешифратора, выходы которого соединеныс вторыми входами соответствующих блоков элементов И, первый выход дешифратора подключен к первому входу второго, элемента И, к втвро,"лу входу которого под ключен выход триггера, выход второго элемента И подключен к счетному входу второго счетчика, выход которого подключен к адресным входам второго блока памяти, выход которого подключен к вхсду 35 задания величины модуля сумматора по модулю, вход запуска устройства подключен к входам сброса первого и второго счетчиков.1797119 едак орректор Л,Пилипе гкнт ссса оизводственно изда 654 НИИПИ ГСоставитель И.сафронТехред М.Моргентал Тираж Подписноственного комитета по изобретениям и откры 113035, Москва, Ж, Раушская наб 4/5 ий комбинат Патент", г, Ужгород, ул.Гагарина, 101

СмотретьЗаявка

4933833, 30.04.1991

СТАВРОПОЛЬСКОЕ ВЫСШЕЕ ВОЕННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ СВЯЗИ ИМ. 60-ЛЕТИЯ ВЕЛИКОГО ОКТЯБРЯ

ЧЕРВЯКОВ НИКОЛАЙ ИВАНОВИЧ, ОЛЕНЕВ АЛЕКСАНДР АНАТОЛЬЕВИЧ, БЕРЕЖНОЙ ВИКТОР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 11/08, H03M 7/18

Метки: классов, код, кода, контролем, остаточных, ошибок, позиционный, преобразования, системы, чисел

Опубликовано: 23.02.1993

Код ссылки

<a href="https://patents.su/4-1797119-ustrojjstvo-dlya-preobrazovaniya-chisel-iz-koda-sistemy-ostatochnykh-klassov-v-pozicionnyjj-kod-s-kontrolem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для преобразования чисел из кода системы остаточных классов в позиционный код с контролем ошибок</a>

Предыдущий патент: Многоканальный сигнатурный анализатор

Следующий патент: Устройство для контроля дешифраторов

Случайный патент: 277474