Генератор псевдослучайных последовательностей

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

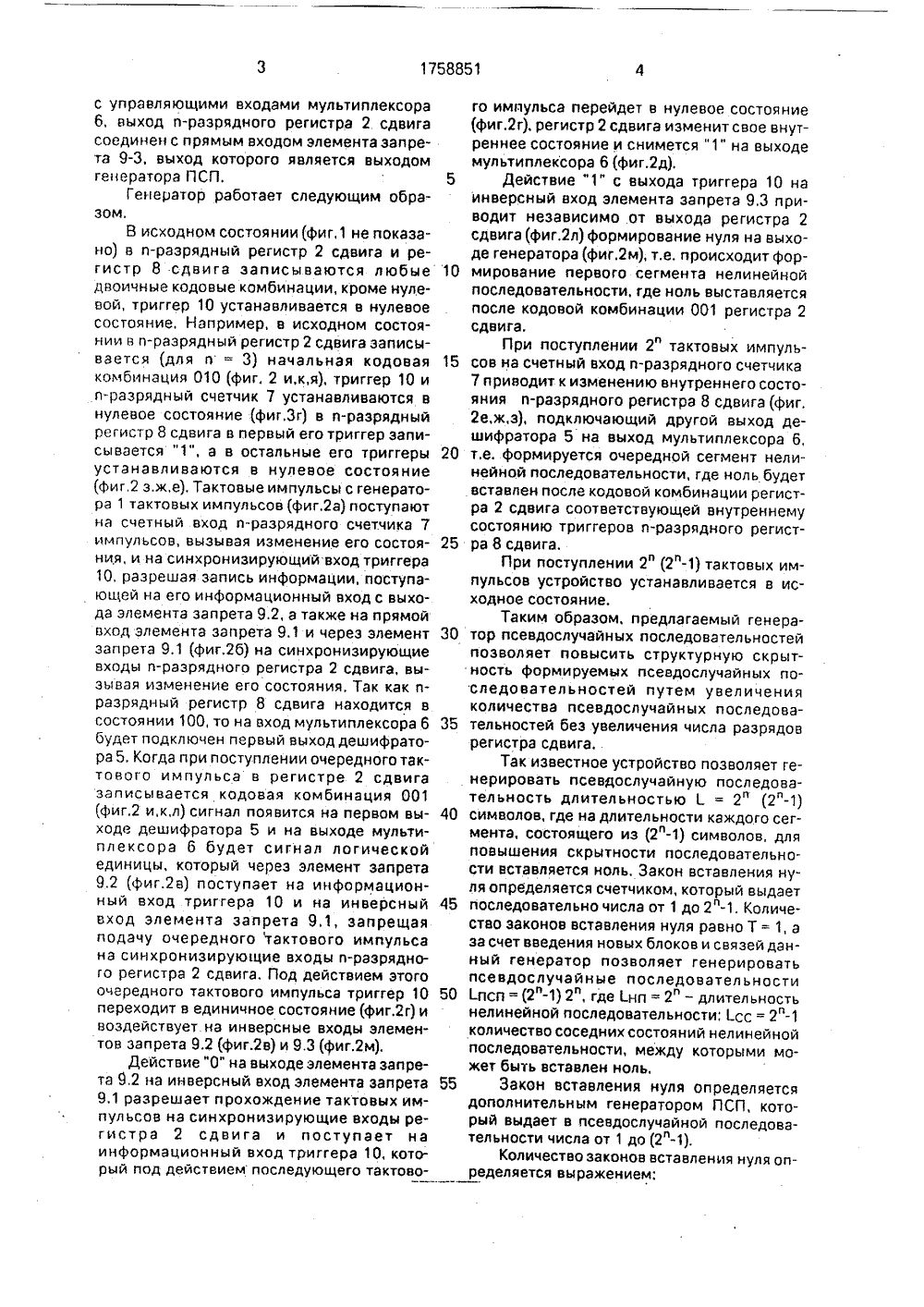

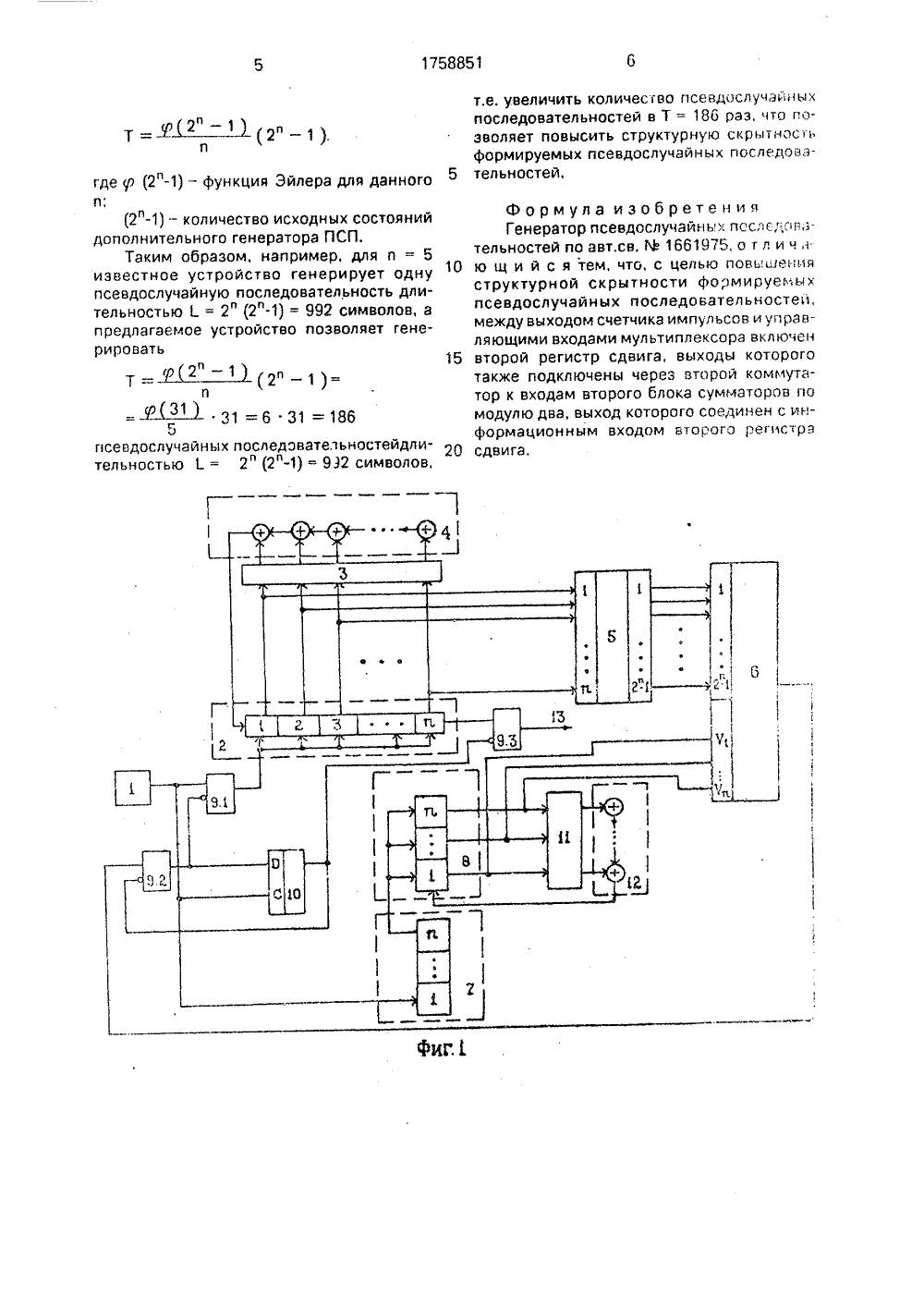

(5)5 Х ПОзова но ой техГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ПИСАНИЕ ИЗОБ АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторское свидетельство СССРМ 1661975, кл, Н 03 К 3/84, 1989.(54) ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЬСЛ ЕДО ВАТЕЛЬ НОСТЕЙ(57) Изобретение может быть испольв связи, радиолокации,вычислительннике и является дополнительным кант Изобретение относится к импульсной технике и может быть использовано в связи, радиолокации и вычислительной технике.Цель изобретения - повышение структурной скрытности формируемых псевдослучайных последовательностей путем увеличения количества псевдослучайных последовательностей.На фиг. 1 приведена структурная схема генератора псевдослучайных последовательностей; на фиг. 2 - эпюры напряжений на выходе соответствующих блоков для данного генератора, поясняющие принцип работы устройства,Генератор псевдослучайных последовательностей (фиг,1) содержит генератор 1 тактовых импульсов, и-разрядный регистр 2 сдвига, коммутатор 3, блок сумматора 4 по модулю дна, дешифратор 5, мультиплексор б, и-разрядный счетчик 7 импульсов, регистр 8 сдвига, три элемента запрета 9.1, 9.2, 9,3, триггер 10, коммутатор 11, блок сумматоров 12 по модулю два, выход элемента запрета 9.3 является выходом генератора 1661975, Генератор псевдослучайных последовательностей содержит 1 генератор тактовых импульсов, 2 регистра сдвига, 2 коммутатора, 1 дешифратор, 1 мультиплексор, 1 счетчик импульсов, 1 триггер, 3 элемента запрета, 2 блока сумматоров по модулю дна. За счет введения регистра, коммутатора и блока сумматоров в устройстве повышается структурная скрытность формируемых псевдослучайных последовательностей путем увеличения количества псевдослучайных последовательностей. 2 ил,ПСП, причем в генераторе псевдослучайных последовательностей последовательно соединены и-разрядный регистр 2 сдвига, в цепи обратной связи которого включены коммутатор 3 и блок сумматоров 4 по модулю два, вход синхронизации и-разрядный счетчика 7 соединен с выходом генератора 1 тактовых импульсов, последовательно соединены дешифоатор 5, мультиплексор б, выход которого соединен с прямым входом второго элемента запрета 9-2, выход кото- рога подключен к входу триггера 10 и к инверсному входу первого элемента запрета 9-1, выход генератора 1 соединен с прямым входом элемента запрета 9-1, выход которого соединен с входом регистра 2 сдвига и с счетным входом триггера 10, выход которого соединен с инверсными входами элементов запрета 9-2, 9-3 последовательно соединенные регистр 8 сдвига, в цепи обратной связи которого включены коммутатор 11 и блок сумматоров 12 па модулю два, вход регистра 8 сдвига соединен с выходом и-разрядного счетчика 7 импульсон, а выход30 35 40 45 50 с управляющими входами мультиплексора б, выход и-разрядного регистра 2 сдвига соединен с прямым входом элемента запрета 9-3, выход которого является выходом генератора ПСП.Генератор работает следующим образом,В исходном состоянии (фиг,1 не показано) в и-разрядный регистр 2 сдвига и регистр 8 сдвига записываются любые двоичные кодовые комбинации, кроме нулевой, триггер 10 устанавливается в нулевое состояние, Например, в исходном состоянии в и-разрядный регистр 2 сдвига записывается (для и = 3) начальная кодовая комбинация 010 (фиг. 2 и,к,я), триггер 10 и и-разрядный счетчик 7 устанавливаются в нулевое состояние (фиг,Зг) в и-разрядный регистр 8 сдвига в первый его триггер записывается "1", а в остальные его триггеры устанавливаются в нулевое состояние (фиг,2 э.ж,е). Тактовые импульсы с генератора 1 тактовых импульсов (фиг,2 а) поступают на счетный вход и-разрядного счетчика 7 импульсов, вызывая изменение его состояния, и на синхронизирующий вход триггера 10, разрешая запись информации. поступающей на его информационный вход с выхода элемента запрета 9.2, а также на прямой вход элемента запрета 9.1 и через элемент запрета 9.1 (фиг,2 б) на синхронизирующие входы и-разрядного регистра 2 сдвига, вызывая изменение его состояния. Так как иразрядный регистр 8 сдвига находится в состоянии 100, то на вход мультиплексора 6 будет подключен первый выходдешифратора 5, Когда при поступлении очередного тактового импульса в регистре 2 сдвига записывается кодовая комбинация 001 (фиг.2 и,к,л) сигнал появится на первом выходе дешифратора 5 и на выходе мультиплексора б будет сигнал логической единицы, который через элемент запрета 9,2 (фиг.2 в) поступает на информационный вход триггера 10 и на инверсный вход элемента запрета 9.1, запрещая подачу очередного тактового импульса на синхронизирующие входы п-разрядного регистра 2 сдвига. Под действием этого очередного тактового импульса триггер 10 переходит в единичное состояние (фиг,2 г) и воздействует на инверсные входы элементов запрета 9.2 (фиг.2 в) и 9.3 (фиг.2 м).Действие "0" на выходе элемента запрета 9,2 на инверсный вход элемента запрета 9.1 разрешает прохождение тактовых импульсов на синхронизирующие входы регистра 2 сдвига и поступает на информационный вход триггера 10, который под действием последующего тактово 5 10 15 20 25 го импульса перейдет в нулевое состояние(фиг.2 г), регистр 2 сдвига изменит свое внутреннее состояние и снимется "1" на выходемультиплексора 6 (фиг,2 д),Действие "1" с выхода триггера 10 наинверсный вход элемента запрета 9,3 приводит независимо от выхода регистра 2сдвига (фиг.2 л) формирование нуля на выходе генератора (фиг.2 м), т.е. происходит формирование первого сегмента нелинейнойпоследовательности, где ноль выставляетсяпосле кодовой комбинации 001 регистра 2сдвига.При поступлении 2" тактовых импульсов на счетный вход п-разрядного счетчика7 приводит к изменению внутреннего состояния и-разрядного регистра 8 сдвига (фиг.2 е,ж,з), подключающий другой выход дешифратора 5 на выход мультиплексора б,т.е. формируется очередной сегмент нелинейной последовательности, где ноль будетвставлен после кодовой комбинации регистра 2 сдвига соответствующей внутреннемусостоянию триггеров и-разрядного регистра 8 сдвига,При поступлении 2" (2"-1) тактовых импульсов устройство устанавливается в исходное состояние.Таким образом, предлагаемый генератор псевдослучайных последовательностейпозволяет повысить структурную скрытность формируемых псевдослучайных последовательностей путем увеличенияколичества псевдослучайных последовательностей без увеличения числа разрядоврегистра сдвига.Так известное устройство позволяет генерировать псевдослучайную последовательность длительностью= 2" (2"-1)символов, где на длительности каждого сегмента, состоящего из (2"-1) символов, дляповышения скрытности последовательности вставляется ноль. Закон вставления нуля определяется счетчиком, который выдаетпоследовательно числа от 1 до 2"-1, Количество законов вставления нуля равно Т = 1, аза счет введения новых блоков и связей данный генератор позволяет генерироватьпсевдослучайные последовательностипсп = (2"-1) 2", где .нп = 2" - длительностьнелинейной последовательности; Есс = 2"-1количество соседних состояний нелинейнойпоследовательности, между которыми может быть вставлен ноль.Закон вставления нуля определяетсядополнительным генератором ПСП, который выдает в псевдослучайной последовательности числа от 1 до (2"-1).Количество законов вставления нуля определяется выражением:, Лукач Заказ 3011ВНИИПИ Го Тираж Подписноетвенного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раувская наб 4/5

СмотретьЗаявка

4874322, 10.08.1990

РОСТОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК

ШЕВЧУК ПЕТР СЕРГЕЕВИЧ, ТОЛУБКО ВЛАДИМИР БОРИСОВИЧ, КАЗАК ЮРИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H03K 3/84

Метки: генератор, последовательностей, псевдослучайных«

Опубликовано: 30.08.1992

Код ссылки

<a href="https://patents.su/4-1758851-generator-psevdosluchajjnykh-posledovatelnostejj.html" target="_blank" rel="follow" title="База патентов СССР">Генератор псевдослучайных последовательностей</a>

Предыдущий патент: Генератор случайных чисел

Следующий патент: Формирователь высоковольтных импульсов специальной формы

Случайный патент: Способ получения заготовок спеченных быстрорежущих сталей