Дельта-кодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

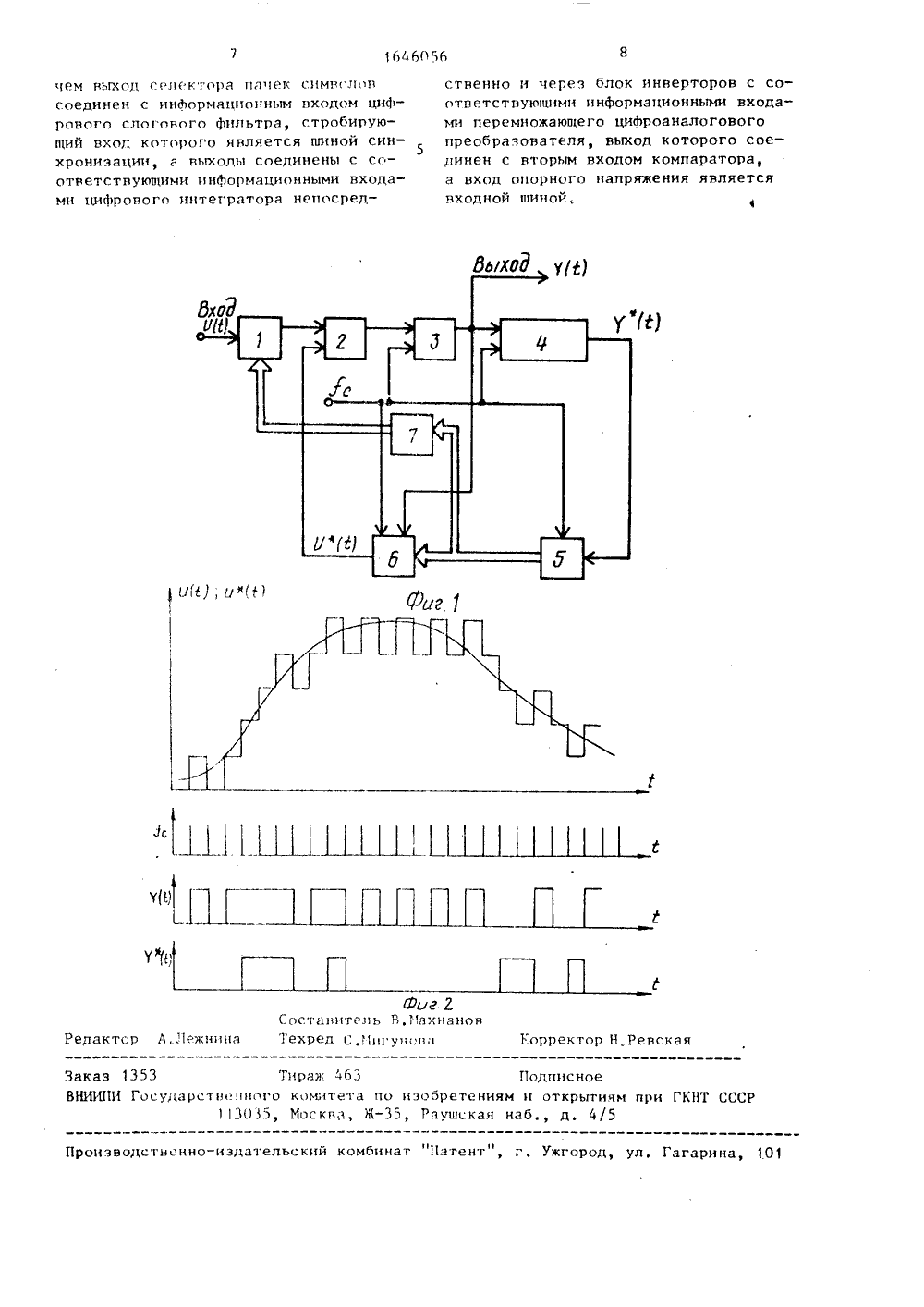

Дельта-кодер работает следующим образом.Входной аналоговый сигнал У поступает на вход опорного напряжения перемножающего ЦАП 1 и появляется на его выходе, ослабленный в К раз. Коэффициент ослабления К определяется двоичной кодовой комбинацией на информационных входах перемножающего ПАП 1: 45 50 Бьь А,ьАМех 2 ф ф где г - разрядность перемножающегоПАП 1;А - кодовая комбинация на инфорАьмационных входах перемножающего ЦАП 1, представленная руются в случае наличия в дельта-модулированном (ДИ) потоке двух и более элементных пачек (следующих подряд однотипных символов), Информационным и стробирующим входами селектора пачек являются информационный истробирующий входы регистра сдвигасоответственно,В качестве цифрового слоговогофильтра, в частности, может быть использован цифровой ДМ-Фильтр Аппаратурно данный Фильтр может быть реализован множеством способов, например на регистре сдвига, наборе буФерных регистров с параллельной записью и сумматоре, причем на информационный вход Фильтра поступает цифровой ДМ-поток, который с приходом тактовых импульсов на стробирующий входрегистра заполняет его разряды. Каждый бит ДМ-потока поступает на одиниз информационных входов соответствующего буФерного регистра, все остальные входы которого заземлены. Испольэование тех или иных входов буферныхрегистров зависит от конкретных требований к характеристикам цифровогослогового Фильтра, ХарактеристикиФильтра, в свою очередь, определяются конкретными условиями применениядельта-кодера, а также типом и параметрами входного сигнала.Появление логических единиц в разрядах регистра сдвига вызывает Форми- Зрование заданных двоичных чисел на выходах соответствующих буферных регистров, Просуммироваввись сумматором,эти числа. Формируют отклик цифровогофильтра на входное воздействие, 40 в десятичной системе счисления,Если предположить, что в моментначала работы двоичная кодовая комбинация на выходе цифрового слоговогоФильтра 5 соответствует числу 0 в десятичной системе счисления (комбинация 000000), то проинвертированная блоком 1 инверторов комбинация(111111) на информационных входахперемножающего 1 АП 1 соответствуетгчислу 2 -1 в десятичной системе счисления, а следовательно, входной сигнал Б(С) коммутируется на выход перемножающего ЦАП с максимальным коэфФициентом передачиЭтот сигнал поступает на вход компаратора 2, где сравнивается с аппроксимирующим сигналом У(1), присутствующим на другом входе компаратора 2,В случае, если У(С) ) У (1), на выходе компаратора 2 Формируется логический ноль, При Б(С) ( У (1) компаратор2 выдает логическую единицу, Двухуровневый сигнал с выхода компаратора 2 поступает на инФормационный входтриггера 3, на стробирующий вход которого подаются тактовые импульсы сшины синхронизации. С приходом каждого тактового импульса логический потенциал, присутствующий на информационном входе триггера Э, записываетсяв него, появляется на его выходе иподдерживается там как минимум доприхода следующего импульса тактовойпоследовательности, Таким образом,Формируются биты выходного ДИ-сигнала, каждый иэ которых поступает навыход устройства, а также одновременно на информационный вход селектора4 пачек символов и на управляющийвход цифрового интегратора 6, С приходом очередных тактовых импульсовФрагмент циФрового ДМ-потока последовательно записывается в селектор4 пачек символов и анализируется последним на предмет наличия двух иболее элементных пачек. Принцип Формирования выходного сигнала селектора 4 пачек символов при использовании в нем двухразрядного (для наглядности) регистра сдвига иллюстрируется временными диаграммами наФиг, 2,Сигнал 7 (С) с выхода селектораМ4 пачек символов (Фиг, 1) поступаетна информационный вход цифровогослогового фильтра 5, усредняется им6056 6 40 45 50 55 5 164и поступает в ниде кодовой комбинации, пропорциональной средней плотности цифрового сигнала Уф(Т), наинформационные входы цифрового интегратора 6.Подача на управляющий вход цифрового интегратора битов цифрового ДМсигнала уИ) (с одновременной подачей тактовых импульсов по его стробирующему входу) приводит к тому, чтовеличина аппроксимирующего напряжения(й) на выходе цифрового интегратора 6 изменяется (либо увеличивается, либо уменьшается) в каждом такте работы устройства на величину,пропорциональную двоичной кодовойкомбинации, присутствующей в моментприхода тактового импульса на информационных входах интегратора 6, причем, если текущий бит ДМ-потока соответствует логическому нулю, происходит уменьшение аппроксимирующегонапряжения Б (1), в случае же, еслитекущий бит У(1)="1", происходитувеличение напряжения Б (Т).Очевидно, что реализованная такимобразом обратная связь приводит ктому (фиг, 2), что аппроксимирующеенапряжение Г(С) всегда будет изменяться таким образом, чтобы уменьшить разность(1)-(С), т,е, напряжение Б+ будет аппроксимироватьвходной сигнал 1.Для улучшения качества преобразования (уменьшения разности между(й) и Б(й) и расширения динамического диапазона) в устройство введенаадаптация параметров (компандирование),Известно, что двух-, трех- и болееэлементные пачки формируются в цифровом ДИ-сигнале тогда, когда аппроксимирующее напряжение Б (1) на протяжении двух, трех и более тактов не может"догнать" быстроизменяющийся входнойсигнал 1(С), Иаличие в ДИ-сигналеУ(с) большого числа таких фрагментов(многоэлементных пачек) на протяжениидлительного времени свидетельствуето необходимости изменения соотношенияамплитуды (уровня) входного сигналакомпаратора 2 и величины шага квантования,Это соотношение может быть изменено двумя способами; путем воздействия на величину шага квантования и путем регулирования уровня входного сигнала компаратора 2 (сигнала, поступающего 5 10 15 20 25 30 35 на его первый вход). В устройстве используются обе возможности такого регулирования, которое производитсяследующим образом. Кодовая комбинацияс выхода цифрового слогового фильтра5, величина которой пропорциональнасредней плотности цифрового, РМ-потока(следовательно, амплитуде и частотевходного сигнала У(С), поступает наинформационные входы цифрового интегратора 6, а также проинвертированнаяблоком 7 инверторов на информационныенходы перемножающего ЦАЛ 1, При такомвключении величина шага квантования,с которым цифровой интегратор 6 производит аппроксимацию входного сигнала, прямо пропорциональна уровню ичастоте входного сигнала, а коэдФициент передачи перемножающего ЦАП 1(по входу опорного напряжения) обратно пропорционален этим величинам, Врезультате в устройстве производитсявысокоэффективное компандирование,которое приводит к расширению динамического диапазона преобразуемогосигнала, Любое увеличение крутизнывходного сигнала (й) приводит кувеличению двоичной кодовой комбинации на выходе цифрового слоговогофильтра 5, а следовательно, к увеличению шага аппроксимирующего напряжения(1), уменьшению уроння сигнала на входе компаратора 2 и стабилизации отношения сигнал/шум квантования, что эквиналентно расширениюдинамического диапазона преобразуемых сигналов,Формула изобретения Дельта-кодер, содержащий компаратор, выход которого подключен к информационному входу триггера, выход которого является выходной шиной и соединен с информационным входом селектора пачек символов и управляющим входом цифрового интегратора, выход которого подключен к первому входу компаратора, а стробирующий вход объединен со стробирующими входами триггера и селектора пачек символов и является шиной синхронизации, о тл и ч а ю щ и й с я тем, что, с целью расширения динамического диапазона преобразуемых сигналов, в него введены цифровой слоговый Фильтр, блок инверторов и перемножающий цифроаналоговый преобразователь, при,В Фиг 2 С оставит с л ь Б,11 ах пан Техред С,11 игупица1 ежнина корректор Н.Ревска едакто раж 463 Подписноомитета по изобретениям и открыт Москв, И, Раушская наб д, 4 акаэ 1353 НИИПИ Государствепнл 113035НТ ССС ям яздательский комбинат "Патент", г. Ужгород, ул, Гагари О иэводстнен чем выход с лектора пачек символовсоединен с информационным входом цифрового слогового фильтра, стробирующий вход которого является шиной синхронизации, а выходы соединены с соответствующими информационными входами цифрового интегратора непосредственно и через блок инверторов с соответствующими информационными входами перемножающего цифроаналоговогопреобразователя, выход которого соединен с вторым входом компаратора,а вход опорного напряжения являетсявходной шиной,

СмотретьЗаявка

4462125, 18.07.1988

РИЖСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. А. Я. ПЕЛЬШЕ

КОТОВИЧ ГЛЕБ НИКОЛАЕВИЧ, ПУНДУРС АРМАНД АНТОНОВИЧ, КОМАРОВ КОНСТАНТИН СЕРГЕЕВИЧ, ХОФМАРКС ВАЛДИС ВОЛДЕМАРОВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-кодер

Опубликовано: 30.04.1991

Код ссылки

<a href="https://patents.su/4-1646056-delta-koder.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-кодер</a>

Предыдущий патент: Преобразователь перемещения в код

Следующий патент: Преобразователь двоично-десятичного кода в двоичный редчина

Случайный патент: Резец