Устройство для обнаружения ошибок в дискретной последовательности

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1589281

Авторы: Анненков, Ахтариев, Керчин, Сарсенбаев

Текст

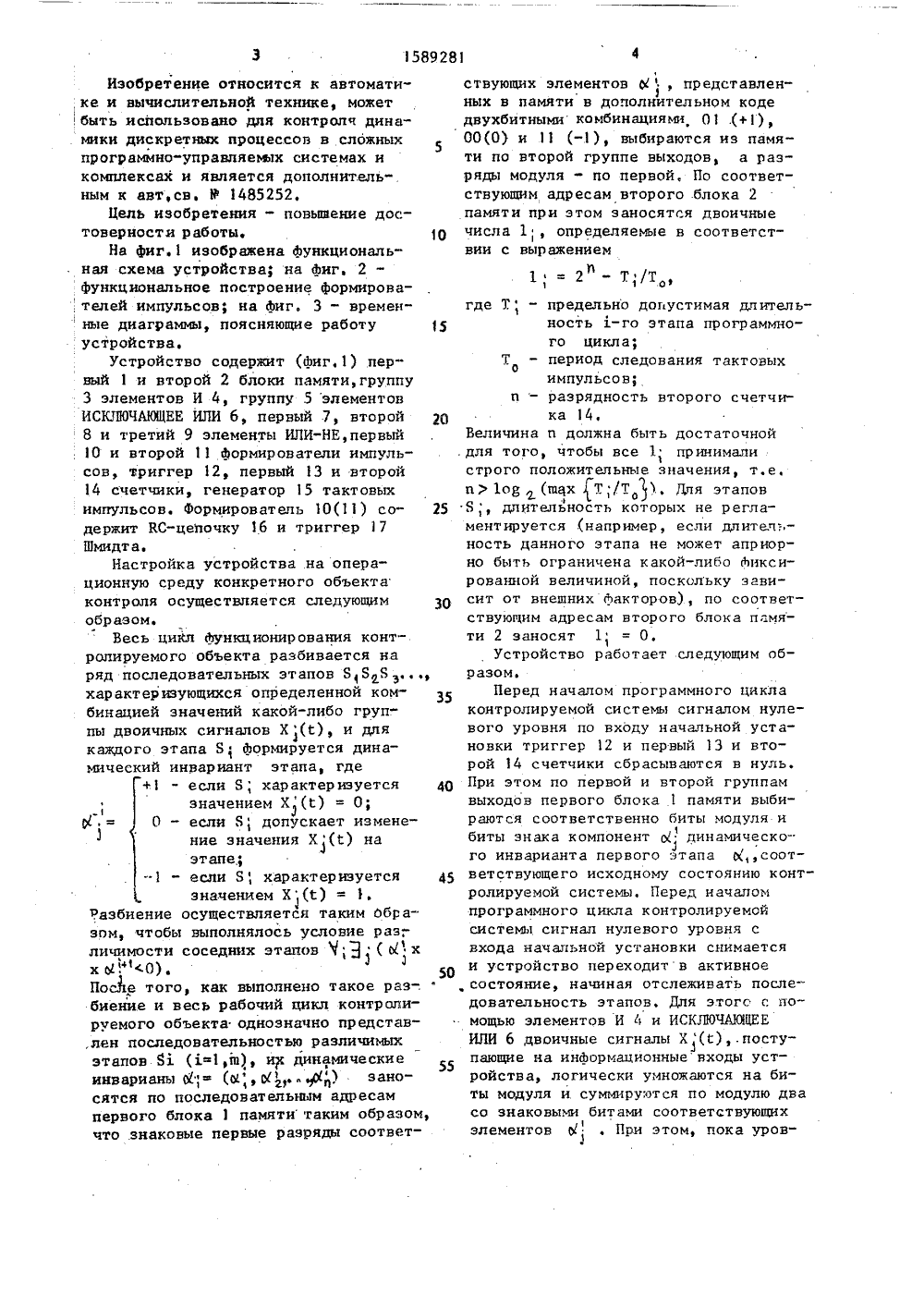

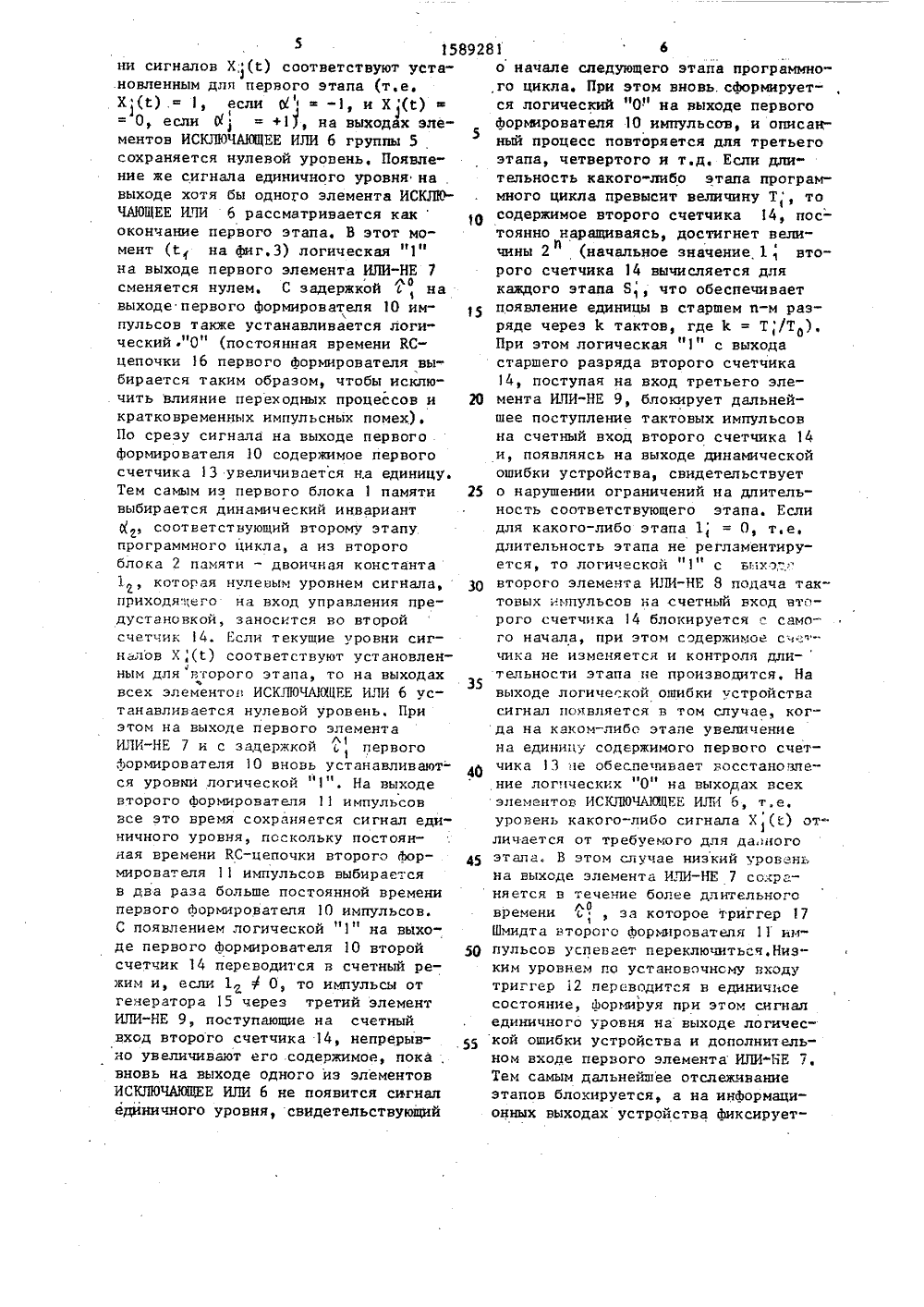

) 56) Авторское свид 1485252, кл, С 06 54) УСТРОЙСТВО ДЛЯ ШИБОК В ДИСКРЕТНОЙ ельство СССР1/28, 1988 БНАРУЖЕНИЯ ОСЛЕА 1 ОВАТЕЛЬ О ТИ(57) Изобретениетике и вычислителбыть использованнамики дискретныных программно-у вт носится ьной технике, можетдля контроля дисл х процесс правляемы л. стемах ГОСУДАРСТВЕННЫЙ КОМИТЕТ О ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯ РИ ГКНТ СССР и комплексах и является дополнительным к авт,св. Р 1485252, Цельюизобретения является повышение достоверности. Устройство содержит первый 1 и второй 2 блоки памяти, группу3 элементов И 4, группу 5 элементовИСКЛОЧАЮЩЕЕ ИЛИ 6, первый 7, второй8 и третий 9 элементы ИЛИ-НЕ, первый10 и второй 11 формирователи импульсов, триггер 12, первый 13 и второй14 счетчики и тактовый генератор 15.Ус.ройство отслеживает послЕдовател.ность этапов программного цикла контролируемого объекта, сигнапизируяо логической ошибке, если наблюдаемая последовательность этапов отличается от программно обусловленной, ио динамической ошибке, если нарушены ограничения на длительность эта15Изобретение относится к автоматике и вычислительной технике, может быть использовано для контроля динамики дискретных процессов в сложных программно-управляемых системах и комплексах и является дополнительным к авт,св. У 1485252.Цель изобретения - повьшение достоверности работы.На фиг.1 изображена функциональная схема устройства; на фиг. 2 - функциональное построение формирователей импульсов; на фиг. 3 " времен ные диаграммы, поясняющие работу устройства,Устройство содержит (фиг.1) первыйи второй 2 блоки памяти, группу 3 элементов И 4, группу 5 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6, первый 7, второй 8 и третий 9 элементы ИЛИ-НЕ,первьп 10 и второй 11 формирователи импульсов, триггер 12, первый 13 и второй 14 счетчики, генератор 5 тактовых импульсов. Формирователь 10(11) содержит КС-цепочку 16 и триггер 17 Шмидта.Настройка устройства на операционную среду конкретного объекта контроля осуществляется следующим образом.Весь цикл дункционирования контролируемого объекта разбивается на ряд последовательных этапов БББ характеризующихся определенной комбинацией значений какой-либо группы двоичных сигналов Х (С), и для каждого этапа Б формируется динамический инвариант этапа, где.О - если Б; допускает изменение значения ХР) наэтапе;-1 - если Б, характеризуетсязначением Х(й) азбиение осуществляется таким образом, чтобы выполнялось условие раз-, личимости соседних этапов М;- ( ьх х ьфО).Пос 3 е того, как выполнено такое раз-. биение и весь рабочий цикл контролируемого объекта однозначно представ,лен последовательностью различимых этапов Б 3. (д=1,а), их динамические инварианы М, (Ю 0 ,э.,ф) заносятся по последователыпм адресам первого блока 1 памяти таким образом что знаковые первые разряды соответ 89281 ствующих элементов МпредставленФ уных в памяти в дополнительном коде двухбитными комбинациями О 1,(+1), 00(0) и 11 (-1), выбираются из памяти по второй группе выходов, а разряды модуля " по первой, По соответствующим адресам второго .блока 2 памяти при этом заносятся двоичные числа 1 определяемые в соответствии с выражением1 =2 -Т/Тио 10 20 состояние, начиная отслеживать последовательность этапов. Для этогс с помощью элементов И 4 и ИСКЛЮЧАЮЩЕЕИЛИ 6 двоичные сигналы Х (Е),.поступающие на информационныевходы устройства, логически умножаются на биты модуля и суммируются по модулю двасо знаковыми битами соответствующихэлементов Ы . При этом, пока уров 55 где Т , - предельно допустимая длитель 15 ность 1-го этапа программного цикла;Т - период следования тактовыхоимпульсовэи - разрядность второго счетчика 14.Величина п должна быть достаточной. для того, чтобы все 1 принималистрого положительные значения, т.е,о) 1 о Э(пцхт;/т ) Лпп этэпоп25 Б;, длительность которых не регламентируется (например если длитеч;-, -ность данного этапа не может априорно быть ограничена какой-либо Аксированной величиной, поскольку зависит от внешних факторов), ио соответствующим адресам второго блока памя- ти 2 заносят 1 = О,Устройство работает следующим образом.Перед началом программного циклаконтролируемой системы сигналом нулевого уровня ло входу начальной установки триггер 12 и первый 13 и второй 14 счетчики сбрасываются в нуль,40 При этом по первой и второй группамвыходов первого блока 1 памяти выбираются соответственно биты модуля ибиты знака компонент с динамического инварианта первого этапа Ксоответствующего исходному состоянию контролируемой системы, Перед началомпрограммного цикла контролируемойсистемы сигнал нулевого уровня свхода начальной установки снимается50 и устройство переходитв активное89281 6 5 15 ни сигналов Х (С) соответствуют уста.новленным для первого этапа (т,е. Х; = 1, если М-1, и Х (С) = О, если 0 = +1, на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ б группы 5 сохраняется нулевой уровень. Появление же сигнала единичного уровня на . выходе хотя бы одного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ б рассматривается какокончание первого этапа. В этот момент ( на фиг.З) логическая "1" на выходе первого элемента ИЛИ"НЕ 7 сменяется нулем, С задержкой с, нало выходе первого формирователя 10 импульсов также устанавливается логический .0 (постоянная времени КС- цепочки 16 первого формирователя выбир ает ся т аким образом, чтобы исключить влияние переходных процессов и кратковременных импульсных помех), По срезу сигнала на выходе первого формирователя 10 содержимое первого счетчика 13 увеличивается на единицу. Тем самым из первого блока 1 памяти выбирается динамический инвариантсоответствующий второму этапу программного цикла, а из второго блока 2 памяти - двоичная константа 1, которая нулевым уровнем сигнала, приходя цегс иа вход управления предустановкой, заносится вс второй счетчик 14. Если текущие уровни сигналов Х,(1) соответствуют установленным для "второго этапа, то на выходаховсех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ б устанавливается нулевой уровень. При этом на выходе первого элемента ИЛИ-НЕ 7 и с задержкой ь первогол формирователя 10 вновь устанавливаются уровии логической "1". На выходе второго формирователя 11 импульсов все это время сохраняется сигнал единичного уровня, поскольку постоянная времени ЕС-цепочки второго формирователя 11 импульсов выбирается в два раза больше постоянной времени первого формирователя 10 импульсов. С появлением логической "1" на выходе первого формирователя 10 второй счетчик 14 переводится и счетный режим и, если 1 4 О, то импульсы от генератора 15 через третий элемент ИЛИ-НЕ 9, поступающие на счетный вход второго счетчика 14, непрерывно увеличивают его содержимое, пока вновь на выходе одного из элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6 не появится сигнал едйничного уровня, свидетельствующий 5 10 15 20 25 30 35 40 45 50 о начале следующего этапа программного цикла. При этом вновь. сформируется логический "О" иа выходе первого формирователя 10 импульсов, и описанный процесс повторяется для третьего этапа, четвертого и т.д. Если длительность какого-либо этапа программного цикла превысит величину Т;, то содержимое второго счетчика 14, пос- тоянно наращиваясь достигнет велииФчины 2 (начальное значение 1второго счетчика 14 вычисляется для каждого этапа Я что обеспечивает появление единицы в старшем и-м разряде через Е тактов, где К = Т,/Т). При этом логическая "1" с выхода старшего разряда второго счетчика 14, поступая на вход третьего элемента ИЛИ-НЕ 9, блокирует дальнейшее поступление тактовых импульсов на счетный вход второго счетчика 14 и, появляясь на выходе динамической ошибки устройства, свидетельствует о нарушении ограничений на длительность соответствующего этапа. Если для какого-либо этапа 1; = О, т,е, длительность этапа не регламентируется, то логической "1" с вцх,".второго элемента ИЛИ-НЕ 8 подача тактовых импульсов на счетный вход втс - рого счетчика 14 блокируется с самого начала, при этом содержимое сч чика не изменяется и контроля длительности этапа не прсизвоцится. На выходе логической ошибки устройства сигнал появляется в том случае, когда на каком-либо этапе увеличение на единицу содержимого первого счетчика 13 ие обеспечивает восстановление логических "0" на выходах всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6, т.е, уровень какого-либо сигнала Х (;) от"1 личается ст требуемого для дансгс этапа. В этом случае низкий уровень на выходе элемента ИЛИ-НЕ 7 сохраняется в течение более длительного времени ь , за которое триггер 17лоШмидта второго формирователя 11 импульсов успевает переключитьсч.Низким уровнем пс установочному входу триггер 12 переводится в единичное состояние, формируя при этом сигнал единичного уровня на выходе логическои ошибки устроиства и дополнительном входе первого элемента ИЛИ-НЕ 7.Тем самым дальнейшее отслежчваниеэтапов блокируется, а на информационных выходах устройства фиксирует"1589281 ся номер этапа, на котором обнаружена ошибка. О Вмх1 О фи. 3оставитель И.Сафроноваехред А.Кравчук едактор И,Келемеш ерявая орректор Заказ 2542 Тираж 5 б 9 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ С 113035, Москва, Ж, Раушская наб., д. 4/5 агарина, 101 дственно-издательский комбинат "Патент", г, Ужгород,П Формула изобретенияУстройство для обнаружения ошибок в дискретной последовательности по авт,св. 9 1485252, о т й и ч а ю" ш е е с я тем, что, с целью повышения достоверности работь 1 устройства, в него ввеДены второй блок памяти, второй счетчик два элемента ИЛИ-НЕ, генератор тактовых импульсов, . причем группа адресных входов второго блока памяти подключена к группе выходов первого счетчика, группа выходов второго блока памяти соеди,нена с группой входов второго элемента ИЛИ-НЕ и группой установочныхвходов второго счетчика, вход резрешения установки и счетный вход которого соединены соответственно с вь 1 ходом первого формирователя, импульсов и выходом третьего элементаИЛИ-НЕ, первый, второй и третий входы которого подключены соответственно к выходу генератора тактовых импульсов, выходу второго элементаИЛИ-НЕ и выходу старшего разрядавторого счетчика, вход начальной установки второго счетчика подключенк установочному входу устройства,.выход старшего разряда второго счетчика является вторым выходом ошибкиустройства.

СмотретьЗаявка

4492750, 10.10.1988

УФИМСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ ИМ. СЕРГО ОРДЖОНИКИДЗЕ

КЕРЧИН ВИКТОР НИКОЛАЕВИЧ, САРСЕНБАЕВ ВАЛЕРИЙ ШАУХАРОВИЧ, АННЕНКОВ ВЛАДИМИР НИКОЛАЕВИЧ, АХТАРИЕВ АЗАТ АГЛУЛОВИЧ

МПК / Метки

МПК: G06F 11/28

Метки: дискретной, обнаружения, ошибок, последовательности

Опубликовано: 30.08.1990

Код ссылки

<a href="https://patents.su/4-1589281-ustrojjstvo-dlya-obnaruzheniya-oshibok-v-diskretnojj-posledovatelnosti.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения ошибок в дискретной последовательности</a>

Предыдущий патент: Устройство для контроля цифровых блоков

Следующий патент: Контроллер памяти

Случайный патент: Центробежный растиратель-смеситель непрерывного действия для приготовления силикатных и другихсмесей