Оперативное запоминающее устройство с резервированием строк

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

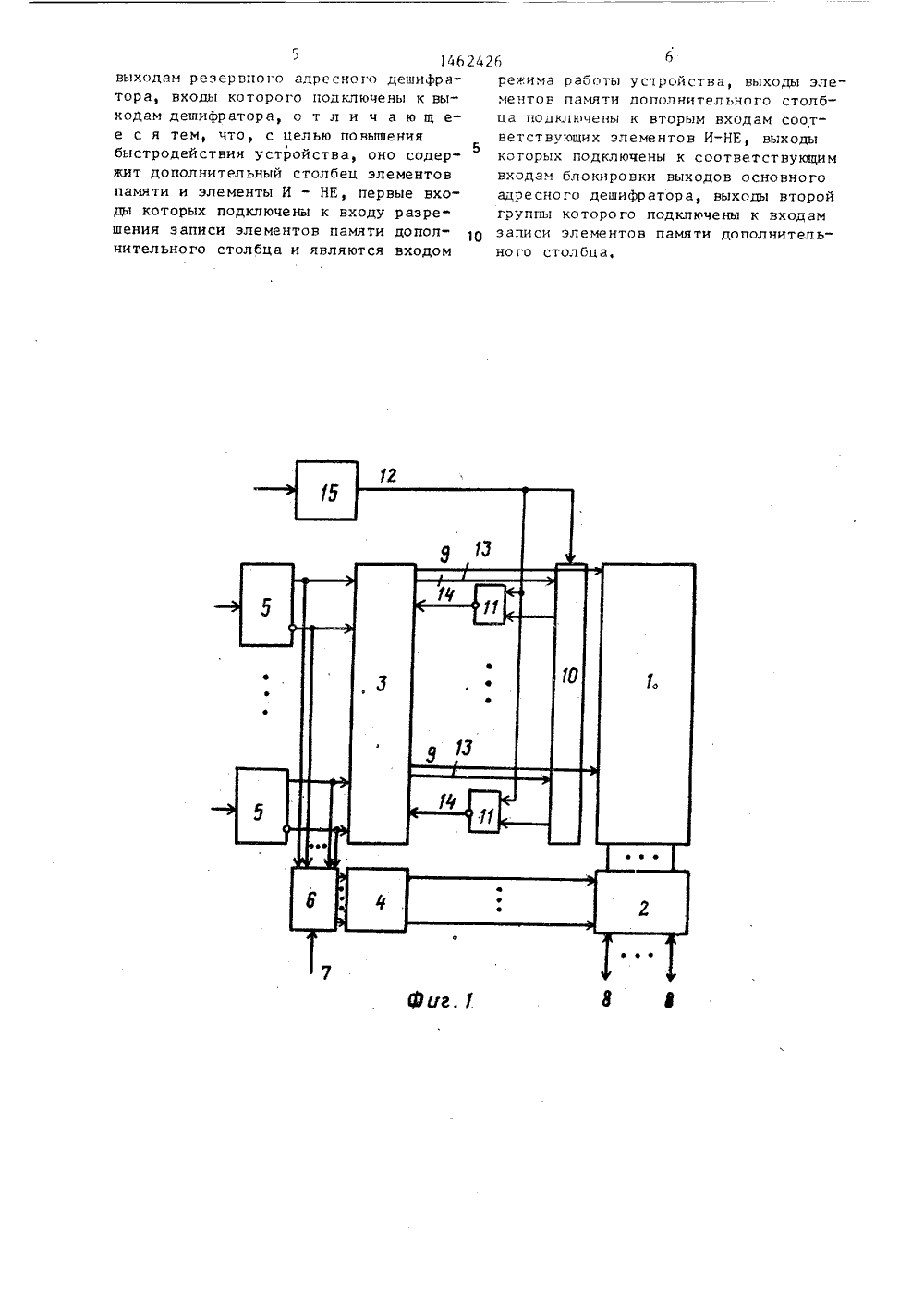

(57) Изо тельной вирован Цель иэо РАТИВНОЕ 3 С РЕЗЕРВИ бретение о технике, в овног гналы с резервныиоку резерным запори бретенияИзобретение отно я к вь апоминающих ус ально ств в полнен эобрет Целью ние быст На фия являетсяустройстваена блок-сх ьппе деист вия изображ на фииггера н устроиств лизация т возмоКМДП-тр ан стоГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР(56) Патент Сц 1 А Ф 4393474кл. 0 11 С 11/40, опубликВерниковский Е,А, и дрвыход годных и избыточносЗарубежная электронная теУ 1 О, с.20,ПОМИНАЮ 1 ЦЕЕ УСТОВАНИЕМ СТРОК носится к вычисли- частности к резерющим устройствам, повышение быстроельнои технике, в частности к запоминающим устройствам, и может быть спользовано при создании оперативнь Устройство содержит основной накопитель 1, резервный накопитель.2, осовной адресный дешифратор 3, реэервдействия устройства, В оперативное запоминающее устройство с резервированием строк, содержащее основной накопитель 1, резервный накопитель 2, основной дешифратор 3, резервный де- шифратор 4, адресные формирователи 5, дешифратор 6, введены дополнительный столбец 10 элементов памяти и элементы И-НЕ 11, Перед работой программируется дешифратор 6 на выявление отказ авших строк, а в элементы памяти дополнительного столбца 10, соответствующие отказавшим строкам, заносятся единицы, формирующие на соответствующих элементов сигналы блокировки выходов адре сно го дешифр атор а 3С выходов дешифратора 6 чере дешифратор 4 подключают ст вного накопителя 2, 2 ил,ный адресный дешифратор 4, адресныеформирователи 5, дешифратор 6, входпрограммирования устройства, выходы8 устройства, первую группу выходов9 основного адресного дешифратора,дополнительный столбец 1 О элементовпамяти, элементы И-НЕ 11, вход 2 ре 1 кима работы устройства, вторую группу выходов 13 основного адресного дешифратора и входы 14 блокировкиосновного адресного дешифратора 3.Кроме того, на фиг, 1 показан триггер15, Триггер 15 (фиг,2) может содержать бистабильную ячейку 16 на КМДПтранзи "торах, управляющий транзистор14624217 и , установочный конденсатор 1 ЯПеред началом работы программируется дешифратор 6, Он может быть вы 5 полнен в виде постоянной памяти, в которую з ано ся т ся адр е с а неи спр авных строк и запоминаются на постоянных запоминающих элементах с плавкими перемычками, Программирование осуществляется путем передачи напряжения программирования на вход 7,После подачи напряжения питания на запрограммированное устройство обращение к нему некоторое время запрещена (на входе 12 поддерживается низкий уровень напряжения), Триггер 15 этот р жим обеспечивает следующим обраЗам, Транзистор 17 закрыт, Из-за на личия емкости конденсатора 18 бистабильная ячеика 16 установится в состояние "0", и на выходе триггера 15 буцет низкий уровень напряжения. Этот уровень поступит на первые входы 2 элементов И-НЕ 11, в результате чего ьсе строки основнога адреснога,цешифратора 3 окажутся незаблокированными, Сигнал с выхода триггера 15 также разрешает производить запись в элементы памяти дополнительного столбца 10, На адре сные входы устройства последовательно подаются адреса неисправных строк, в результате чего дешифратор 3 будет последовательно по 35 давать на входы лементов памяти дополнител ьно го столбцаО саответ ствующих неисправным строкам, сигналы выборки, Элементы памяти дополнительного столбца 10, на которые поступали выборки, переключат "я и установят на вторых входах соответствующих элементов И-НЕ 11 высокий потенциал, После перебора всех адресов неисправных строк на вход триггера 15 подается импульс положительной полярности, которой откроет транзистор 17, в результате чего зарядится емкость конденсатора 18, и бистабильная ячейка 16 переключится в состояние "1", На входе 12 установится высокий уровень напряжения, который в дальнейшем не изменится при любых изменениях на входе триггера 15, Высокий уровень на выходе триггера 15 запрещает запись в элементы памяти дополнительного столб" ца 10 и устанавливает высокий уровень на первых входах элементов И-НЕ 11, В результате на. выходах элементов 64И-НЕ 11, соответствующих неисправнымстрокам, установится низкий уровень,который поступит на входы блокировкиэтих строк основного адресного дешифратора 3, После этого разрешаетсяобращение к устройству,Дальнейшая работа устройства осуществляется обычным образом, При поступлении на адресные входы исправнойстроки (данная строка дешифратора 3не заблокирована) происходит выборкаданной строки из основного накопнтеля 1, Дешифратор 6 выявляет, что обращение происходит к исправной строке и подает на резервный адресный дешифратор 4 сигнал запрещения выборкииз резервного накопителя 2,При поступлении адреса неисправнойстроки основной дешифратор 3 не подает сигнала выборки данной строки основного накопителя 1, гак как на входе блокировки данной строки дешифратора 3 установлен низкий уровень. Дешифратор 6 по адресу, поступившему навход, сформирует сигнал, поступающийна резервный адресныи дешифратор 4.Этот сигнал выбирает из резервногонакопителя 1 строку, соответствующуюнеисправной строке основного накопителя 1,Таким образом, сигналы блокировкинеисправных строк подаются на дешифратор 3 постоянно и независимо от адреса, поступающего на адресные входы,Поэтому отпадает необходимость подачи сигнала блокировки в каждом циклевыборки,Фор мул а из обре тенияОперативное запоминающее устройство с резервированием строк, содержащее основной накопитель, адресные входыстрок которого подключены к выходам первой группы основного адресногодешифратора, информационные входы которого подключены к информационным вхоцам дешифратора и выходам адресных формирователей, входы которых являются адресными входами устройства, информационные входы-выходы основного накопителя подключены к информационным входам- выходам резервного накопителя и являются информационными входами-выходами устройства, адресные входы строк резервного накопителя подключены кг146 выходам резервного адресного деширатора, входы которого подключены к выходам дешифратора о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия устройства, оно содержит дополнительный столбец элементов памяти и элементы И - НЕ, первые вхо" ды которых подключены к входу разрешения записи элементов памяти дополнительного столбца и являются входом 24266режима работы устройства выходы эле -ментов памяти дополнительного столбца подключена к вторым входам соответствующих элементов И-НЕ, выходы 5которых подключены к соответствующимвходам блокировки выходов основногоадресного дешифратора, выходы второйгруппы которого подключены к входамзаписи элементов памяти дополнительного столбца,146 242 б аказ 731/53 Тираж 558 Подписно НИИПИ Государственного комитета по изобретениям и открытиям113035, Москва, Ж, Раущская наб д. 4/5 Т СССР ельский комбинат "Патент", г, Ужгород, ул, Гагарина, 1 иэводственно-и Составитель С ЗустенкоРедактор О, Спе си вых Техред И. Ходанич Корректор С.Шек

СмотретьЗаявка

4148815, 19.11.1986

ПРЕДПРИЯТИЕ ПЯ Р-6429, МОСКОВСКИЙ ИНЖЕНЕРНО-ФИЗИЧЕСКИЙ ИНСТИТУТ

БАРАНОВ ВАЛЕРИЙ ВИКТОРОВИЧ, БЕРЕЗИН АНДРЕЙ СЕРГЕЕВИЧ, КОРОЛЕВ СЕРГЕЙ АНАТОЛЬЕВИЧ, ОНИЩЕНКО ЕВГЕНИЙ МИХАЙЛОВИЧ, ПОПЛЕВИН ПАВЕЛ БОРИСОВИЧ, ТРОШИН СЕРГЕЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, оперативное, резервированием, строк

Опубликовано: 28.02.1989

Код ссылки

<a href="https://patents.su/4-1462426-operativnoe-zapominayushhee-ustrojjstvo-s-rezervirovaniem-strok.html" target="_blank" rel="follow" title="База патентов СССР">Оперативное запоминающее устройство с резервированием строк</a>

Предыдущий патент: Устройство для управления регенерацией динамической памяти со свободными зонами

Следующий патент: Способ намотки многослойных высоковольтных электрических катушек

Случайный патент: Объектив с большим задним фокальным отрезком