Микропроцессорная система для программного управления технологическим оборудованием

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

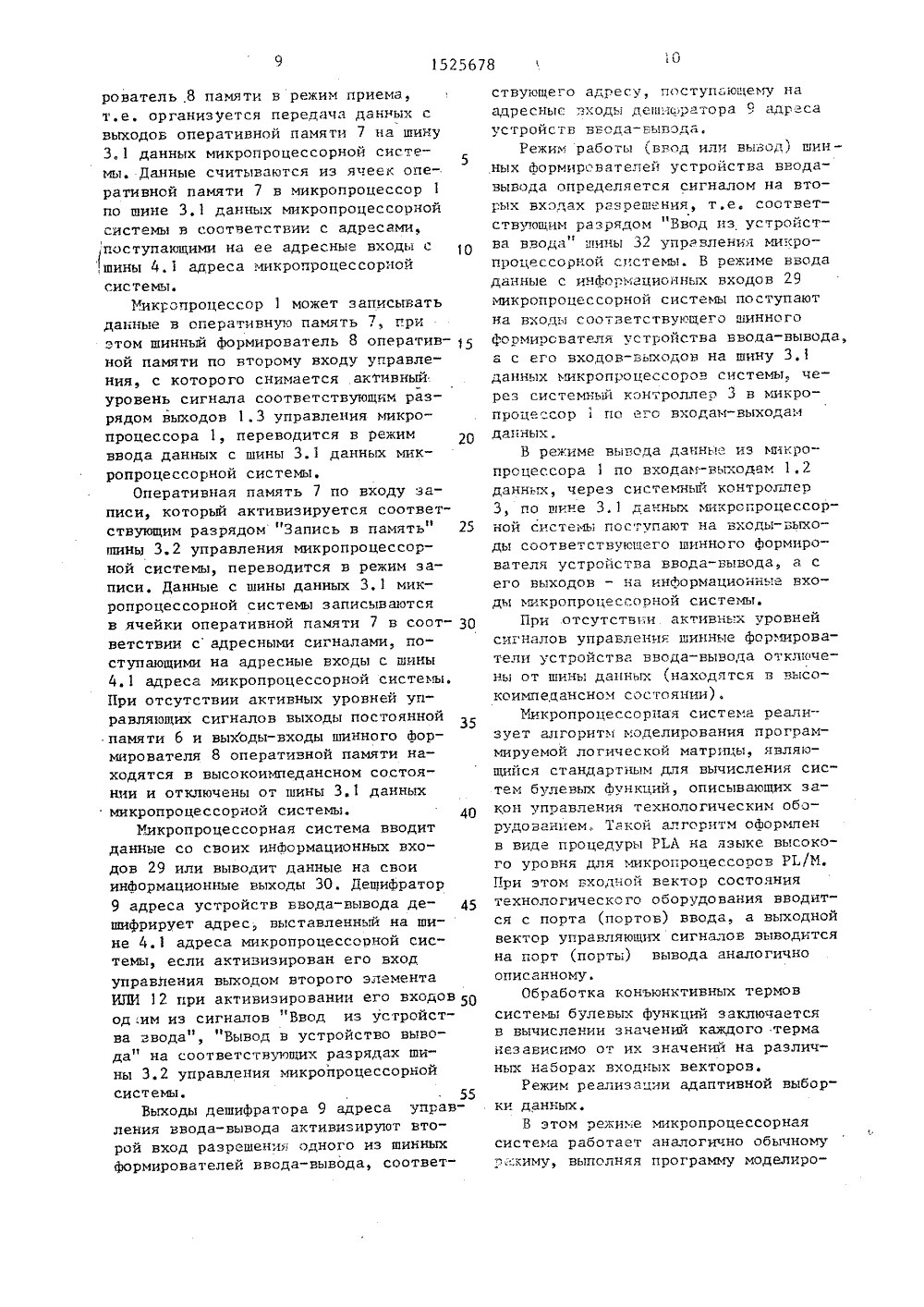

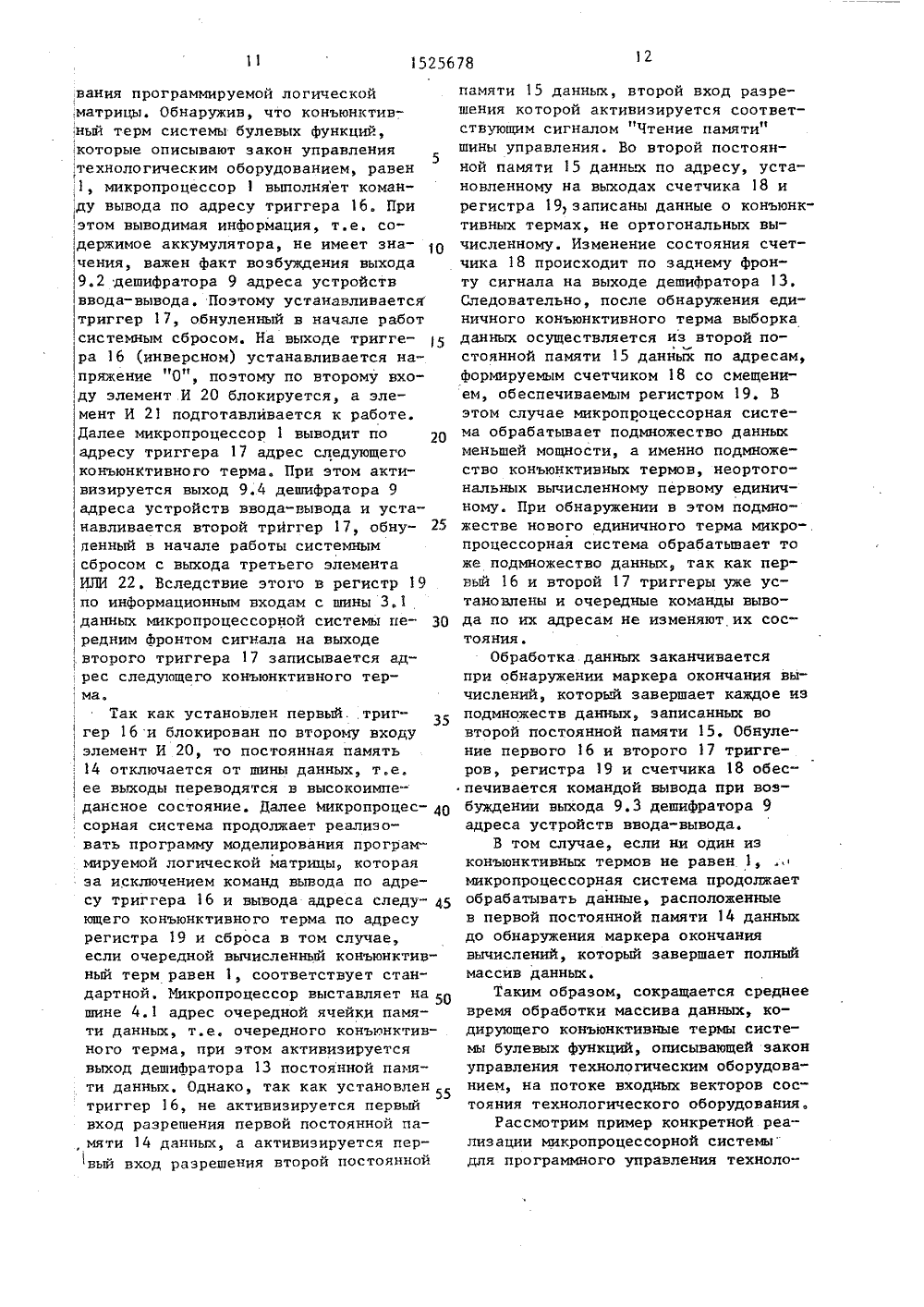

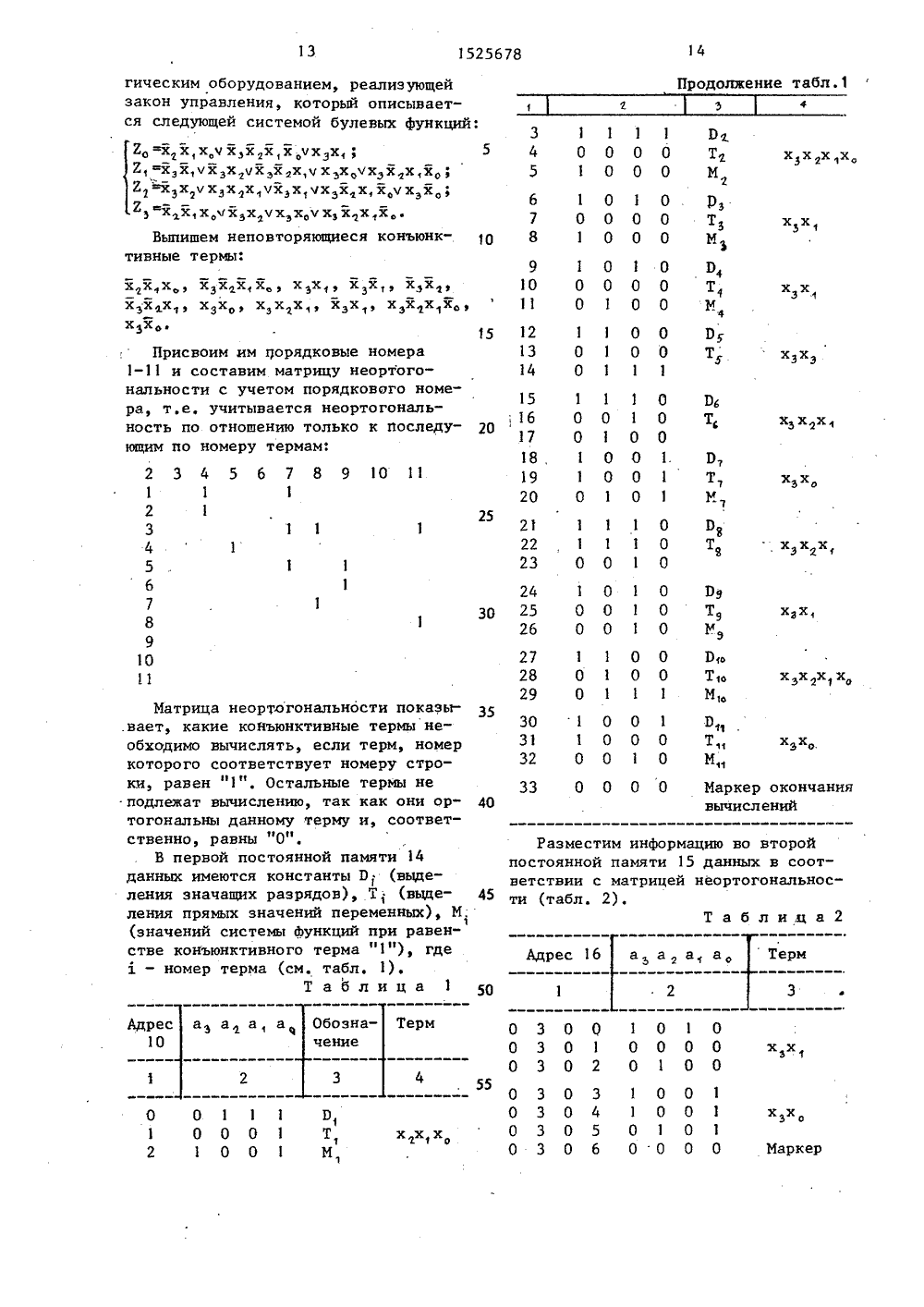

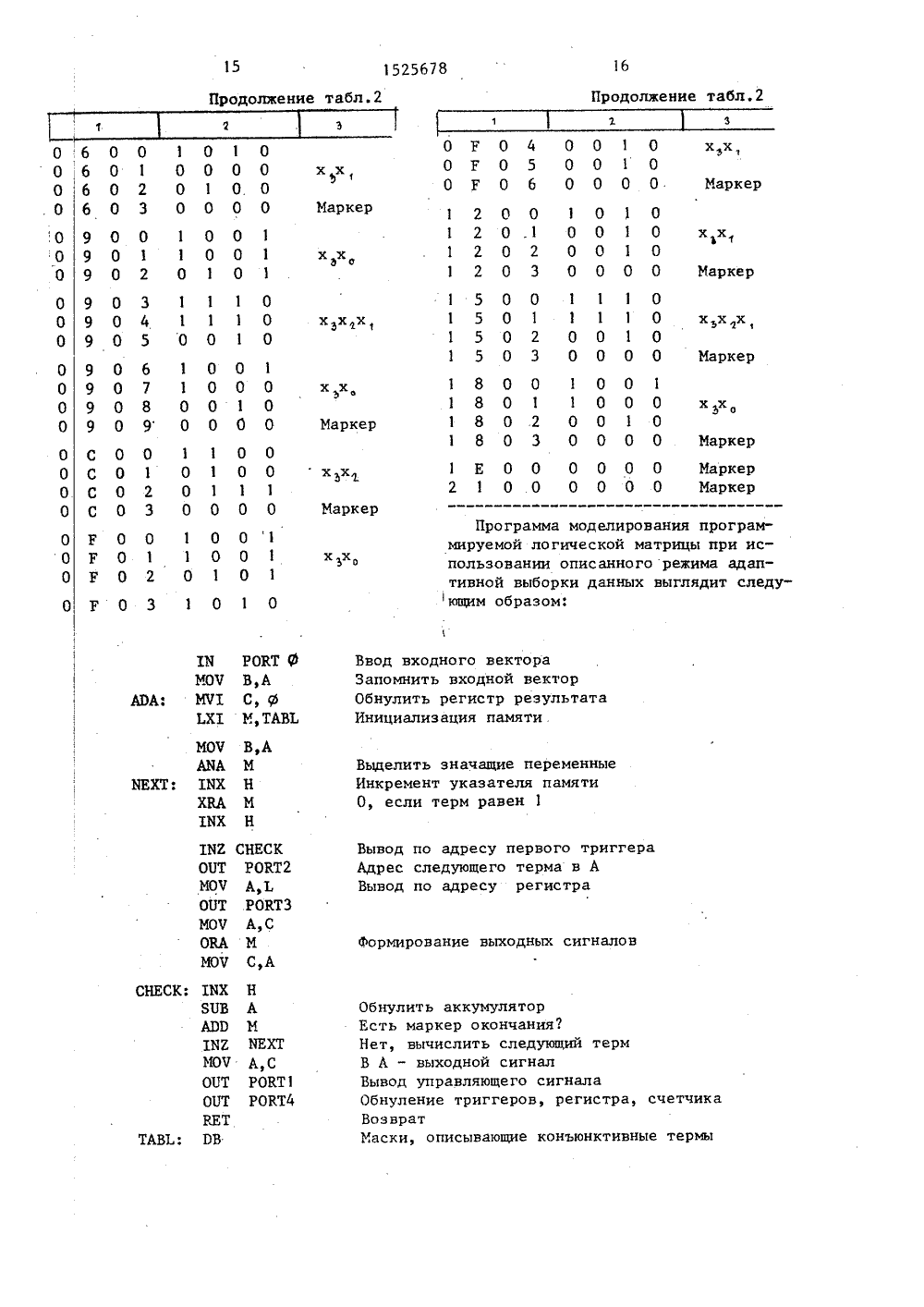

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК А 1 678 18 4 С 05 ЕТЕН ИСАНИЕ ТОРСКОМУ СВ ЕПЬСТВ я к микрожет бытьрованных е радио- кропроь, 1984,хно нныхи т.д. ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР(56) Пупырев Е,И. Перестраиваемыеавтоматы и микропроцессорные системы. - М.: Наука, 1984, с. 103,132-138.Патент США М 4509120,кл. С 06 Р 15/00, 1984.Авторское свидетельство СССРР 1172455, кл, С 06 Р 15/00, 1984,Авторское свидетельство СССРР 1012205, кл. С 05 В 19/18, 1983Алексенко А.Г., Галицын А.Л.,Иванников А.Д. Проектированиэлектронной аппаратуры на мицессорах. - М.: Радио и связс. 11, 109-110, 129,Коффрон Дж. Технические средствамикропроцессорных систем. - М.: Мир,1983, с, 43, 49.Шевкопляс Б.В. Микропроцессорныеструктуры. - М.: Радио и связь,1986, с. 23, рис2.8.Лазарев В.Г Пийль Е.И Турута Е.М. Построение программируемых:управляющих устройств. - М,: Энергоиздат, 1984, с, 69, 74-87Изобретение относится к микропроцессорной технике и может быть использовано в автоматизированных системах для программного управления(54) МИКРОПРОЦЕССОРНАЯ СИСТЕМА ДЛЯПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОПЧЕСКИМ ОБОРУДОВАНИЕМ(57) Изобретение относитспроцессорной технике и моиспользовано в автоматизисистемах для программного управления технологическими процессами, например, в системах числового программного управления производственныхкомплексов, роботов-манипуляторови т,д, Целью изобретения являетсяповышение производительности микропроцессорной системы путем введениярежима адаптивной выборки данных.Микропроцессорная система для программного управления технологическимоборудованием состоит из микропроцессора, тактового генератора, системного контроллера, буфера адреса, дешифратора адреса памяти, постояннойпамяти, оперативной памяти, шинногоформирователя оперативной памяти,дешифратора адреса устройств ввода -вывода, шинных формирователей устройств ввода - вывода, первого ивторого элементов И, трех элементовИЛИ, 2 ил.,2 табл. огическими процессами, нав системах числового проого управления производстве ксов,роботов-манипуляторовзвода-вывода подключена к первым входам разрешения соответствующих винных формирователей ввода-вывода, торые входы разрешения подключены к азряду шины управления микропроцессорной системы "Ввод из устройства вода", выходы шинных формирователей вода-вывода являются информационнывыходами микропроцессорной системы Оих входы являются информационными ходами микропроцессорной системы,т л и ч а ю щ а я с я тем, что,целью повышения производительноси микропроцессорной системы, дополительно содержит дешифратор постонной памяти данных, первую и вторую остоянные памяти данных, первый и торой триггеры, счетчик, регистр, ервый и второй элементы И и третий 20 лемент ИЛИ, причем информационные ходы дешифратора постоянной памяти анных и дешифратора адреса устройств вода-вывода подключены к шине адреа микропроцессорной системы, вход 25 азрешения дешифратора постоянной амяти данных соединен с разрядом "Чтение памяти" шины управления,выход дешифратора постоянной памяти анных подключен к первым входам пер вого и второго элементов И, второй выход дешифратора адреса устройств ввода-вывода подключен к входу установки первого триггера, третий выход дешифратора адреса устройств ввода- вывода подключен к первому входу третьего элемента ИЛИ, второй вход которого подключен к третьему выходутактового генератора, четвертый выходдешифратора адреса памяти подключенк входу установки второго триггера,выход третьего элемента ИЛИ подключенк входам сброса первого и второготриггеров, счетчика и регистра, выход первого триггера подключен к вторым входам первого и второго элементов И, выход второго триггера подключен к входу синхронизации регистра,выход первого элемента И подключен кпервому входу разрешения первой постоянной памяти данных, второй входразрешения которой подключен к разряду шины управления микропроцессорной системы "Чтение памяти", подключенному также к второму входу разрешения второй постоянной памяти данных, выход второго элемента И подключен к первому входу разрешениявторой постоянной памяти данных, атакже к счетному входу счетчика, выходы счетчика подключены к первойгруппе адресных входов второй постоянной памяти данных, к второй группе которых подключены выходы регистра, выходы первой и второй постояннойпамяти данных, а также входы регистраподключены к шине данных микропроцессорной системы, а адресные входы первой постоянной памяти данных подключены к шине адреса микропроцессорнойсистемы, 15256781525678 Составитель С.ЗубковРдактор Л,Пчолинская Техред М.Дндык Корректор О.Кр Тираж 788 Подписноеомитета по изобретениям и открытиям при ГКНТ СССР осква, Ж, Раушская наб., д. 4/5 изводственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарин Заказ 7226/44ВСКИПИ Государственно11303 3; 9фЦель иэобретения - повышение производительности микропроцессорной системы путем введения режима адаг " тивной выборки данных.гэНа Фиг. 1 изображена Функциональная схема микропроцессорной систеьы; на Фиг. 2 - временная диаграмма раба.- ты микропроцессорной системы в режиме адаптивной выборки данных, 10Микропроцессорная система для про- граммнога управления технологическим оборудованием содержит микропроцессор 1 с адресными выходами 1.,1 входами-выходами 1,2 данных, выходами 5 1.3 управления, тактовыми входами 1,4 и 1.5 первой и второй Фаз, вхсдом 1,6 сброса, входом 1.7 готовности и выходам 1.8 синхронизации, тактовый генератор 2 с входами 2,1 и 2,2 о подключения кварцевого резонатора входом 2.3 синхронизации, тактовыми выходами 24 и 2.5 первой и второй Фаз, выходом 2.6 сброса, выходом 2.7 готовности и вьгходам 2.8 синхро:- 25 низации, системный контроллер 3 с выходаии-входами 3,1 данных, являющимися шиной данных микрапроцессорисемы, и выодм . управле ния являющимися шиной управления я микропроцессорной систеьы буфер 4 адреса с выходами 4,1, являющимися шиной адреса микропрацессарнаи систеьы Дешифратор 5 адреса памЯГи с выходам 5,1 ПОДключения пОстОЯннОЙ памяти и выходом 5.подключения ОПЕРативнай ПаМЯТИ ПОСТОЯННУЮ Пс 1 мять 6, оперативную память 7 шинный Формирователь 8 оперативной памяти, дешифратор 9 адреса устройств ввода" .1 о вывода с выходами 9,1 подключения устройств ввода-вывода и выходами 9,.2- 9,4, шинный Фармиравател; 1 О устройств ввода в выво, первый 1: и второй 12 элементы ИЛИ, дешифратор 13 постоянной памяти данных первую 14 и вторую 15 постоянную память данных, первый 16 и второй 17 триггеры счетчик 18, регистр 19 первый 20 и второй 2 т элементы И, третий элемент ИЛИ 22 вход 23, яттляющийся входам сброса микропроцессорной системы, вход 24, являющийся входом готовности микропроцессорной систеь 1, вход 25, являющийся входом захватаээ микропропессарной системы вход 26, являющийся входом запроса прерывания .микропроцессорной системы выход 27 т являющийся выходом ожидания микропра:.ессорнай системь, выход 28, являющийся выходом разрешения прерывания микропроцессорной систеьш 1, входы 29, являющиеся информационными вхадаги микропроцессорной системы, и ВыхОДы 3.) ЯвлЯюЩиесЯ информаЦионными выходами микропроцессорной системью Первый 2.1 и второй 2,2 входы тактового генератора подключены к кварцевому резонатору, Пятый вход 2.3 тактового генератора 2 подключен к выходу синхронизации 1.8 микропроцессора 1. Первый 2,4 и второй 2.5 выходы тактового генератора 2 подключены к первому 14 и второму 15 тактовым входам микропроцессора 1 соответственно, Третий 2.6 и четвертый 2.7 выходы тактового генератбра 2 поцключены к входам сброса 1.6 и готовности 1.7 микропроцессора 1 соответственно, Пятый вьгход 2.8 тактового генератораподключен к входу синхронизации системного контроллера 3. Адресные выходы 1, микттоттпацессаОа 1 падключень" к инфармацион тть," входам буйера 4 Яда:"са ВхаДыБыхады ,2 данных микрапООцессара 1 ПОДКЛЮЧЕНЫ К ВХОДаМ-БЬП.ОтаМ ДаННЫХ системного контроллера 3 Выходы. управления 1,3 микропроцессора 1 под- .КЛЮЧЕНЫ К БХОДБМ УПРс;БЛЕНИЯ СИСТЕМ- ного контроллера 3. Первый и второй входы разрешения буфера 4 адреса подключены к разряду шины 32 управления микропроцессорной систРмы Пад" тверждение захвата" Информационные входы дешифраторов 5 и 9 адреса памяти и адреса устройств ввода-вывода подключены к шине 4 адреса мик" рапрацессарной системы, Бхад разрешения дешифратара 5 адреса памяти падклочен к выходу первого элемента ИБ 11, первый и второй входы котооага подключены к разрядам шины 3.2 управления микропроцессорной системы "Чтение памяти", "Запись в память," соответственно. Первый выход 5.1 дешифратора 5 адреса памяти подключен к первому входу разрешения постоянной памяти 6. Второй выход 5.2 дешифратора 5 адреса памяти подключен к входу разрешения оперативной памяти / и к первому входу разрешения шин:.Ога Формирователя 8 оперативной памяти. Второй вход разрешения пост%.янпай памяти 6 подключен к разряду35 5 15256 выходов 1.3 управления микропроцессора 1 "Прием", также подключенному к второму входу разрешения шинного формирователя 8 оперативной памяти, Вход записи оперативной памяти 7 подключен к разряду шины 32 управления микропроцессорной системы "Запись в память". Адресные входы постоянной б и оперативной 7 памяти подключены к шине 4.1 адреса микропроцессорной системы, Информационные выходы постоянной памяти 6, входы-выходы шинных формирователей 8 и О оперативной памяти устройств ввода-вывода 5 подключены к шине данных 3,1 микропроцессорной системы, Выходы .шинного формирователя 8 оперативной памяти подключены к входам данных оперативной памяти 7, выходы данных ко торой подключены к входам шинного формирователя 8 памяти. Вход разрешения дешифратора 9 адреса устройств ввода-вывода подключен к выходу второго элемента ИЛИ 12, первый и вто рой входы которого подключены к разрядам шины 3.2 управления микропроцессорной системы "Ввод из устройства ввода", "Вывод в устройство вывода" соответственно.Труппа информа ционных выходов 9.1 дешифратора адреса устройств ввода-вывода. 9 подключена к первым входам разрешения соответствующих шинных формирователей 10 устройств ввода-вывода, вторые входы разрешения которых подключены к разряду шины 3,2 управления микропроцессорной системы Ввод из устройства ввода". Выходы шинных формирователей 10 ввода-вывода являются и 40 информационными выходами 30 микропроцессорной системы, а их входы являются информационными входами 29 микропроцессорной системы. Информационные входы дешифратора 13 посто янной памяти данных подключены к шине 4,1 адреса микропроцессорной системы, а его вход разрешения подключен к разряду шины 3.2 управления микропроцессорной системы Чтение памяти . 50 Выход дешифратора 13 постоянной памяти данных подключен к первым входам первого 20 и второго 21 элементов И. Второй выход 9.2 дешифратора адреса устройств ввода-вывода подключен к входу установки первого триггера 16, Третий выход 9,3 дешифратора адреса устройств ввода-вывода подключен к.первому входу третьего эле 78 6мента ИЛИ 22, второй вход которого подключен к третьему выходу 2,6 тактового генератора 2. Четвертый 9,4 выход дешифратора адреса памяти 9 подключен к входу установки второго триггера 17, Выход третьего элемента ИЛИ 22 подключен к входам сброса первого 16 и второго 17 триггеров, счетчика 18 и регистра 19, Выход первого триггера 16 подключен к вторым входам первого 20 и второго 21 элементов И, Выход второго триггера 17 подключен ко входу синхронизации регистра 19. Выход первого элемента И 20 подключен к первому входу разрешения первой постоянной памяти 14 данных, второй вход разрешения которой .подключен к разряду шины 3,2 управления микропроцессорной системы "Чтение памяти",подключенному также к второму входу разрешения второй постоянной памяти 15 данных. Выход второго элемента И 21 подключен к первому входу разрешения второй постоянной памяти 15 данных, а также к счетному входу счетчика 18, Выходы счетчика 18 подключены к первой части адресных входов второй постоянной памяти 15 данных, к второй части которых подключены выходы регистра 19. Выходы первой 14 и второй 15 постоянной памяти данных, а также входы регистра 19 подключены к шине данных 3,1 микропроцессорной системы. Адресные входы первой постоянной памяти 14 данных подключены к шине адреса 4,1 микропроцессорной системы.Микропроцессорная система для программного управления технологическим оборудованием работает следующим образом.Обычный режим работы.В этом режиме тактовыйгенератор 2 (фиг. 1) формирует две неперекрывающиеся тактовые последовательности, которые с его выходов 2.4 и 2.5 поступают на тактовые входы первой 1.4 и второй 1.5 фаз микропроцессора 1. Стабильность тактовой частоты обеспечивается кварцевым резонатором, подключенным к входам 2.1 и 2,2 тактового генератора 2.Микропроцессор 1 генерирует сигналы адреса, данных и управления после подачи сигнала сброса на соответствующий его вход 1.6, причем внешний сигнал сброса с входа 23 микропроцессорной системы стробируется в15 20 тактовом генераторе 2 и поступаетна его выход 2.6 ф после установленияуровня "1" на входе 24 готовностимикропроцессорной системы, причемсигнал готовности стробируется в так товом генераторе 2 и с его выхода2,7 поступает на вход 1,7 готовностимикропроцессора 1, Если же на входе24 микропроцессорной системы установ-лен сигнал "О", то на выходе 27 микропроцессорной системы устанавливается сигнал "1", свидетельстзующийо том, что микропроцессорнаходится в режиме ожидания готовности,Микропроцессор 1 выдает слово состояния на шину 1.2 данных по синхро.сигналу на соответствующем выходе1.8, поступающему на вход 2.3 тактового генератора 2 в первом тактекаждого машинного цикла, а стробированный по первой Фазе сигнал синхронизации (системный строб) с выхода2.8 тактового генератора 2 поступаетна вход синхронизации системногоконтроллера 3, в который записывается слово состояния микропроцессорас входов - выходов 1,2 данных микропроцессора 1. Системный контроллер3 по слову состояния и сигналам навыходах 1,3 управления микропроцессора 1 Формирует шину управлекия 3,2микропроцессорной систеьи. а такжешину данных 3,1 микропроцессорной "истемь 1, обеспечивая ее требуемую нагру-.зочную способность и двунаправленность передачи данных на входах-выходах 1.2 данных микропроцессора 1,Буфер 4 адреса формирует по адресным сигналам на соответствующих выходах 1,1 микропроцессора 1 шину 4.1адреса микропроцессорной системы,обеспечивая ее требуемую нагрузочнуюспособность,Микропроцессорную систему можноперевести в режим прерывания и захвата подачей соответствующих сигналовна входы 25 и 26, При переходе в ре жим прерывания с выхода 28 снимаетсясигнал разрешения прерывания При переходе микропроцессорной системь врежим захвата на соответствующем разряде выходов 1.3 управления микропроцессора 1 так же, как и на шине 3.2управления микропроцессорной системы,устанавливается сигнал подтверждениязахвата, который по первому и втором,, входам управления переводит выходыбуфера адреса 4 в высокоимпедансное состояние. По этому сигналу выходысистемного контроллера 3, выходы 11 адреса, входы-выходы 1,2 данных микропроцессора 1 переводятся в высокоимпедансное состояние. Режимы захва а и грерывания в предлагаемой микропроцессорной системе не используются.Микропроцессор 1 считывает и выполняет программу, записанную в постоянной памяти 6 либо в оперативной памя". ти 7. При этом дешифратор 5 адреса памяти дешифрирует адрес, выставленный на шине 4,1 адреса микропроцессорной системы, если на шине 3,2 управления выставлен один из сигналов "Чтение памяти , "Запись в память" при этом активизируется выход первого элемента ИЛИ 11 и вход управления дешифратора 5. Если на шине 4.1 адреса микропроцессорной системы выставлен адрес постоянной памяти 6, то активизируется выход 5.1 дешифратора 5 и первый вход управления постоянной памяти 6.Если на шине адреса 41 микропроцессорной системь; выставлен адрес оперативной памяти 7, то активизирует я выход 5,2 дешифратора 5. вход управления оперативной памяти 7 и первый вход управления шинного формирователя 8 оперативной памяти.Выходы постоянной памяти б подключаются к шине 3,2 данньгх микропроцес сорной системы, если активизированкроме первого входа управления, второй вход управления сигналом пПрием с соответствующего разряда выходов 1.3 управления микропроцессораДанные считываются из ячеек постоянной памяти 6 в микропроцессорпо .пине 3,2 данных микропроцессоркой системы через входы-выходы данных системного контроллера ка входы-выходы 1.2 данных микропроцессора 1 в соответствии с адресами, поступающиви на адресные входы с шины 4. адреса микропроцессорной системы.Дпя считывания данных из оперативной памяти 7, кроме активизирования ее входа. управления, на ее вход записи пода. ется сигнал "О" с соответствующего разряда шины 3.2 управления микропроцессорной системы "Запись в память", а второй вход управления шинного формирователя 8 оперативной памяти активизируется разрядом выходов 13 управления микропроцессорд 1 "Прием", Это переводит шинный Форю. -20 рователь .8 памяти в режим приема,т,е, организуется передача данных свыходов оперативной памяти 7 на шину3,1 данных микропроцессорной систе 5мы. Данные считываются из ячеек оперативной памяти 7 в микропроцессор 1по шине 3,1 данных микропроцессорнойсистемы в соответствии с адресами,;поступающими на ее адресные входы с,шины 4.1 адреса микропроцессорнойсистемы.Микропроцессор 1 может записыватьданные в оперативную память 7, приэтом шинный формирователь 8 оперативной памяти по второму входу управления, с которого снимается активный.уровень сигнала соответствующим разрядом выходов 1.3 управления микропроцессора 1, переводится в режимввода данных с шины 3,1 данных микропроцессорной системы,Оперативная память 7 по входу записи, который активизируется соответствующим разрядом "Запись в память" 25шины 3,2 управления микропроцессорной системы, переводится в режим записи, Данные с шины данных 3.1 микропроцессорной системы записываютсяв ячейки оперативной памяти 7 в соответствии с адресными сигналами, поступающими на адресные входы с шины4.1 адреса микропроцессорной системы,При отсутствии активных уровней управляющих сигналов выходы постояннойпамяти 6 и выходы-входы шинного формирователя 8 оперативной памяти находятся в высокоимпедансном состоянии и отключены от шины 3,1 данныхмикропроцессорной системы. 40Микропроцессорная система вводитданные со своих информационных входов 29 или выводит данные на своиинформационные выходы 30. Дешифратор9 адреса устройств ввода-вывода дешифрирует адрес, выставленный на шине 4.1 адреса микропроцессорной системы, если активизирован его входуправления выходом второго элементаИЛИ 12 при активизировании его входов 50од .им из сигналов "Ввод из устройства ввода", Вывод в устройство вывода" на соответствующих разрядах шины 3,2 управления микропроцессорнойсистемы, 55Выходы дешифратора 9 адреса управления ввода-вывода активизируют второй вход разрешения одного из шинныхФормирователей ввода-вывода, соответствующего адресу, поступающему наадресныс входы деш 1 юратора 9 адресаустройств ввода-вывода.Режим работы (ввод или вывод) шинных формирователей устройства вводазывода определяется сигналом на вторых входах разрешения, т,е, соответствующим разрядом "Ввод из устройства ввода" пины 32 упргвления микропроцессорной системы. В режиме вводаданные с информационных входов 29микропроцессорной системы поступаютна входы соответствующего шинногоФормирователя устройства взоца-вывода,а с его входов-выходов на шину 3,1данных микропроцессоров системы, через системный контроллер 3 в микропроце"сор 1 по его входам-выходам,цанных.В режиме вывода данны из микропроцессора 1 по входам-выходам 1.2данных, через системный контроллер3, по шине 3.1 данных микропроцессорной системы пост упают на входы-выходы соответствующего шинного Формирователя устройства ввода-вывода, а сего выходов - на информационные входы микропроцессорной системы.При отсутствии активных уровнейсигналов управления шинные Формирователи устройства ввода-вывода отключены от шины данных (находятся з высокоимпедансном состоянии),Микропроцессорная система реализует алгоритм моделирования программируемой логической матрицы, являющийся стандартным для вычисления систем булевых Функций, описывающих закон управления технологическим оборудованием. Тгкой алгоритм оформленв виде процедуры Р 1.А на языке высокого уровня для микропроцессоров Р./М.При этом входной вектор состояниятехнологического оборудования вводится с порта (портоз) ввода, а выходнойвектор управляющих сигналов выводитсяна порт (порты) вывода аналогичноописанному.Обработка конъюнктивных термовсистемы булевых функций заключаетсяв вычислении значений каждого термансзависимо от их значений на различных наборах входных вектороз.Режим реализации адаптивной выборки данных,В этом режиме микропроцессорнаясистема работает аналогично обычномурсжиму, выполняя программу моделиро 1525678вания программируемой логической ,матрицы. Обнаружив, что конъюнктивный терм системы булевых функций, которые описывают закон управления технологическим оборудованием, равен 1, микропроцессор 1 выполняет коман,ду вывода по адресу триггера 16. При ,этом выводимая информация, т.е, со,держимое аккумулятора, не имеет значения, важен факт возбуждения выхода 9.2 дешифратора 9 адреса устройств ввода-вывода. Поэтому устанавливается триггер 17, обнуленный в начале работ системным сбросом, На выходе триггера 16 (инверсном) устанавливается напряжение "О", поэтому по второму входу элемент И 20 блокируется, а элемент И 21 подготавливается к работе. Далее микропроцессор 1 выводит по 20 адресу триггера 17 адрес следующего конъюнктивного терма. При этом активизируется выход 9,4 дешифратора 9 адреса устройств ввода-вывода и устанавливается второй трйггер 17, обну денный в начале работы системным сбросом с выхода третьего элемента ИЛИ 22, Вследствие этого в регистр 19 по информационным входам с шины 3.1 данных микропроцессорной системы пе редним фронтом сигнала на выходе ,второго триггера 17 записывается ад. рес следующего конъюнктивного терма.Так как установлен первьй. триг-гер 16 и блокирован по второму входу , элемент И 20, то постоянная память14 отключается от шины данных, т.е.ее выходы переводягся в высокоимпедансное состояние. Далее микропроцессорная система продолжает реализовать программу моделирования программируемой логической матрицы, котораяза исключением команд вывода по адресу триггера 16 и вывода адреса следующего конъюнктивного терма по адресурегистра 19 и сброса в том случае,если очередной вычисленный конъюнктивный терм равен 1, соответствует стандартной, Микропроцессор выставляет на 50шине 4.1 адрес очередной ячейки памяти данных, т.е, очередного конъюнктивного терма, при этом активизируетсявыход дешифратора 13 постоянной памяти данных. Однако, так как установлентриггер 16, не активизируется первый вход разрешения первой постоянной па, мяти 14 данных, а активизируется первый вход разрешения второй постоянной памяти 15 данных, второй вход разрешения которой активизируется соответствующим сигналом "Чтение памяти" шины управления. Во второй постоянной памяти 15 данных по адресу, установленному на выходах счетчика 18 и регистра 191 записаны данные о конъюнктивных термах, не ортогональных вычисленному. Изменение состояния счетчика 18 происходит по заднему фронту сигнала на выходе дешифратора 13, Следовательно, после обнаружения единичного конъюнктивного терма выборка данных осуществляется из второй постоянной памяти 15 данных по адресам, формируемым счетчиком 18 со смещением, обеспечиваемым регистром 19. В этом случае микропроцессорная система обрабатывает подмножество данных меньшей мощности, а именно подмножество конъюнктивных термов, неортогональных вычисленному первому единичному. При обнаружении в этом подмножестве нового единичного терма микро-. процессорная система обрабатывает то же подмножество данных, так как первый 16 и второй 17 триггеры уже установлены и очередные команды вывода по их адресам не изменяют их состояния.Обработка данных заканчивается при обнаружении маркера окончания вычислений, который завершает каждое из подмножеств данных, записанных во второй постоянной памяти 15. Обнуле" ние первого 16 и второго 17 триггеров, регистра 19 и счетчика 18 обеспечивается командой вывода при возбуждении выхода 9.3 дешифратора 9 адреса устройств ввода-вывода.В том случае, если ни один из конъюнктивных термов не равен 1, микропроцессорная система продолжает обрабатывать данные, расположенные в первой постоянной памяти 14 данных до обнаружения маркера окончания вычислений, который завершает полный массив данных.Таким образом, сокращается среднее время обработки массива данных, кодирующего конъюнктивные термы системы булевых функций, описывающей закон управления технологическим оборудованием, на потоке входных векторов состояния технологического оборудования.Рассмотрим пример конкретной реализации микропроцессорной системы для программного управления техноло25 21 22 23 1 1 1 1 1 1 О 0 1 0 0 О 8Т Х Х Х 1 О 1 О 0 1 0 О 1 О 0 0 24 25 26 30 Хз Х 10 0 1 0 0 127 28 29 П 1 о Т 1 о Мм ХЗХ 2 Х, Хо 1 0 0 1 0 О 0 030 31 32 ХЗХо 33 0 0 0 Маркер окончаниявычислений блиц а 2 Т а Терм Адрес 16 а а,а 2 а,( 3 ОбозначениеХ 2 Х 1 Х 0 гическим оборудованием, реализующейзакон управления, который описывается следующей системой булевых функций: Ео ффх 2 х хоч хэх гх х ч хзх 1 1 5Э 1 3 2 31 3 О 3 2 1 ОФЕ -2-ХЗХ 4 ХЗХ 2 Х 1 НХЭХ 1 ЧХЗХХ 1 Хоl ХЭХО Э3 2 Х 1 Хо/ХЗХ ЧХЗХОУ ХЭ Х 2 Х ХоВыпишем неповторяющиеся конъюнк"тивные термы: Х 2 ХХХЗХХ ХоХЗХ 1 ХЗХХЗХ 2 Ь ХЗХХ 1 в ХЗХо э ХХ 2 Х 1 ХЗХ 1 ф З 2 1 о ф ХзХ Присвоим им порядковые номера 1-11 и составим матрицу неортогональности с учетом порядкового номера, т,е, учитывается неортогональность по отношению только к последу ющим по номеру термам: 2 3 4 5 6 7 8 9 10 111 1 12 13 1 1 1415 1 16 17 18910 Матрица неортогональности показьг .вает, какие конъюнктивные термы необходимо вычислять, если терм, номер которого соответствует номеру строки, равен "1". Остальные термы не подлежат вычислению, так как они ор тогональны данному терму и, соответственно, равны "0".В первой постоянной памяти 14 данных имеются константы Э; (вьщеления значащих разрядов), Т, (выде ления прямых значений переменных), М;1 (значений системы функций при равенстве конъюнктивного терма "1"), где- номер терма (см. табл. 1).Таблица50 О О 1 1 1 0 1 0 0 0 1 Т 1 2 1 0 0 1 М,02РзМЮи,Т Разместим информацию во второй постоянной памяти 15 данных в соответствии с матрицей неортогональности (табл. 2).. 0 0 1 О 1 0 1 9 О 0 1 9 0 1 1 9 0 2 0 ххМаркер х х( 1 0 1 0 1 0 9 0 3 1 9 0 4 1 9 О 5 0 ххх, Маркер 0 1 О 0 1 0 0 0 9 0 6 1 9 0 7 1 9 0 8 0 9 0 9 0 0 0 0 0 0 0 0 0 Маркер х х,Маркер 0 0 0 0 1 1 0 О С 0 0 1 С О 1 0 С 0 2 0 С О 3 О 0 0 0 0 Маркер Маркер х х Маркер 0 1 0 1 0 1 Р 0 0 1 Р 0 1 1 Р 0 2 0 О 0 1 0 0 0 1 0 Р О 3 1 10 РОЕТ ФМОЧ В,ААОАф МЧ 1 С, Ф1 Х 1 М, ТАВ 1 МОЧ В,ААБА МБРЕХТ: 1 ЯХ НХВА М1 НХ Н 102 011 Т МОЧ 011 ТМОЧ ОКА УОЧ Н А М БРЕХТ А,С РОВ.Т 1 РОЕТ 4 СНЕСК: 1 ЮХ ББВ АЭЭ 132 МОЧ ОПТ 01.1 Т ЕЕТ ТАВ РВСНЕСКРОКТ 2А,ЬРОУЗА,СМС,А 0 Р 0 4 0 0 1 0 0 Р 0 5 0 0 1 0 0 Р 0 6 0 0 О 0 1 2 0 0 1 0 1 0 120.10010 1 2 О 2 0 0 1 0 1 2 О 3 0 О О 0 1 5 0 0 1 1 1 0 1 5 0 11 1 0 1 5 0 2 0 0 1 0 1 5 0 3 0 0 0 0 1 8 О 0 1 0 0 1 1 8 0 1 1 0 0 0 1 8 0 .2 0 0 1 О 1 8 0 3 0 0 0 0 1 Е 0 О 0 0 О 0 2 1 0 0 О 0 0 0 Программа моделирования программируемой логической матрицы при использовании описанного режима адаптивной выборки данных выглядит следующим образом: Ввод входного вектораЗапомнить входной векторОбнулить регистр результатаИнициализация памяти Выделить значащие переменныеИнкремент указателя памятиО, если терм равен 1 Вывод по адресу первого триггераАдрес следующего терма в АВывод по адресу регистра Формирование выходных сигналов Обнулить аккумуляторЕсть маркер окончанияНет, вычислить следующий термВ А - выходной сигналВывод управляющего сигналаОбнуление триггеров, регистра, счетчикаВозвратМаски, описывающие конъюнктивные термыСледовательно, за исключением четырех команд ОБТРОВТ 2, МОЧА, Ь, 013 Т РОЕТ 3,4 программа соответствует известной.Таким образом, микропроцессорная система обеспечивает сокращение временных затрат на вычисление закона управления технологическим оборудованием, заданным системой булевых Функций, более чем в 1,6 раза. 1 О Формула изобретения Микропроцессорная система для 15 программного управления технологическим оборудованием, содержащая микропроцессор, тактовый генератор, системный контроллер, буфер адреса, дешифратор адреса памяти, постоянную 2 О память, оперативную память, шинный Формирователь оперативной памяти, дешифратор адреса устройств ввода-вывода, шинные формирователи устройств ввода-вывода, первый и второй элемен ты ИЛИ, причем первый и второй входы тактового генератора подключены к кварцевому резонатору, третий и четвертый входы тактового генератора являются входами сброса и готовности 30 микропроцессорной системы соответственно, пятый вход тактового генератора подключен к выходу синхронизации микропроцессора, первый и второй вьг ходы тактового генератора подключены к первому и второму тактовым входам микропроцессора соответственно, третий и четвертый выходы тактового генератора подключены к входам сброса иготовности микропроцессора сост О ветственно, пятый и шестой входы микропроцессора являются входами захвата и запроса прерывания микропроцессорной системы соответственно, первый и второй выходы микропроцессора яв ляются выходами ожидания и разрешения прерывания микропроцессорной системы соответственно, пятый выход тактового генератора подключен к входу синхронизации системного контроллера, 5 О адресные выходы микропроцессора подключены к информационным входам буфера адреса, входы-выходы данных микропроцессора подключены к входам-выходам данных системного контроллера, 55 выходы управления микропроцессора подключены к входам управления системного контроллера, выходы-входы данных системного контроллера являются шиной данных микропроцессорной системы, выходы управления системного контроллера являются шиной управления микропроцессорной системы, первый и второй входы разрешения буфера адреса подключены к разряду шины управления микропроцессорной системы "Подтверждение захвата", выходы буФера адреса являются шиной адреса микропроцессорной системы, информационные входы дешифраторов адреса памяти и адреса устройств ввода-вьг вода подключены к шине адреса микропроцессорной системы, вход разрешения дешифратора адреса памяти подключен к выходу первого элемента ИЛИ, первый и второй входы которого подключены к разрядам шины управления микропроцессорной системы "Чтение памяти", "Запись в память" соответственно, первый выход дешифратора адреса памяти подключен к первому входу разрешения постоянной памяти, второй выход дешифратора адреса памятиодключен к входу разрешения оперативной памяти и первому входу разрешения шинного Формирователя оперативной памяти, второй вход разрешения постоянной памяти подключен к разряду выходов управления микропроцессора 11 иПрием , а также подключенному к второму входу разрешения шинного формирователя оперативной памяти, вход записи оперативной памяти подключен к разряду шины управления микропроцессорной системы "Запись в память", адресные входы постоянной и оперативной памяти подключены к шине адреса микропроцессорной систем,1, информационные выходы постоянной памяти, входы-выходы шинных Формирователей оперативной памяти и устройств ввода-вывода подключены к шине данных микропроцессорной системы, выходы шинного формирователя оперативной памяти подключены к входам данных оперативной памяти, выходы данных которой подключены к входам шинного формирователя памяти, вход разрешения дешифратора адреса устройствввода-вывода подключен к выходу второго элемента ИЛИ, первый и второй входы которого подключены к разрядам шины управления микропроцессорной системы "Ввод из устройства ввои и и да , Вывод в устройство вывода соответственно. группа информационных выходов дешифратора адреса устройств

СмотретьЗаявка

4417537, 23.03.1988

ПРЕДПРИЯТИЕ ПЯ М-5156

СИДОРЕНКО НИКОЛАЙ ФЕДОРОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТЮРИН СЕРГЕЙ ФЕОФЕНТОВИЧ, ОСТРОУМОВ БОРИС ВЛАДИМИРОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ПЕТРЕНКО ВАСИЛИЙ ИВАНОВИЧ

МПК / Метки

МПК: G05B 19/18

Метки: микропроцессорная, оборудованием, программного, технологическим

Опубликовано: 30.11.1989

Код ссылки

<a href="https://patents.su/12-1525678-mikroprocessornaya-sistema-dlya-programmnogo-upravleniya-tekhnologicheskim-oborudovaniem.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессорная система для программного управления технологическим оборудованием</a>

Предыдущий патент: Электропривод

Следующий патент: Устройство для управления процессом передачи сигналов управления в иерархической автоматизированной системе управления

Случайный патент: Шаговый искатель